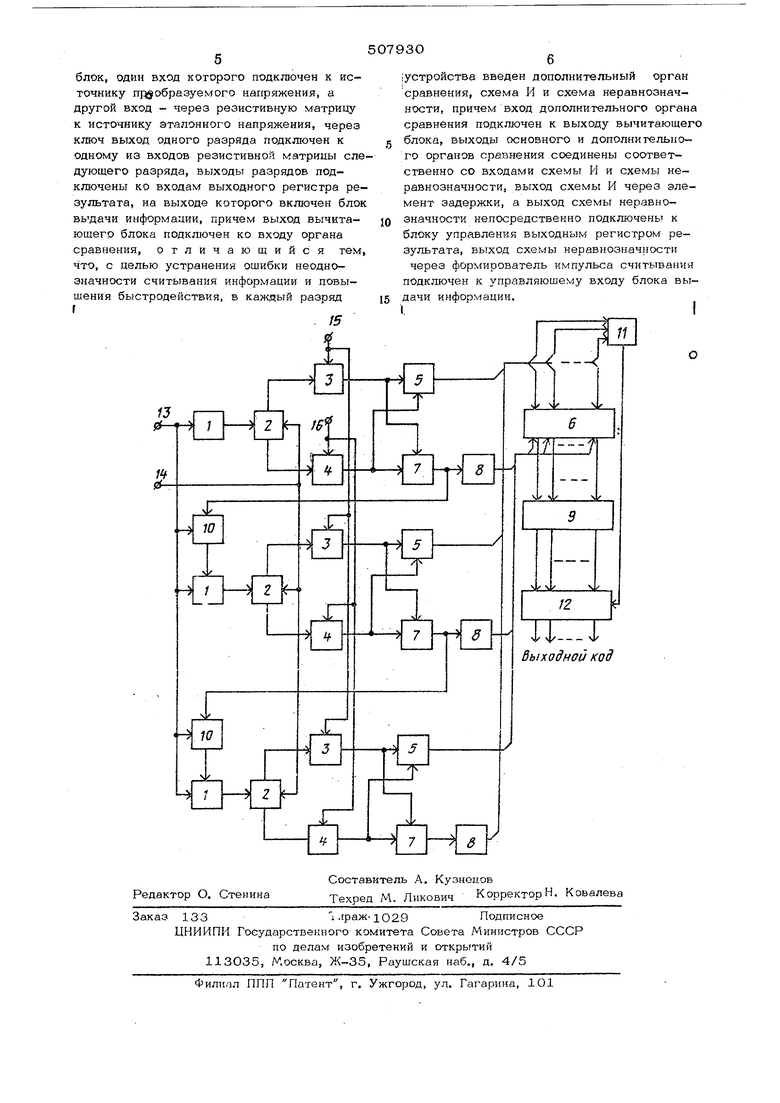

а выход cxeMbf неравнозначности непосред ственно подкгаочены к блоку управления выходным регистром результата, выход схемы неравнозначности через формирова тель импульса считывания подключен к упразляюшему входу блока выдачи информации. На чертеже дана блок-схема предлагаемого преобразователя. Устройство содержит резкстивную матрицу 1 типа вычитающий, блок 2, органы срааненчя 3 и 4; схему неравнозначности о, блок 6 управления выходным регистром результата; схему И 7, элемент задержки 8, выходкой регистр 9 результата; ключи 10; формирователь 11 импульсов считывания; блок 12 выдачи информации; шику 13, на которую подается эталонное напряжйние, шину 14, на ко торую подается преобразуемое напряжение шины 15 и 16j на которые подаются пороговые напряжения. Предлагаемый преобразователь напряжения в код работает следующим образом В исходном состоянии на выходах резистивных матриц 1 формируется опорное напряжение Uan., Равное соответственно 4 -. ...4 МАКС. МАКС. КАЙС. где тг -количество разрядов преобразователя, k номер разряда преобразователя. Ключи 10 находятся в разомкнутом состоянии. Выходное напряжение органов сравнения 3 и 4 соответствует логичесKovfy нулю. Выходной регистр результата обнулен. В момент подачи на шину 14 преобразуемого напряжения Н органы сравнения каждого k -го разряда сравнивают разностное напряжение (У. ), снимаемо с вычитающего блока 2, с пороговым напряжением U;,r) h -квант шкал преобразователя), подаваемым на шины 15 и 16. В случае если разностное напряжение (УХ - Uon)-f---- Ci) (где л. Un - ширина зоны неопределенности срабатывания органа сравнения), на выходе органов сравнения появляется напряжение, соответствующее уровню логической единицы. Если же (2), Ux-V к22 то выходное напряжение органов сравнени соответствует логическому нулю. В случае если разностное напряжение КйОн (х - onj г г х Иопк)ыходное напряжение органов сравнения ожет соответствовать с некоторой веротностью как логическому нулю, так и лоической единице. При наличии на выходах обоих органов сравнения fe -го порядка двух логических единиц, схема И 7 вырабатывает управляющий сигнал, который с помощью ключа 10 подключает эталонное напряжение подаваемое на шину 13, в старшие разряды матрицы последующих разрядов. В этом случае fe ый разряд выходного кода, равный единице, через элемент задержки 8 записывается с помощью блока управления 6 в соответствующий разряд выходного регистра. Если будет выполняться второе условие, го г -ый разряд выходного кода равен нулю, а ключ аналогового напряжения 10 подает в старшие разряды матриц последующих ступеней преобразования напряжение, равное нулю. Если преобразуемое напряжение И(таково, что выполняются третье и четвертое соотношения, то при появлении на выходе органа сравнения соответствующего разряда логической комбинации типа 1О на выходе схемы неоднозначности 5 появляется сигнал, записывающий с помощью блока управления 6 единицу в соответству-ющий разр5зд выходного регистра результата и нули во все младщие разряды. Кроме гого, блок управления 6 по этому сигна- лу блокирует возможность записи результатов преобразования в данном и младших разрядах, поступающих с соответствующих элементов задержки. Их постоянная времени должна быть такой, чтобы сигнал блокировки опережал сигналы, поступающие со схем И последующих младших разрядов. Сигналы со схем неоднозначности используются в блоке 11 формирования импульса считывания результата пре-. образования, подаваемого в схему выдачи информации. В случае если напряжение И. не попадает в зону неопределенности органов сравнения, считывание результата производится через фиксированные промежутки времени импульсом окончания преобразования, поступающим на блок выдачи информации в канал связи. Формула изобретения Преобразователь напряжения в код, содержащий в каждом разряде вычитающий

блок, один вход которого подключен к источнику nnsобразуемого напряжения, а другой вход - через резистивную матрицу к источнику эталонного напряжения, через ключ выход одного разряда подключен к одному из входов резистивной матрицы следующего разряда, выходы разрядов подключены ко входам выходного регистра результата, на выходе которого включен блок выдачи информации, причем выход вычитающего блока подключен ко входу органа сравнения, отличающийся тем, что, с целью устранения ошибки неоднозначности считывания информации и повышения быстродействия, в каждый разряд

f

/5

|устройства введен дополнительный орган сравнения, схема И и схема неравнозначности, причем вход дополнительного органа сравнения подключен к выходу вычитающег блока, выходы основного и дополнительного органов сравнения соединены соответственно со входами схемы И и схемы неравнозначности, выход схемы И через элемент задержки, а выход схемы неравнозначности непосредственно подключены к блоку управления выходным регистром результата, выход схемы неравнозначности

через формирователь импульса считывари1Я подключен к управляющему входу блока выдачи информации.

/f

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь напряжения в код | 1978 |

|

SU739734A1 |

| СЛЕДЯЩИЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1989 |

|

RU2028731C1 |

| Многоканальный аналого-цифровой преобразователь | 1982 |

|

SU1040599A1 |

| Запоминающее устройство с самоконтролем | 1982 |

|

SU1061176A1 |

| Преобразователь активной мощностиВ КОличЕСТВО иМпульСОВ | 1979 |

|

SU845109A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 2000 |

|

RU2171543C1 |

| Аналого-цифровой преобразователь поразрядного кодирования | 1976 |

|

SU657607A1 |

| Аналого-цифровой преобразователь | 1980 |

|

SU938396A1 |

| Следящий аналого-цифровой преобразователь | 1983 |

|

SU1181116A1 |

| Многоканальный преобразователь кода в напряжение | 1985 |

|

SU1279071A1 |

Авторы

Даты

1976-03-25—Публикация

1974-10-07—Подача