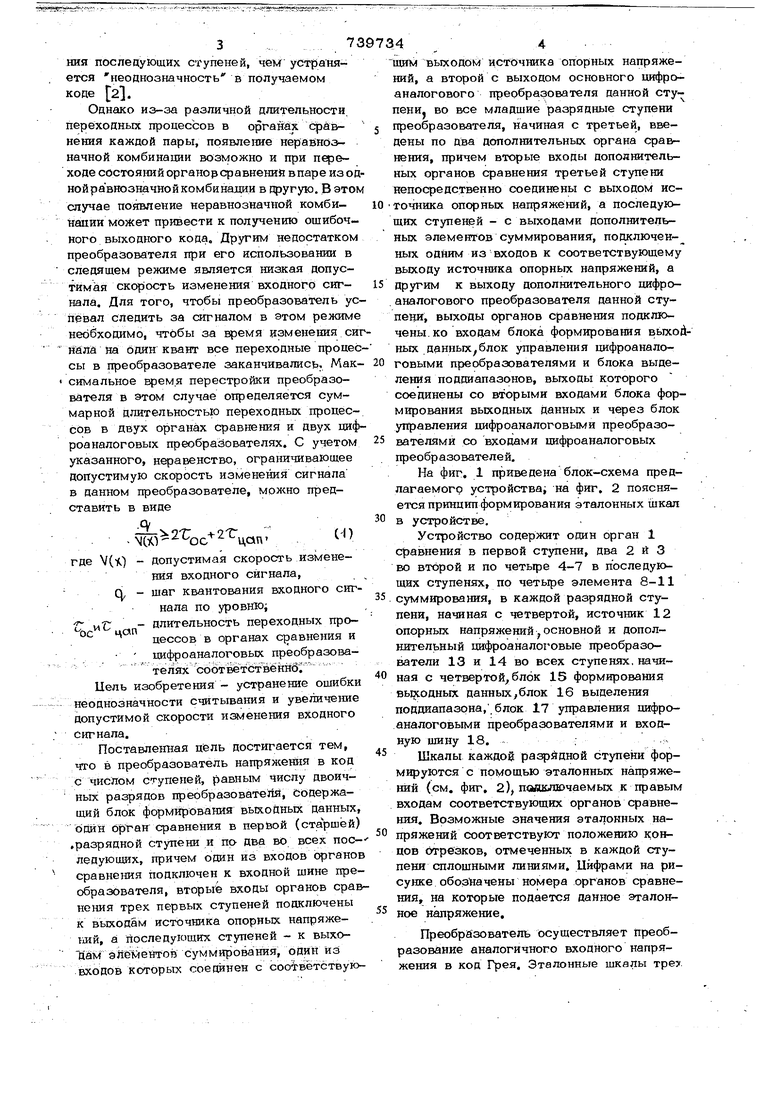

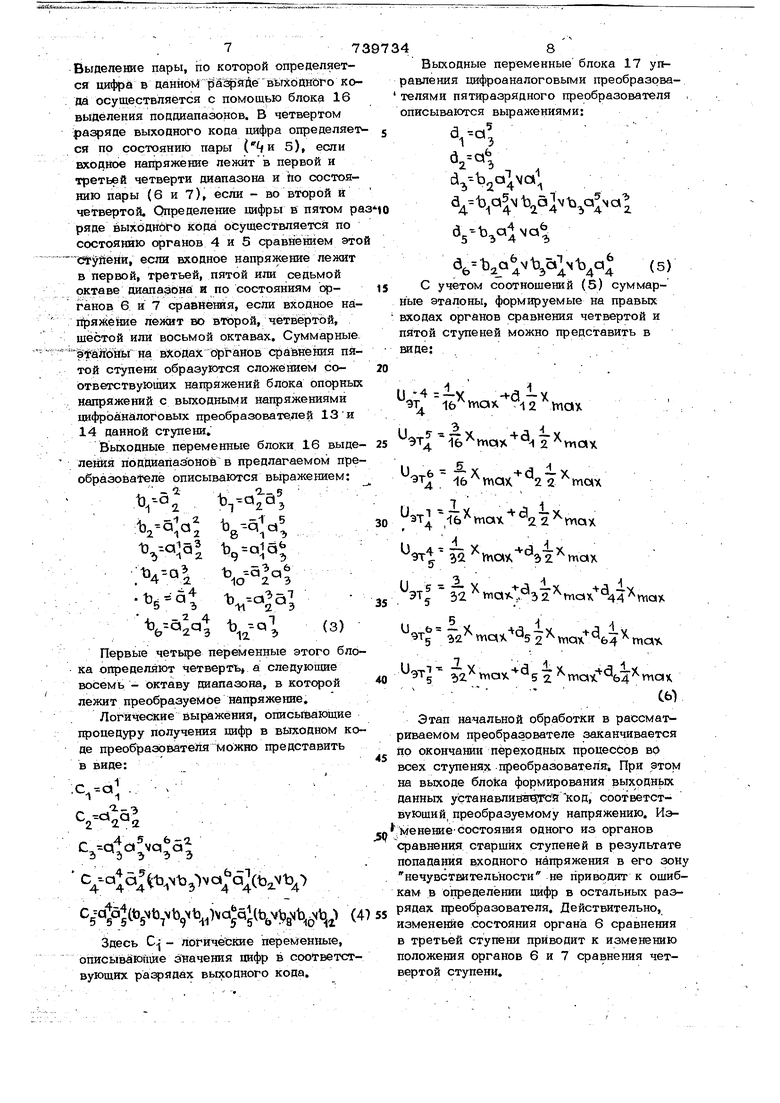

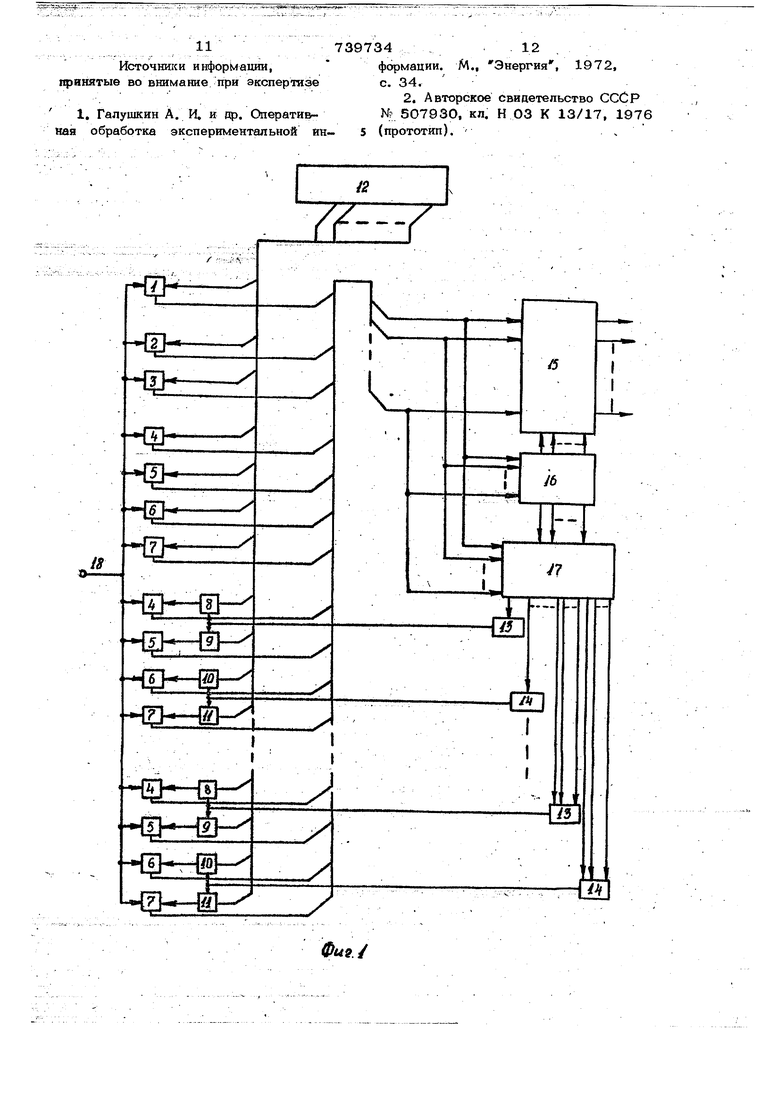

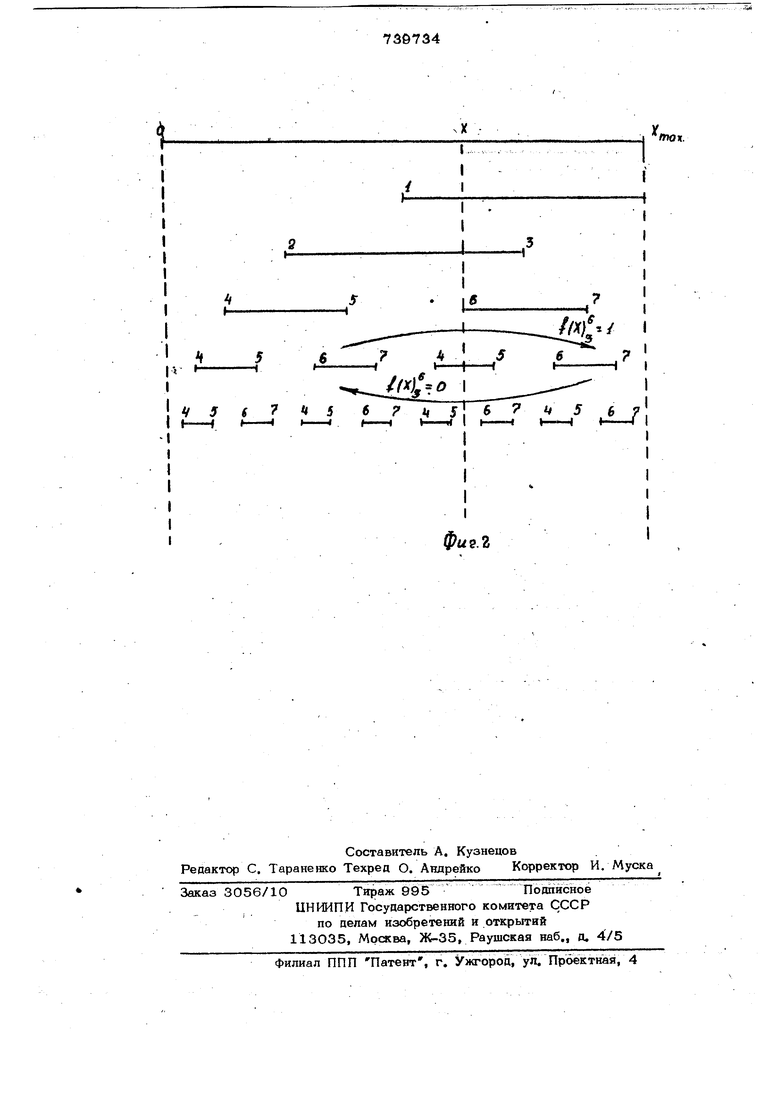

(54) ПРЕОБРАЗОВАТЕЛЬ НАПРЯЖЕНИЯ В КОД .I ПреДпагаемое изобретение относится I к вычислительной технике и быть использовано в контрольно-измерительньк системах различного назначения. Известна структура асинхронного нреОбразования, состоящая из и ступеней, где м -число разрядов преобразова.теля, каждая из которых включает в себя орга Оравнения и цифроаналоговый преобразователь, управляемый с выходов органов срайнёшя предыдущих ступеней 1 . .- Существенным недостатком указанных структур является возможность возникновения ошибки неоднозначности счи тывания, которая может достигать 50% от диапазона измеряемой величины. Причинойуказанной ошибки является наличие в характеристиках органов сравнения зоны нечувствительности, где они могут с н& которой вероятностью находиться как в еди шчном, так и в нулевом состоянии. Соответственно изменяются и состояния органов сравнения последующих младших ступеней. Код, снимаемый в этот момент с преобразователя, может значительно отличаться от истинного. Известен преобразователь, включающий в себя блок формирования выходных аанньгх, по цва оргапа сравнения и по одному Цифроаналоговому преобразователю в каждой разрядной ступени, причем выходы Нифроаналоговых преобразователей через элементы суммирования, вторые входы которых соединены с источником опорных напряжений, подключень ко входам органов сравнения соответствующей ступени. Использование в каждой разрядной ступени преобразователя двух органов сравнения позволяет существенно снизить вероятность возникновения ошибки неоднозначности. При значениях входного сигнала близких к величине эталонного , напряжения оДной из ступеней возможно появление нерабнозначной комбинации на выходах соответствующей пары органов сравнения. В этом случае выходной код формируется независимо от состояния органов сравнения поспедующих ступеней, чем устраняется неоднозначность в получаемом коде 2. Однако из-за различной длительности переходных процессов в органах сра&нения каждой пары, появление неравнозначной комбинации возможно и при переходе состоянийорганорсравнений впареизод нойравнозначной комбинации в другую. В этом случае по твление неравнозначной комбинации может привести к получению ошибочного выходного кода. Другим недостатком преобразователя при его использовании в следящем режиме является низкая допустимая скорость изменения входного сигнала. Для того, чтобы преобразователь ус певал следить за сигналом в этом режиме необходимо, чтобы за время изменения си Нала на один Квант все переходные проиес сы в преобразователе заканчивались. Максимальное время перестройки преобразователя в этом случае определяется суммарной длительностью переходных продессов в двух органах сравнения и двух циф роаналоговых преобразователях. С учетом указанного, неравенство, ограничивающее допустимую скорость изменения сигнала в данном преобразователе, можно представить в виде где V(4k) допустимая скорость изменения входного сигнала, (V - шаг квантования входного сигнала по уровню - длительность переходных процессов в органах сравнения и цифроаналоговых преобразователях собтБетствёНнб АСЛЯЛ 1 О .. Цель изобретения - устранение ошибки неоднозначности считывания и увеличение допустимой скорости изменения входного сигнала.. Поставленная цель достигается тем, что в преобразователь напряжегаш в код с числом ступеней, равным числу двоич ных разрядов преобразователя, содержащий блок формирования выходных данных, ОДИН орган сравнения в первой (старшей) и {JJfl jn. tJ I с n LJCA .ЛА-1АJJ Ai. .разрядной ступени и по два во всех последующих, причем один из входов органов сравнения подключен к входной шине преобразователя, вторые входы органов срав нения трех первых ступеней подключены к выходам источника опорных напряжений, а последующих ступеней - к выхо дам 9йе1йейтов суммирования, оДий из входов которых соединен с соответствуюшим выходом источника опорных напряжений, а второй с выходом основного цифроаналогового преобразователя данной стуneHHj во все младшие разрядные ступени преобразователя, начиная с третьей, введены по Два дополнительных органа сравнения, причем вторые входы дополкительных органов сравнения третьей ступени непосредственно соединены с выходом источника опорных напряжений, а последующих ступеней - с выходами дополнительных элементов суммирования, подключенных одним из входов к соответствующему выходу источника опорных напряжений, а другим к выходу дополнительного цифроаналогового преобразователя данной ступевд1, выходы органов сравнения подключены, ко входам блока формирования выхойных данных,блок управления цифроаналоговыми преобразователями и блока выделенйя поддиапазонов, выходы которого соединены со вторыми входами блока формирования выходных Данных и через блок управления цифроаналоговыми преобразователями со входами цифроаналоговых преобразователей. На фиг. 1 приведена блок-схема предлагаемого устройства на фиг. 2 поясняется принцип формирования эталонных шкал в устройстве. Устройство содержит один орган 1 сра)энения в первой ступени, два 2 и 3 во второй и по четыре 4-7 в последующих ступенях, по четыре элемента 8-11 суммирования, в каждой разрядной ступеня, начиная с четвертой, источник 12 опорных напряжений, основной и дополнительный цифроаналоговые преобразователи 13 и 14 во всех ступенях, начи. -J1 ная с четвертой,блок 15 формирования выходных данных,блок 16 выделения поддиапазона, блок 17 управления цифроаналоговыми преобразователями и входную шину 18. .;.;. Шкалы каждой рафйдной ступени формируются с помощью эталонных напряжений (см. фиг. 2), подключаемых к правым входам соответствующих органов сравнения. Возможные значения эталонных напряжений соответствуют положению конпов отрезков, отмеченных в каждой сту пеня сплошными линиями. Цифрами на рисунке номера органов сравнения, на которые подается данное эталонное напряжение. Преобразователь осуществляет преобразование аналогичного входного напряжения в код Грея. Эталонные шкалы тре. старших {зазрядных ступеней образуются путем подключения эталонного напряжения ко входу органа 1 сравнения, 1/4 . 3/4 vriax o входам органов 2 и 3 сравнения и напряжений e- vnavl max-f mF WOTL ко входам органов 4-7 сравнения третьей ступени соот ветственно. Эти напряжения образуют пос тоянные шкалы трех старших ступеней преобразователя. Напряжения, подавае; мые на правые входы органов сравнения этих ступеней, не меняются в течение всего времени работы преобразователя. Начальные напряжения, подаваемые на входы органов 4-7 сравнения последующих младших разрядных ступеней уста-навливаются равными; |г так4тач ,. порядковой номер разрядной ступени, считагя состаршей.Этинапряженияобеспечивают формирование эталонных шкал, расположенны в левых частях диапазона (фиг. 2). В исходном-состоянии преобразуемое напряжение отключено от входной шины преобразоватепя. При этом все органы сравнения находятся в нулевом состоянии и напряжения на выходах цифроаналоговых преобразователей 13 и 14 равны нулю. При подключении преобразуемого напряжения к входной шине преобразователя состоянйе органов сравнения изменяется в соответствии с выражением: пр«, ,H) пь п - эт -231-1 2 (2 где fU) -функция, реализуемая . 3-ым органом сравнения i-ой ступени, U 571-%. , эталонное напряжение, подаваемое на правый вход этого органа сравнения; С -ширина зоны нечувствительностиорганов сравнения ()-,),Ptf)- условные верюятности появления единицы и нуля на выходе органа сравнения при заданном X соответственно. Обозначаем логическую переменную, опи сывающую состояние данного органа сравнения через : Рассматриваем работу преобразования на примере кодирования входного напряжения, равного 5/8 пятиразрядным преобразователем данного типа. При под-ключении этого напряжения к входной щине преобразователя органы 1 и 2 сравнения двух первых ступеней, 4 и 5 третьей ступени и все органы сравнения младшизс ступеней переходят в единичное сос1ЕЧ5янив, Поскольку входное напряжение находитсяс в зоне нечувствительности органа 6 сравнения третьей ступени, то состояние этого органа сравнения может принимать как единичное, так и нулевое значение. По состоянию органов сравнения трех старших ступеней формируются суммарные эталонные напряжения на правьйс входах органов сравнения четвертой ступени. Эти напряжения образуются путем суммирования эталонных напряжений .блока 12 Ъпорных напряжений и выходных напряжений щфроаналоговых преобразователей 13 и 14. формирование суммарных эталонов на входах органов сравнения ступени осуществляется следующим образом. Бели входное напряжетше Ъ ,(4-иг лёяит 6 идаервале ,%.„„ L тм т«к, то на выходе цифроаналрговогопреобразователя 13 четвертой ступени формируется напряжение, равное эталонные напряжения органов 4 и 5 сравнения устанавливаются симметрично относительно напряжения 5/8 (фиг. 2). Такое же напряжение l/2Xwvoni.°®P y® выходе цифроанапогового преобразователя 14 этой ступени, еслиКв -|х о, При этом а I 1 .В противном случае выходное напряжение Щ1фроаналогового преобразователя 14 равно нулю.. . Таким образом, при изменении состояния органа сравнения в третьей ступени на противоположное пара органов (б и 7) Р ьнения четвертой сту.пени изменяет свое положение, а пара (4 и 5) положе- . шя не Меняет. Определение диапазона, в котором лежит преобразуемое .напряжение и формирование сигнала управления нифроаналоговыми преобразователями осуохествляется с помощью блока 16 выделения, поддиапазонов и блока 17 управления вдфроаналоговыми преобразователями. Логика блока 15 формирования выходных данных обеспечивает участие в формировании цифры в данном разряде выходного кода только той пары, которая не меняет своего положения при изменении состояния одного из органов сравнения старших ступеней. В формировании цифры в четвертом разряде выходного кода в рассматриваемом примере участвует пара (4 и 5), а пара (6 и 7) в формировании этой цифры участия не принимает. 77397 Выделение пары, по которой определяется цифра в даннок 1раё1{эййе выходного кода осуществляется с помощью блока 16 выделения поддиапазонов. В четвертом разряде выходного кода цифра определяет 5 ся по состоянию пары (и 5), если входное напряжение лежит в первой и третьей четверти диапазона и ho состоянию пары (б и 7), если - во второй и четвертой. Определение цифры в пятом ряде выходного коде осуществляетсй по состоянию органов 4 и 5 сравнением этой сЯруйбНи, если входное напряжение лежит в первой, третьей, пятой или седьмой октаве диапад1Ьнй и по состояниям ор- 15 ганов 6 и 7 сравйения, если входное напряжение лежит во второй, четвёртой, шестой или восьмой октавах. Суммарные. на входах Органов ера вне щя пятой ступени образуются сложе йием со- 20 Ответствующих напряжений блока Опорных . напряжений с выходными напряжениями цифроанйлоговых преобразователей 13и 14 данной ступени. Выходные переменные блоки 16 выде- 25 леййя поддиапазонов в предлагаемом преобразователе описываются выражением:

(3)

Первые четыре переменные этого блока определяют четверть, а следующие восемь - октаву диапазона, в которой лежит преобразуемое напряжение.

Логические выражения, описы1вающие процедуру получения цифр в выходном коде преобразОватёйя можно представить в виде:

.«4-5

ь-г

.V C.,.vb , vb«Mb Nto (4755 э 5 & э 7 9 -ti 5 5 О . а чо -(Z Здесь С| - логические переменные, описываюйще значения цифр в соответствующих разрядах выходного кода. зо

. I ; 3-

ix

ЭТ 32 nay.t.

44 П1С111(.

-I

ч

.

0,2 max

у i К Ч.Я 1.к 5,2. 2 (,

(bV

Этап начальной обработки в рассматриваемом преобразователе заканчивается

по окончании переходных процессов во всех ступенях преобразователя, При этом на выходе блока формирования выхрдн|з1Х данных устанавлива С:Якод, соответствующий, преобразуемому напряжению, Иэ -менение-состояния одного из органов сравнения старших ступеней в результате попадания входного напряжения в его зону нечувствительности не приводит к ошибкам в определении цифр в остальных раз48Вьиодные переменные блока 17 управления цифроаналоговыми преобразрвателями пятиразрядного преобразователя описываются выражениями: а at (5) С учетом соотношений (5) суммарные эталоны, формируемые на правых входах органов сравнения четвертой и пятой ступеней можно представить в шде: II -4 - - Y 9т 12 mail и А - так i . 6 16 max ё may. преобразователя. Действительно, изменение состояния органа 6 сравнения в третьей ступени приводит к изменению положения органов 6 и 7 сравнения четвертой ступени. 9 Однако поскольку в формировании 1щфр В данном разряде участвует только;пара (4 и 5). то изменение положения пары (6 и 7) не влияет на цифр у в этом разряде выходного кода. Изменения положешш органов сравнения в nocrteдующих ступенях преобразователя вообще не происходит. Следовательно, и цифры в вы- - ходном коде, форм.ируемые этими ступенями, не меняются. Таким образом, иэг менение состояния органа 6 сравнения в третьей ступени прИ аОйит к изменЬнию иифы лишь в одном: Т{)бтьем разряде преобразователя. При этЬЙ охсибка цифрового представления не npeSbiti lieT едивицы младшего разряда.; Проведенный анализ процесса преобразования показывает, что максимальная величина ошибки неоднозначностя в предлагаемом преобразователе снижена по сравнению с известными асинхронными преобразователями с величины х уго до величины, не превышающей кванта. Эт существенно расширяет области применения асинхронных преобразователей в различных системах обработки быстроменяк щихся процессов. Кроме того, введенные изменения позволяют повысить допустимую скорость изменения сигнала в следящем режиме. Это обеспечивается тем, что одна из пар органов сравнения, не участвующая в данный момент в формировании выходного кода, следит за изменением, входного напряжения. При этом к моменту, когда блок выделения поддиапазонов вырабатывает команду на смену пары, формирующей .цифру в данном разряде выходного кода, все переходные про цессы в этой паре заканчиваются. В этом случае время, затрачиваемое на фор мирование нового выходного кода, опре.деляется только длительностью переходных процессов в органе сравнения и логической части преобразователя. Время же обработки, сигнала всеми ступенями преобразователя определяется суммарной длительностью переходных процессов в двух органах сравнения и одном цифроаналоговом преобразователе. Для того, чтобы ошибка цифрового представления не превысила единицы младшего разряда необходимо, чтобы входное напряжение изменилось за это время не более, чем на 3. Неравенство, ограничивающее допустимую cKoJDocTb изменения сигнала, в этом случае можно представить в виде: 2Г Г NjUr ОС, цап(7) 73410 СравнеЕше результатов аналитического расчета гфедельно допустимых скоростей измене я контролируемых процессов, проведенное на основании неравенств (1) и (7),показывает, что введенные нзменешя позволяют не менее чем в три раза i увегасчить i- допустимую скорость изменения сводного сигнала в предлагаемом преобразователе по сравнению с известными. Это позволяет использовать пред- . лагаемый преобразователь для представления более быстрых процессов. Формула изобретения Преобразователь напряжения: в код счислом ст;ут1бней равным числу двоичных разрядов преобразователя, содержащий блок формирования выходных данных один орган сравнения в первой (старшей) разрядной ступени и по два во всех последуЮших, причем один из входов органов сравнения подключен к входной шине преобразователя, вторые входы органов сравнения трех первых ступеней подключены к выходам источника опорных напряжений, . а последующих ступеней к выходам йлементов суммирования, один из входов которых соединен с соответствующим выходом источника опорных Напряжений, а второй с выходом основного цифроаналогового преобразователя данной ступени, отличающийся тем, что, с целью устранения ошибки неоднозначности считывания и увеличения допустимой скорости изменения входного сигнала, во все младшие разрядные ступени преобразователя, начиная с третьей, введены по два дополнительных органа сравнения, причем BTOptie входы дополнительных органов сравнения третьей ступени непосредственно соединены с выходом источника опорных напряжений, а последующих ступеней - с выходами дополнительных элементов суммирования, подключенньпс одним из вх.одов к соответствующему выходу источника опорных напряжений, а другим к выходу дополнительного цифроаналогового преобразователя данной ступени, выходы органов сравнения подключены ко входам блока формирования выходных данных, блок управления цифроаналоговыми преобразователями и блока выделения поддиапазонов, выходы которого соединены со вторыми входами блока формирования выходных данных и через блок управления пифроаналоговыми преобразователями со входами пифроаналоговых преобразователей.

739734 ,12 ,

Источники информации, принятые во внимание при экспертизе

1, Галушкин А. И, и Щ). Оперативная обработка экспериментальной йн- 5 (прототип).

формации. М., Энергия, 1972, с. 34.

2. Авторское свидетепьство СССР N 507930, кл. Н 03 К 13/17, 1976

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь напряжения в код | 1980 |

|

SU961135A1 |

| Устройство для измерения погрешности цифро-аналоговых преобразователей | 1982 |

|

SU1112546A1 |

| Регулятор | 1984 |

|

SU1260913A1 |

| Устройство для сопряжения ЦВМ с аналоговыми объектами | 1983 |

|

SU1130856A1 |

| Преобразователь напряжения в код | 1974 |

|

SU507930A1 |

| Параллельно-последовательный аналого-цифровой преобразователь | 1980 |

|

SU995313A1 |

| Последовательно-параллельный аналого- цифровой преобразователь | 1978 |

|

SU743193A1 |

| Управляемый генератор ступенчатого напряжения | 1983 |

|

SU1095368A1 |

| Цифроаналоговый преобразователь | 1984 |

|

SU1216829A1 |

| Аналого-цифровой преобразователь | 1984 |

|

SU1368990A1 |

(Фиг. / Y

mox.

VJ f7 ц 51 6 5 6 7

фи.г

Авторы

Даты

1980-06-05—Публикация

1978-01-16—Подача