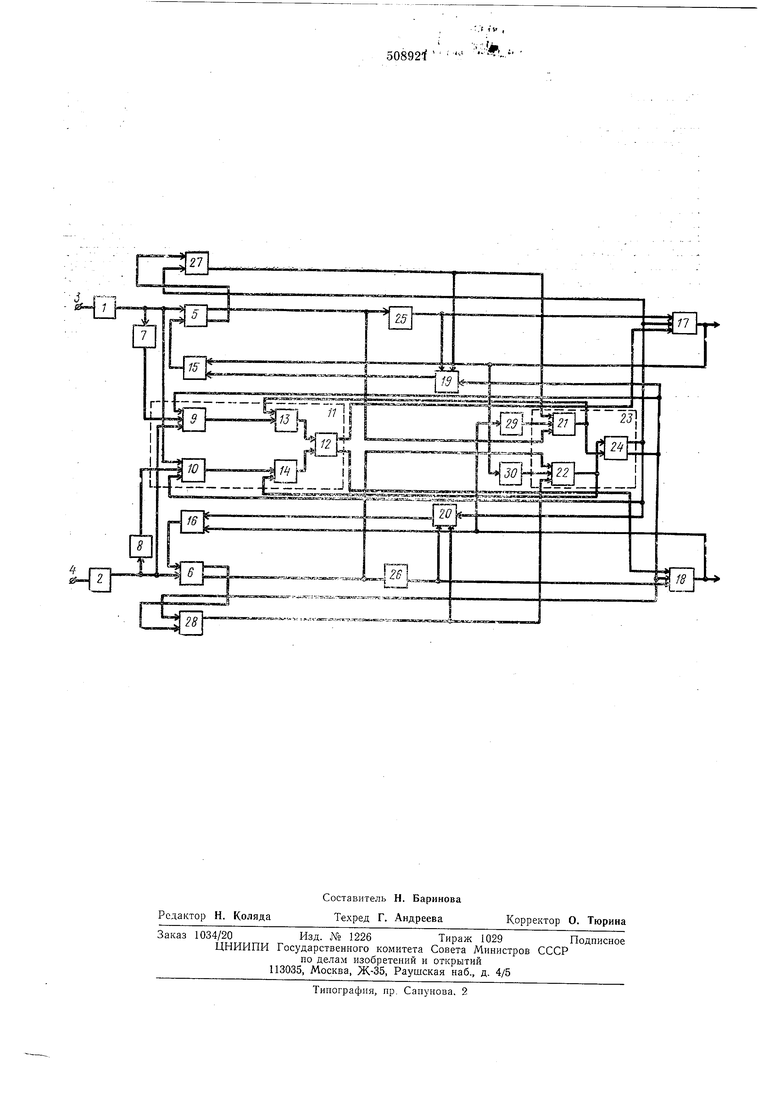

го триггер 12 блока запрета 11, к первому входу которого через элемент ИЛИ 13 блока запрета 11 подключен выход элемента И 9, а ко второму входу через элемент ИЛИ 14 блока запрета 11 -выход элемента И 10. Вторые входы элементов И 9 и 10 блока запрета 11 соединены с выходами формирователей 2 второго канала и 1 первого канала, соответственно.

Вторые входы триггеров памяти 5, 6 соединены с выходами дополнительных элементов ИЛИ 15, 16, первые входы которых подключены к выходам элементов совпадения 17, 18 первого и второго каналов, а вторые их входы- к выходам элементов И 19 и 20 первого и второго каналов. Первые выходы триггеров памяти 5, 6 соединены непосредственно с первыми входами элементов И 21, 22 блока заноминания 23, содержащего триггер 24 блока запоминания 23, первый вход которого подключен к выходу элемента И 22, а второй- к выходу элемента И 21, а через инверторы 25, 26 1первые выходы триггеров памяти 5, 6 первого и второго .канала соединены с первыми входами элементов И 19 первого и 20 второго каналов и первыми входами элементов совладения 17, 18.

Вторые выходы триггеров памяти 5, 6 первого и второго каналов соединены с первыми входами дополнительных триггеров 27, 28, выходы которых подключены к третьим входам элементов И 19, 20 первого и второго каналов и вторым входам элементов И 21, 22 блока запоминания 23. Первый и второй выходы триггера 12 блока запрета И соединены со вторыми входами элементов совпадения 17 и 18 первого и второго каналов, соответственно. Выходы элементов совпадения 18 и 17 подключены, соответственно, через дополнительные инверторы 29 и 30 к третьим входам элементов И 21 и 22 блока запоминания 23, выходы которых соединены с вторыми входами элементов ИЛИ 13 и 14, соответственно, блока запрета 11.

Первый выход триггера 24 блока запоминания 23 подключен к второму входу дополнительного триггера 27, третьему входу элемента совпадения 17, третьему входу элемента И 10 блока запрета 11 и второму входу элсме1гта И 20 второго канала, а второй выход - к второму входу дополнительного триггера 28, третьему входу элемента совпадения 18, третьему входу элемента И 9 блока запрета 11 и второму входу элемента И 19 первого канала. Устройство для получения разностной частоты двух импульсных последовательностей работает следующим образом.

В исходном состоянии триггеры памяти 5, 6 и дополнительные триггеры 27, 28 находятся в нулевом состоянии, на первом выходе триггера 12 блока запрета 11 и втором выходе триггера 24 блока запоминания 21 имеется разрешающий потенциал, а на втором выходе триггера 12 блока запрета 11 и первом выходе триггера 24 блока запоминания 21 -

запрещающий потенциал. На третьих входах элементов И 21, 22 имеется разрещающий потенциал, подаваемый с выходов дополнительных инверторов 29, 30.

5 При поступлении от первого источника входного сигнала на клемму 3 первого канала сигнала формирователь 1 выдает импульс положительной полярности, под воздействием которого элементы схемы изменяют свои состоя10 ния. Эти изменения происходят таким образом, что по окончании импульса формирователя 1 (по заднему фронту этого импульса) триггер памяти 5 устанавливается в исходное (нулевое) состояние, а другие элементы уст15 ройства устанавливаются в следующие состояния: на втором входе элемента И 20, первом входе элемента И 10 и третьем входе элемента совпадения 17 первого канала имеется разрещающий потенциал, подаваемый с первого 0 выхода триггера 24, а на втором входе элемента И 19, первом входе элемента И 9 и втором входе элемента совпадения 18 второго канала имеется запрещающий потенциал, подаваемый со второго выхода триггера 24. С первого вы5 хода триггера 12 подается запрещающий потенциал на второй вход элемента совпадения 17, а со второго выхода триггера 12 подается разрешающий потенциал на второй вход элемента совпадения 18.

0 При поступлении импульса от второго источника входного сигнала на клемму 4 второго канала формирователь 2 выдает положительный импульс, под воздействием которого элементы схемы соответствующим образом изменяют свои состояния. По окончании импульса формирователя 2 (по заднему фронту этого импульса) триггер памяти 6 переходит В исходное состояние и схема устанавливается в следующее состояние: на втором входе элемента И 19, первом входе элемента И 9 и третьем входе элемента совпадения 18 имеется разрешающий потенциал, подаваемый со второго выхода триггера 24, а на втором входе элемента И 20, первом входе элемента И 10 5 и третьем входе элемента совпадения 17 первого канала имеется запре цающий , подаваемый с первого выхода триггера 24. Со второго выхода триггера 12 подается запрещаюн|ий потенцнал на второй вход элемента сов0 падс1 ия 18, а с первого выхода триггера 12 подается разрешаюни-1Й потенциал на второй вход элемента совпадения 17.

С приходом второго сигнала на входную клемму 4 второго канала от второго источника 5 входного сигнала формирователь 2 выдает еще один положительный импульс, под воздействием которого элементы схемы срабатывают таким образом, что на выходе элемента совпадения 18 появляется импульс, равный по дли0 тельности импульсу формирователя 2. С приходом каждого следующего сигнала на вход второго канала - клемму 4 второго источника входного сигнала (при отсутствии сигналов на входе первого канала - клемме 3 перво5 го источника входного сигнала) на выходе элемента совпадения 18 соответственно будут появляться импульсы, равные по длительности импульсам формирователя 2.

При поступлении на клеммы 3 и 4 источников входных сигналов первого и второго каналов двух импульсных последовательностей с разными частотами на выходе соответствую.щего элемента совпадения 18 или 17 появляются импульсы разностной частоты. А именно, если частота импульсной последовательности, поступающей на клемму 3 источника входного сигнала первого канала, больше частоты импульсной последовательности, поступающей на клемму 4 источника входного сигнала второго канала, то импульсы разностной частоты будут появляться на выходе элемента совпадения 17 первого канала, а в противоположном случае - на выходе элемента совпадения 18 второго канала.

При близких частотах импульсных последовательностей, поступающих на клеммы 3, 4 источников входных сигналов первого и второго каналов, происходит частичное или полное перекрытие импульсов, формируемых формирователями 1 и 2. При частичном перекрытии последних и, если импульс формирователя 1 опережает импульс формирователя 2, по окончании импульса формирователя 1 схема устанавливается в состояние, соответствующее прохождению импульса по первому каналу, а по окончании импульса формирователя 2 - в состояние, соответствующее прохождению импульса по второму каналу. У налогично срабатывает схема и в случае, когда импульс формирователя 1 отстает от импульса формирователя 2 при частичном перекрытии формируемых ими импульсов.

При выдаче формирователями 1 и 2 импульсов-, полностью перекрывающихся во времени, то есть когда отстаюн1ий импульс (передний фронт начинается позже) зака 1чивается раньше опережающего импульса (передний фронт начинается раньше) аюсле окончания импульса формирователя, выдавшего опережающий имПульс, произойдет установка схемы в состояние, соответствующее прошедшему отстающему Имлульсу.

Формула изобретения

Устройство для иолуче.;ия разностной частоты двух импульсных последовательностей, имеющее два канала, каждый из которых содержит формирователь, вход которого подключен к источнику входного сигнала, а выход - через элементы И и ИЛИ к одному входу триггера блока запрета, и через инвертор, другие элементы И и ИЛИ - ко второму входу триггера блока запрета и ко входу триггера памяти, выход которого соединен со входом элемента И блока запоминания, выход которого подсоединен ко входу триггера блока запоминания и к другому входу элемента

ИЛИ блока запрета, а через инвертор соединен со входом элемента совпадения, другой вход которого подключен к выходу триггера блока запрета, и со входом элемента И канала, отличающееся тем, что, с целью повышения разрешающей способности и расширения частотного диапазона работы, в каждый канал введены элемент ИЛИ, дополнительный инвертор и дополнительный триггер, один вход которого подключен к второму выходу

триггера памяти, другой вход соединен с выходом триггера блока запоминания, третьим входом элемента совпадения, третьим входом элемента И блока запрета и вторым входом элемента И другого канала, а выход соедииен со вторым входом элемента И блока запоминания и третьим входом элемента И канала, выход которого подключеи ко входу упомянутого дополнительного элемента ИЛИ, выход которого соединен со

вторым входом триггера памяти, а другой вход подключен к выходу элемента совпадения и ко входу упомянутого дополнительного инвертора, выход которого подключен к третьему входу элемента И блока запоминания.

, t iv ,

.I)M .

508Q2i

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для измерения расстояния между центрами интерференционных полос интерферограмм | 1988 |

|

SU1677877A1 |

| Устройство для формирования команд телеуправления | 1986 |

|

SU1399796A1 |

| Двухканальное устройство для сопряжения двух электронно-вычислительных машин | 1989 |

|

SU1647581A2 |

| Устройство для допускового контроля длительности временных интервалов | 1976 |

|

SU657404A1 |

| Устройство для управления шаговым двигателем | 1977 |

|

SU663058A1 |

| Устройство для защиты и автоматического отключения потребителя | 1985 |

|

SU1339722A1 |

| Распределитель импульсов | 1980 |

|

SU919085A2 |

| Каскад программируемого делителя частоты | 1980 |

|

SU919091A1 |

| Устройство для сжатия цифровых телевизионных сигналов цветного изображения | 1988 |

|

SU1529471A1 |

| Резервированный делитель частоты сле-дОВАНия иМпульСОВ | 1979 |

|

SU805496A2 |

чз

Авторы

Даты

1976-03-30—Публикация

1974-06-26—Подача