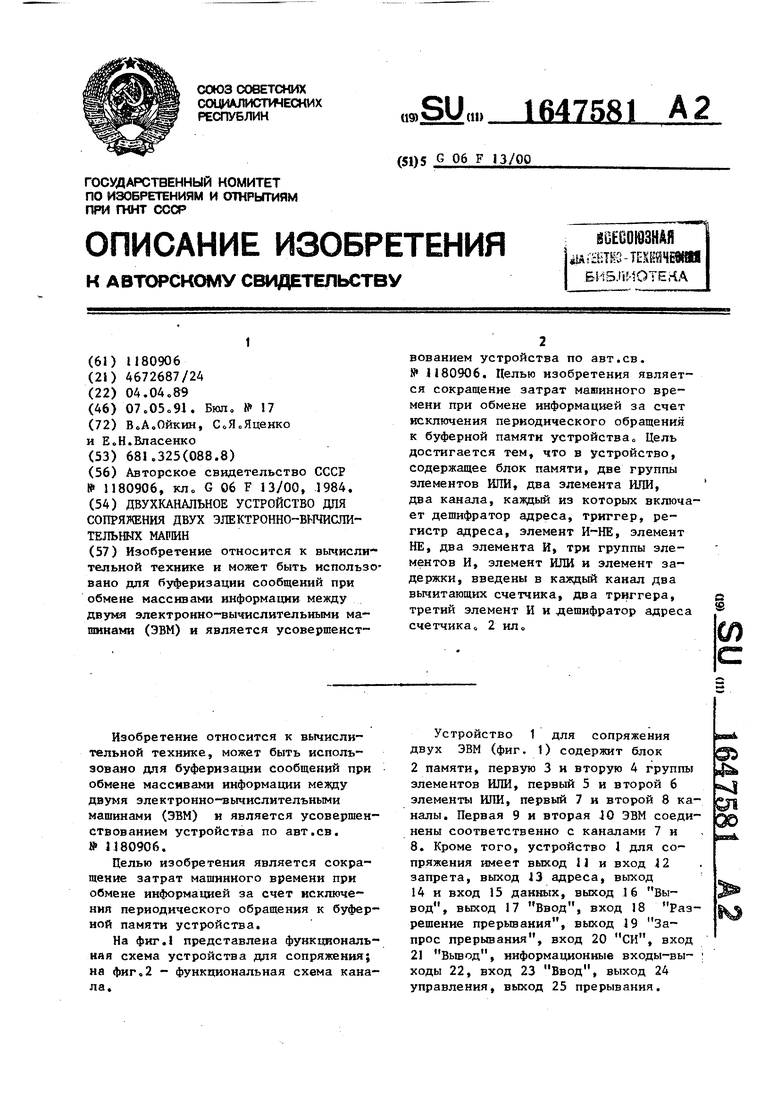

Изобретение относится к вычислительной технике, может быть использовано для буферизации сообщений при обмене массивами информации между двумя электронно-вычислительными машинами (ЭВМ) н является усовершенствованием устройства по авт.св. 11 80906.

Целью изобретения является сокращение затрат машинного времени при обмене информацией за счет исключения периодического обращения к буферной памяти устройства.

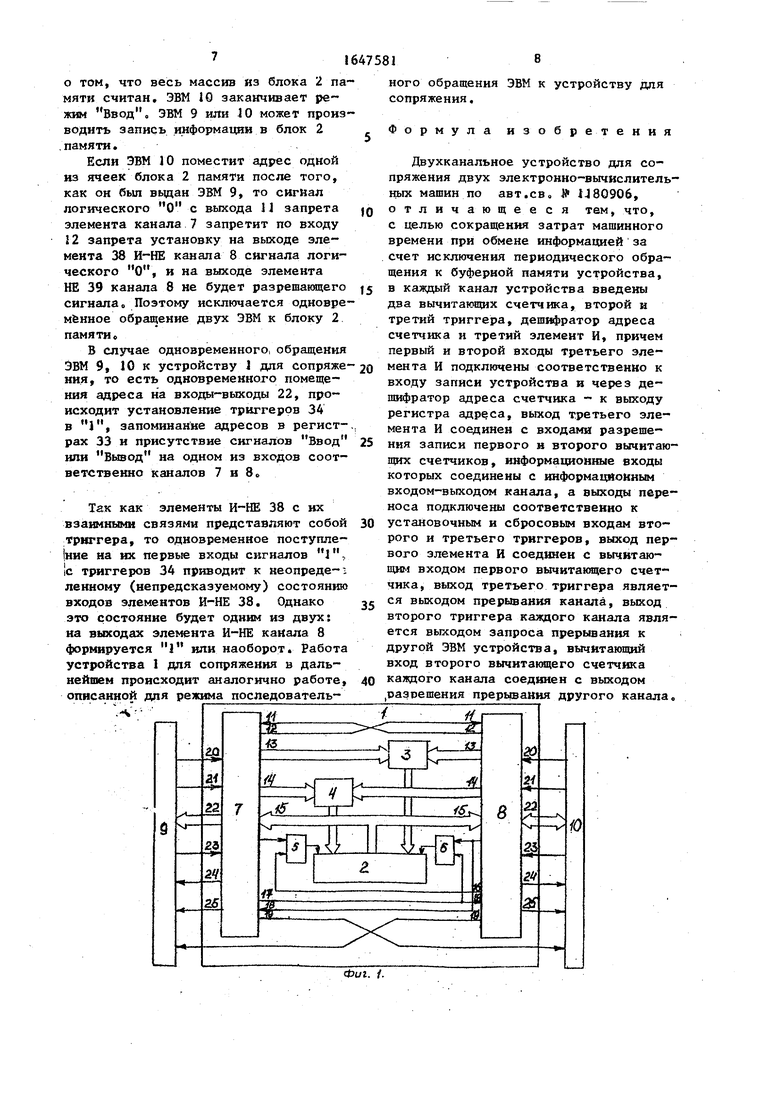

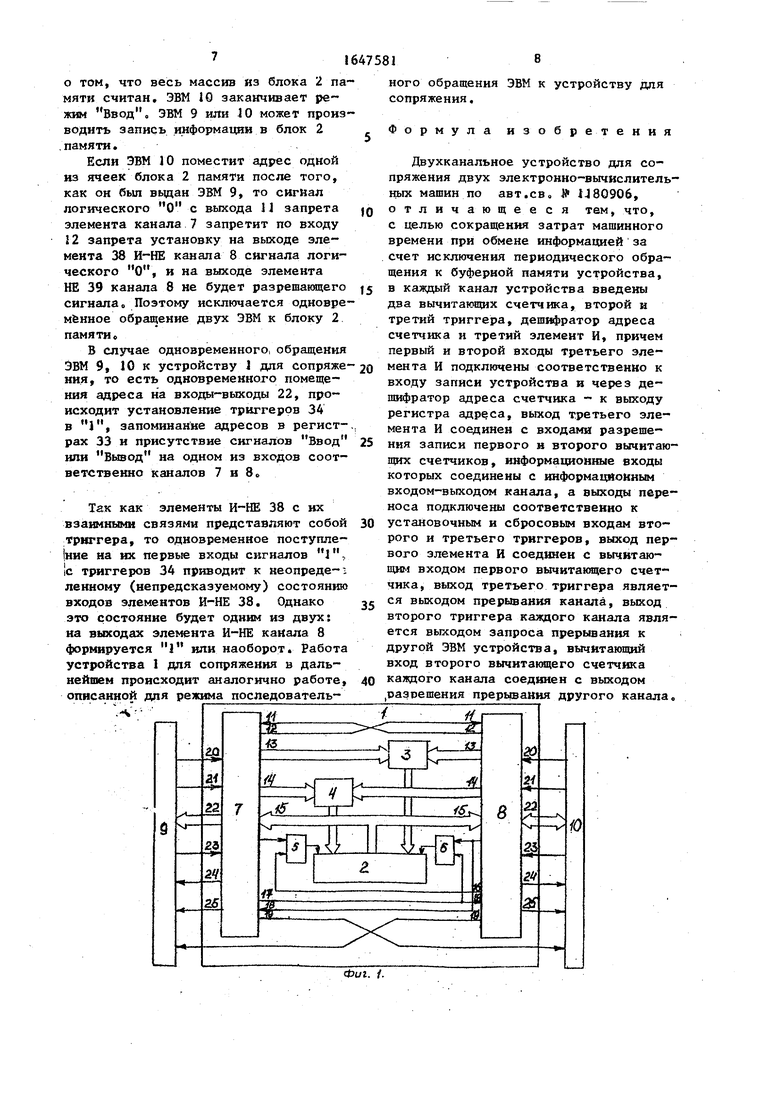

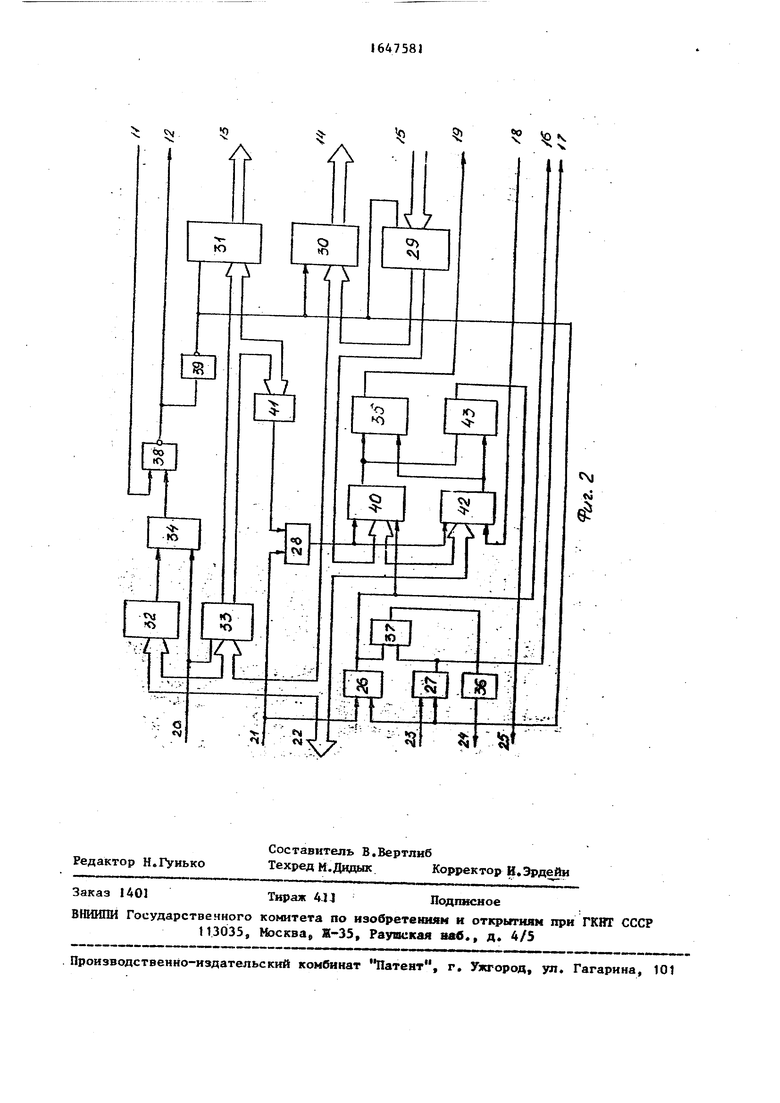

На фиг. представлена функциональная схема устройства для сопряжения; на фиг.2 - функциональная схема канала.

Устройство 1 для сопряжения двух ЭВМ (фиг. 1) содержит блок 2 памяти, первую 3 и вторую 4 группы элементов ИЛИ, первый 5 и второй 6 элементы ИЛИ, первый 7 и второй 8 каналы. Первая 9 и вторая 40 ЭВМ соединены соответственно с каналами 7 и 8. Кроме того, устройство 1 для сопряжения имеет выход 11 и вход 1 2 запрета, выход J3 адреса, выход 14 и вход 15 данных, выход 16 Вывод, выход 17 Ввод, вход 18 Разрешение прерывания, выход 19 Запрос прерывания, вход 20 СИ, вход 21 Вывод, информационные входы-вы ходы 22, вход 23 Ввод, выход 24 управления, выход 25 прерывания.

4

Первый 7 и второй 8 каналы (фиг.2) содержат первый 26, второй 27 и третий 28 элементы И, первую 29, вторую 30 и третью 3J группы элементов И, дешифратор 32 адреса, регистр 33 адреса, первый 34 и второй 35 триггера, элемент 36 задержки элемент ИЛИ 37, элемент И-НЕ 38, элемент НЕ 39, первый вычитающий счетчик 40, дешифратор 4J адреса счетчика, второй вычитающий счетчик 42, третий триггер 43.

Блок 2 памяти представляет собой оперативное запоминающее устройство емкостью 4-32 К 16-разрядных слов, выполненное на интегральных микросхемах, обеспечивающих время обращения к запоминающему устройству порядка I мкс,

Дешифратор 32 адреса предназначен для дешифрации группы адресов, соответствующих адресному полю блока 2 памяти, выделяемых программно из общего адресного пространства ЭВМ 9 и 10, и представляет собой обычную схему дешифрации двоичного кода в позиционный, в которой сигнал на выходе каждой из шин, объединенных в дальнейшем через элемент ИЛИ, соответствует одной или нескольким комбинациям двоичного кода на входе.

Регистр 33 адреса предназначен для хранения адреса ячейки блока 2 памяти в пределах одного цикла обращения ЭВМ 9 и 10 к устройству 1 сопряжения. Регистр 33 состоит из D- триггеров, информационные входы которых являются информационными входами регистра, а тактовые, соединен- ные вместе,- тактовыми входами. Количество D-триггеров регистра определяется количеством разрядов двоичного слова ЭВМ, которое обычно равно 16

Функции синхронизации при переда- че адреса и приеме-передаче данных выполняют сигналы управления, поступающие от ЭВМ на входы 20, 21. Сигнал синхронизации на вход 20 устройства 1 вырабатывается ЭВМ. Перед- ний отрицательный фронт этого сигнала означает, что адрес находится на линии 22„ Сигнал на входе 20 сохраняет активный уровень до окончания цикла обращения ЭВМ к устройству J.

Сигнал Ввод вырабатывается ЭВМ, поступает на вход 23 во время действия сигнала на входе 20 и означает, что ЭВМ готова принять данные от

0

Q

5 Q v

5

блока 2 памяти при операции Считывание,,

Сигнал Вывод вырабатывается ЭВМ, поступает на вход 24 во время действия сигнала на входе 20 и означает, что на линии 22 помещены данные для записи в блок 2 памяти при операции Запись.

Сигнал на выходе 24 информирует ЭВМ о том, что данные установлены или приняты с линии устройством 1, и формируется путем подачи сигналов Ввод или Вывод на элемент 36 задержкио

Длительность задержки определяется временем обращения к блоку 2 памяти, поскольку наличие сигнала ка входе 24 сигнализирует о завершении операции ввода-вывода

Счетчики 40, 42 представляют собой вычитающий двоичный счетчик с количеством триггеров, определяемым как двоичный логарифм от объема максимального передаваемого массива, и с управляющим выходом признака нулевого состояния, активный уровень сигнала на котором вырабатывается при нулевом состоянии всех триггеров счетчика.

Дешифратор 41 адреса счетчика представляет собой схему, активный уровень сигнала на выходе которой вырабатывается при наличии на ее входе адреса счетчиков 40 и 42, и может быть построен как схема совпадения, на одну группу входов которой поступает информация с регистра 33 адреса, а на другой группе входов перемычками установлен адрес счетчика.

Сигнал Разрешение прерывания вырабатывается ЭВМ, поступает на вход 18 устройства и информирует устройство, что ЭВМ приняла запрос на прерывание от устройства I для сопряжения.

Сигнал запроса прерывания на выходе 19 Информирует одну ЭВМ, что другая ЭВМ записала в блок 2 памяти массив информации, Сигнал запрета записи на выходе 25 информирует ЭВМ, что в блоке 2 памяти записан и еще не считан массив информациио

Устройство работает следующим образом

Пусть первая ЭВМ 9 подготовила массив информации и начинает запись s блок 2 памяти Перед записью маесива ЭВМ 9 устанавливает на информа- ционных входах-выходах адрес счетчика 40 канала 7, Так как на входе дешифратора адреса счетчика 41 находится адрес счетчика, на его выходе имеется активный уровень напряжения, ЭВМ 9 помещает на информационные входы-выходы 22 данные, которые определяют число слов в массиве и вырабатывают на входе 2-1 активный сигнал Вывод. На выходе элемента И 28 формируется активный уровень, который записывает данные в вычитающие счетчики 40-и 42. После этого начинается запись слов массива в блок 2 памяти

Запись каждого слова массива про- .исходит следующим о-бразом0

ЭВМ 9 в адресной части цикла Вывод передает на входы-выходы 22 адрес ячейки блока 2 памяти, в которую необходимо записать информацию. На входе 20 СИ при этом присутствует высокий потенциал 1, который поступает на тактовые входы регистра 33 и триггера 34 канала 7. В регистр 33 записывается адрес. Дешифратор 32 дешифрирует адрес и в случае принадлежности его адресному полю блока 2 памяти вырабатывает сигнал на информационный вход первого триггера 34, который устанавливает первый триггер 34 в 1 . Сигнал с выхода первого триггера 34 поступает на первый вход элемента И-НЕ 38, на втором входе которого присутствует высокий потенциал 1 с входа Запрет (с выхода элемента И-НЕ 38 канала 8), и вызывает на его выходе появление сигнала логического О. На выходе элемента НЕ 39 появляется разрешающий сигнал 1, которьй поступает на вторые входы элементов 26, 27, 29, 30 и первые входы 14 элементов. После адресной части цикла ЭВМ 9 помещает на входы-выходы 22 данные, которые необходимо записать в блок 2 памяти, после чего на входе 21 устанавливается сигнал Вывод. Так как на втором входе элемента И 26 присутствует сигнал I, то на его выходе сигнал Вывод через элемент ИЛИ 5 поступает на управляющий вход блока 2 Запись. При этом на адресных и информационных входах блока 2 присутствует соответственно адрес с выхода адреса 13 через элемент ИЛИ 3 и

0

5

0

данные с выхода 14 через элемент ИЛИ 4, следовательно происходит операция записи выданных ЭВМ 9 данных по необходимому адресу. Одновременно сигнал поступает на счетный вход счетчика 40, уменьшая его содержимое на единицу„

Сигнал Вывод поступает также через элемент ИЛИ 37 на элемент 36 задержки, с выхода которого через время задержки поступает по входу управления 24 на ЭВМ 9, в результате чего сигнал Вывод устанавливается в О, снимаются данные с входов- выходов 22 и устанавливается высокий потенциал на входе 20 СИ.

После записи последнего слова массива в блок 2 памяти содержимое счетчика 40 становится равным нулю, и на его выходе признака нулевого состояния появляется управляющий сигнал, который фронтом импульса перебрасывает триггера 35, 43 в состояние логической 1. Сигнал с выхода триггера 35 поступает на выход 19 Запрос прерывания ЭВМ 10, сообщая ей, что массив записан в блок 2 памяти. Сигнал с выхода триггера 43 поступает на выход 12 ЭВМ 9, сообщая ей, что в блоке 2 памяти находится несчитанная информация. ЭВМ 10. приняв запрос на прерывание, выдает сигнал разрешения прерывания, который поступает на вход 18,и далее на вход вычитающего счетчика 42, уменьшая его содержимое на единицу. ЭВМ 10 производит цикл Ввод, в котором из блока 2 считывается одно слово Опе- 0 рация Ввод аналогична операции Вывод за исключением того, что управляющийсигнал Ввод поступает на вход элемента ИЛИ бис его выхода на управляющий вход блока 2 памяти о

5

0

5

5

0

5

Содержимое ячейки памяти, адрес которой указан на адресных линиях блока 2 памяти, по входу 15 данных и далее через элемент 29 передается на информационный вход-выход 22 устройства После считывания всего массива содержимое счетчика 42 становится равным нулю и на его выходе признака нулевого состояния появляется управляющий сигнал, который фронтом импульса перебрасывает триггеры 35, 43 в состояние логического О. При этом ЭВМ 9 и 10 получают информацию

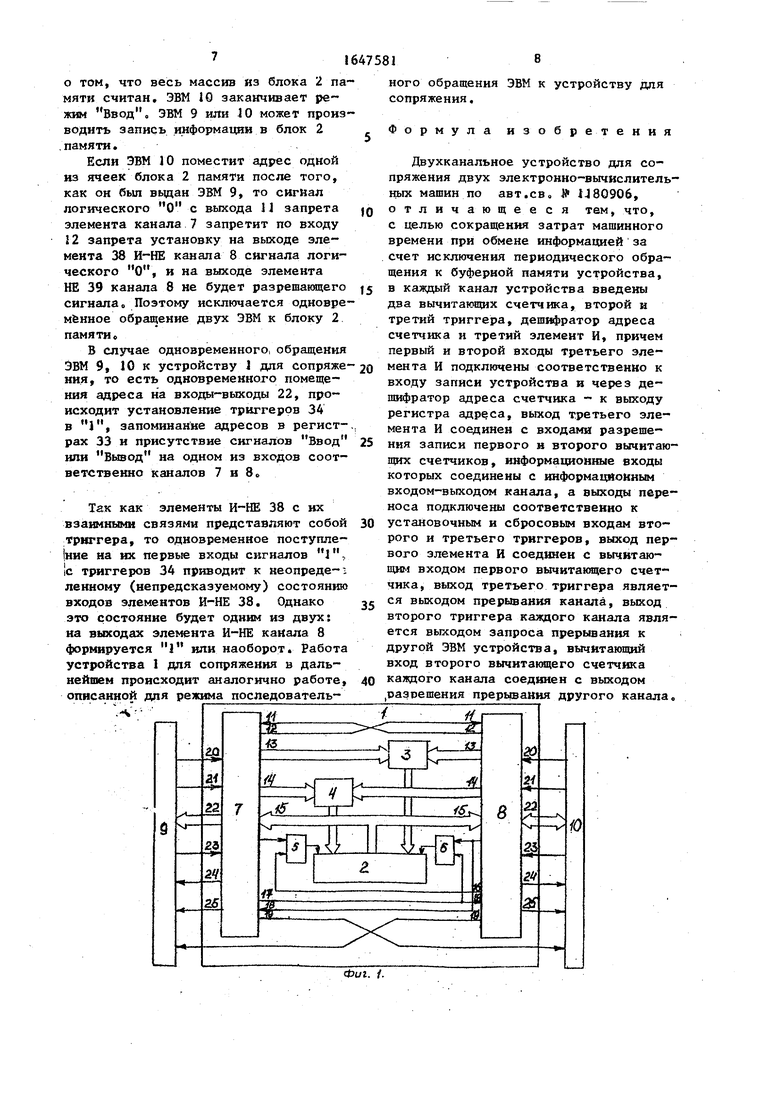

о том, что весь массив из блока 2 памяти считан. ЭВМ 10 заканчивает ре- жим Ввод, ЭВМ 9 или 10 может производить запись информации в блок 2 памяти.

Если ЭВМ 10 поместит адрес одной из ячеек блока 2 памяти после того, как он был вьщан ЭВМ 9, то сигнал логического О с выхода 1J запрета элемента канала 7 запретит по входу 12 запрета установку на выходе элемента 38 И-НЕ канала 8 сигнала логического О, и на выходе элемента НЕ 39 канала 8 не будет разрешающего сигналао Поэтому исключается одновременное обращение двух ЭВМ к блоку 2 памяти

В случае одновременного, обращения ЭВМ 9, 10 к устройству 1 для сопряжения, то есть одновременного помещения адреса на входы-выходы 22, происходит установление триггеров 34 в J, запоминание адресов в регистрах 33 и присутствие сигналов Ввод или Вывод на одном из входов соответственно каналов 7 и 8„

Так как элементы И-НЕ 38 с их взаимными связями представляют собой триггера, то одновременное поступпе- |ние на их первые входы сигналов 1, ic триггеров 34 приводит к неопреде-: ленному (непредсказуемому) состоянию входов элементов И-НЕ 38. Однако это состояние будет одним из двух: на выходах элемента И-НЕ канала 8 формируется 1 или наоборот. Работа устройства 1 для сопряжения в дальнейшем происходит аналогично работе, описанной для режима последователь .ч

0

5

0 5 0

ного обращения ЭВМ к устройству для сопряжения.

Формула изобретения

Двухканальное устройство для сопряжения двух электронно-вычислительных машин по авт.св. № 1480906, отличающееся тем, что, с целью сокращения затрат машинного времени при обмене информацией за счет исключения периодического обращения к буферной памяти устройства, в каждый канал устройства введены два вычитающих счетчика, второй и третий триггера, дешифратор адреса счетчика и третий элемент И, причем первый и второй входы третьего элемента И подключены соответственно к входу записи устройства и через дешифратор адреса счетчика - к выходу регистра адреса, выход третьего элемента И соединен с входами разрешения записи первого и второго вычитающих счетчиков, информационные входы которых соединены с информационным входом-выходом канала, а выходы переноса подключены соответственно к установочным и сбросовым входам второго и третьего триггеров, выход первого элемента И соединен с вычитающим входом первого вычитающего счетчика, выход третьего триггера является выходом прерывания канала, выход второго триггера каждого канала является выходом запроса прерывания к другой ЭВМ устройства, вычитающий вход второго вычитающего счетчика каждого канала соединен с выходом разрешения прерывания другого канала.

М

сО

Ј

| название | год | авторы | номер документа |

|---|---|---|---|

| Двухканальное устройство для сопряжения двух электронно-вычислительных машин | 1987 |

|

SU1425692A2 |

| Устройство для сопряжения ЭВМ с внешними устройствами | 1987 |

|

SU1478222A1 |

| Устройство отладки микропрограммных блоков | 1988 |

|

SU1541617A1 |

| УСТРОЙСТВО ДЛЯ ПОИСКА ПЕРЕМЕЖАЮЩИХСЯ ОТКАЗОВ В МИКРОПРОЦЕССОРНЫХ СИСТЕМАХ | 1996 |

|

RU2099777C1 |

| УСТРОЙСТВО ДЛЯ ПОИСКА ПЕРЕМЕЖАЮЩИХСЯ НЕИСПРАВНОСТЕЙ В МИКРОПРОЦЕССОРНЫХ СИСТЕМАХ | 1992 |

|

RU2030784C1 |

| Устройство для сопряжения ЭВМ с разноскоростными группами внешних устройств | 1990 |

|

SU1837302A1 |

| Устройство для сопряжения вычислительной машины с линиями связи | 1985 |

|

SU1262512A1 |

| Устройство для сопряжения вычислительной машины с телеграфными каналами связи | 1986 |

|

SU1392571A1 |

| Устройство для отладки микропроцессорных систем | 1989 |

|

SU1672455A1 |

| Устройство для отладки программ | 1988 |

|

SU1654827A1 |

Изобретение относится к вычислительной технике и может быть использовано для буферизации сообщений при обмене массивами информации между двумя электронно-вычислительными ма- шинами (ЭВМ) и является усовершенствованием устройства по авт.св. № 1180906. Целью изобретения является сокращение затрат машинного времени при обмене информацией за счет исключения периодического обращения к буферной памяти устройства„ Цель достигается тем, что в устройство, содержащее блок памяти, две группы элементов ИЛИ, два элемента ИЛИ, два канала, каждый из которых включает дешифратор адреса, триггер, регистр адреса, элемент И-НЕ, элемент НЕ, два элемента И, три группы элементов И, элемент ИЛИ и элемент задержки, введены в каждый канал два вычитающих счетчика, два триггера, Q третий элемент И и дешифратор адреса счетчика, 2 ил S

| Двухканальное устройство для сопряжения двух электронно-вычислительных машин | 1984 |

|

SU1180906A1 |

Авторы

Даты

1991-05-07—Публикация

1989-04-04—Подача