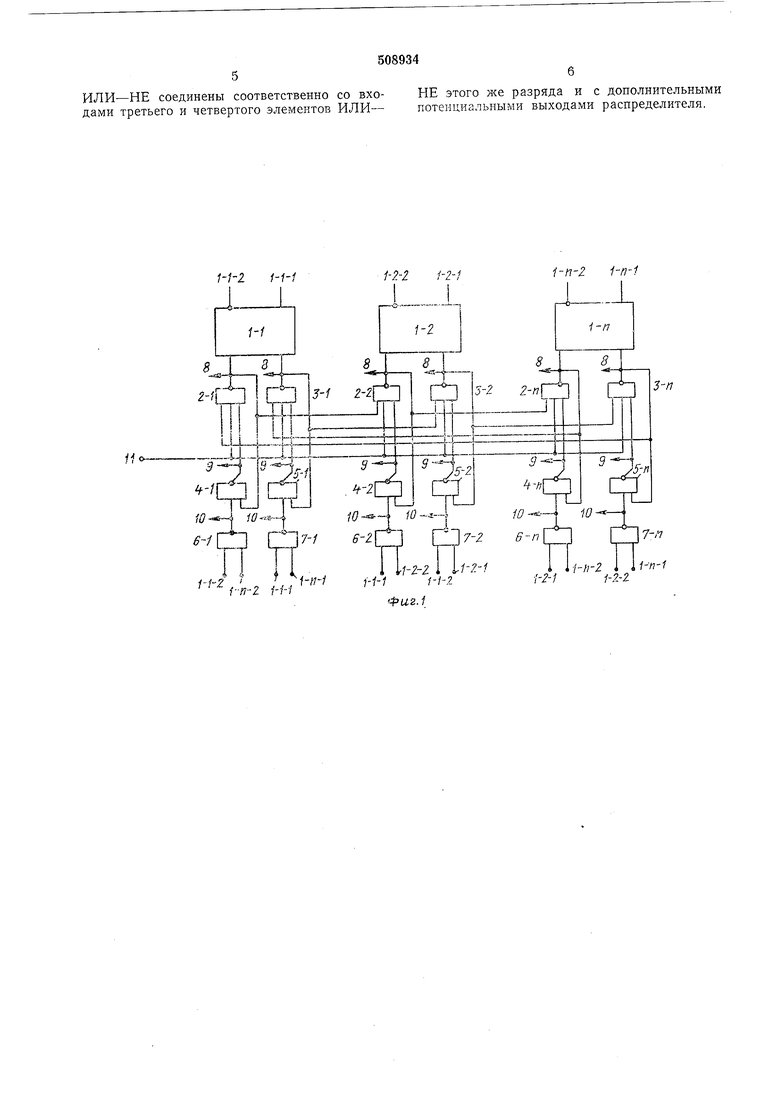

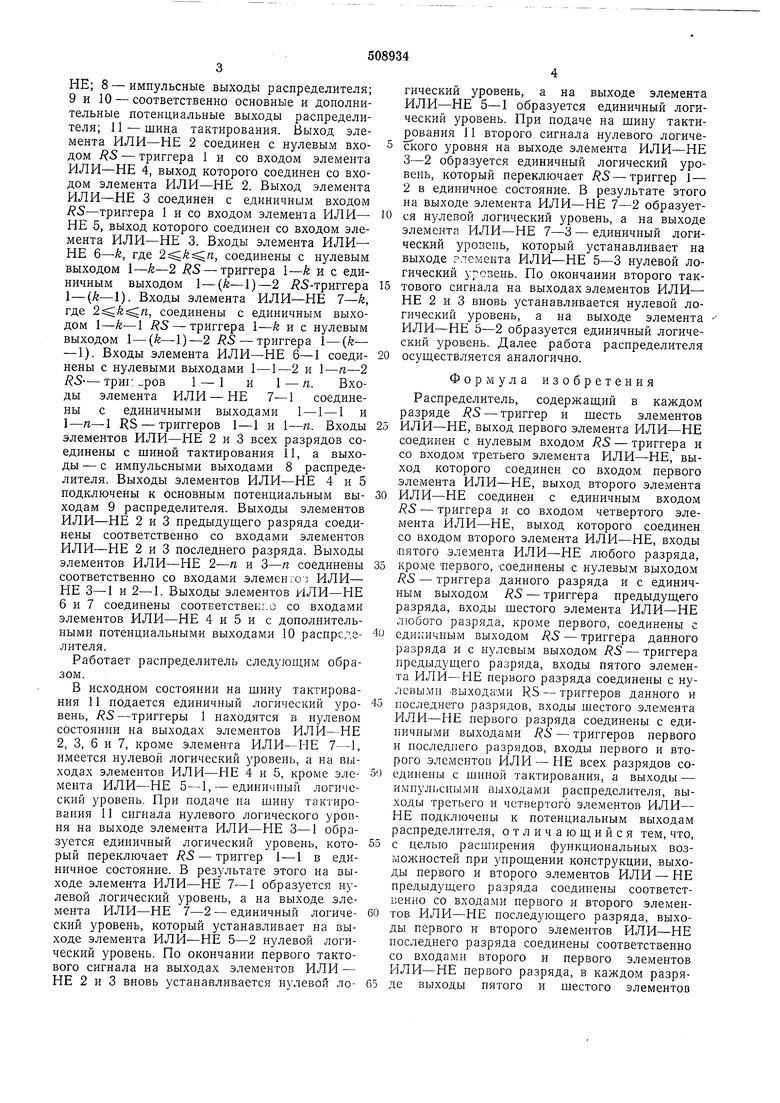

НЕ; 8 - импульсные выходы распределителя; 9 и 10 - соответственно основные и дополнительные потенциальные выходы распределителя; 11 - шина тактирования. Выход элемента ИЛИ-НЕ 2 соединен с нулевым входом 5 - триггера 1 и со входом элемента ИЛИ-НЕ 4, выход которого соединен со входом элемента ИЛИ-НЕ 2. Выход элемента ИЛИ-ЛЕ 3 соединен с единичным входом KS-триггера 1 и со входом элемента ИЛИ- НЕ 5, выход которого соединен со входом элемента ИЛИ-НЕ 3. Входы элемента ИЛИ- НЕ 6-k, где , соединены с нулевым выходом 1-k-2 RS - триггера l-k и с единичным выходом 1-(k-1)-2 5-триггера 1-(-1). Входы элемента ИЛИ-НЕ 7-k, где , соединены с единичным выходом 1-k-1 RS - триггера 1-k и с нулевым выходом 1-(k-1)-2 JRS - триггера 1-(k- - 1). Входы элемента ИЛИ-НЕ 6-1 соединены с нулевыми выходами 1-1-2 и 1-п-2 RS-триг.ров 1 - 1 и 1-п. Входы элемента ИЛИ - НЕ 7-1 соединены с единичными выходами 1 - 1 - 1 и 1-п-1 RS - триггеров 1-1 и 1-п. Входы элементов ИЛИ-НЕ 2 и 3 всех разрядов соединены с шиной тактирования 11, а выходы - с импульсными выходами 8 распределителя. Выходы элементов ИЛИ-НЕ 4 и 5 подключены к основным потенциальным выходам 9 распределителя. Выходы элементов ИЛИ-НЕ 2 и 3 предыдущего разряда соединены соответственно со входами элементов ИЛИ-НЕ 2 и 3 последнего разряда. Выходы элементов ИЛИ-НЕ 2-п и 3-п соединены соответственно со входами элементеi ИЛИ- НЕ 3-1 и 2-I. Выходы элементов ИЛИ-НЕ 6 и 7 соединены соответственно со входами элементов ИЛИ-НЕ 4 и 5 и с дополнительными потенциальными выходами 10 распрсделителя.

Работает распределитель следующим образом.

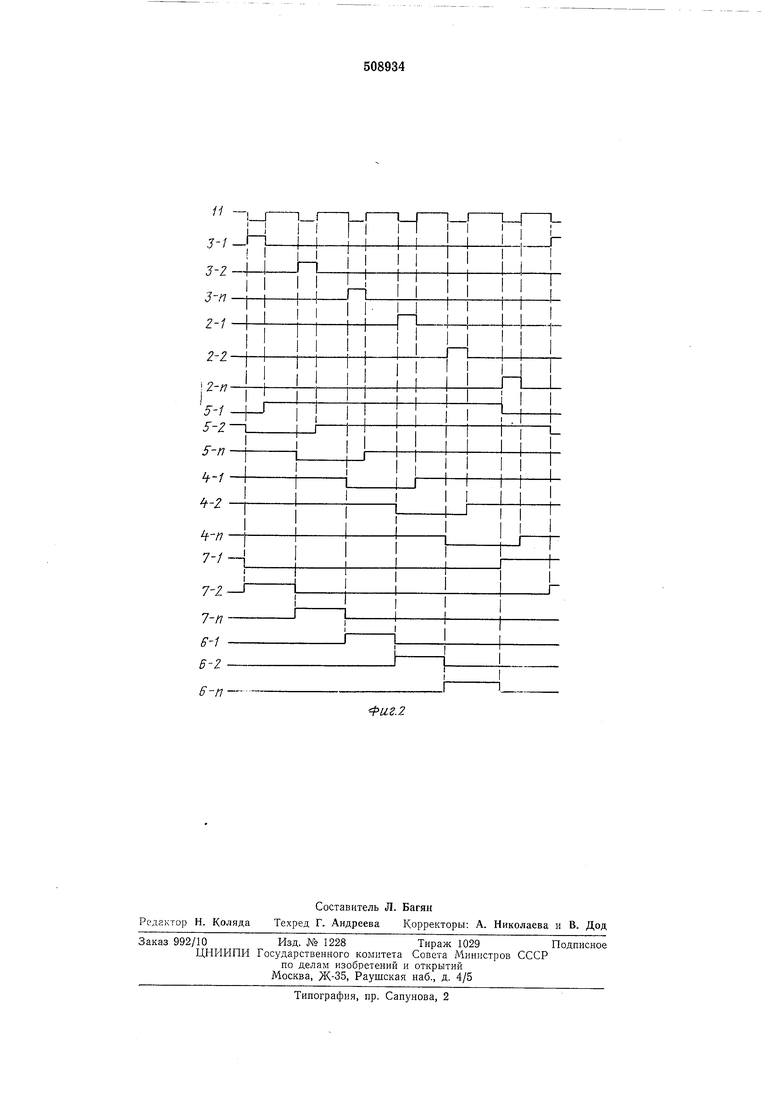

В исходном состоянии на шину тактирования 11 подается единичный логический уровень, RS -триггеры 1 находятся в нулевом состоянии на выходах элементов ИЛИ-НЕ 2, 3, 6 и 7, кроме элемента ИЛИ-НЕ 7-1, имеется нулевой логический уровень, а на выходах элементов ИЛР1-НЕ 4 и 5, кроме элемента ИЛИ-НЕ 5-1, - единичный логический уровень. При подаче на шину тактирования 11 сигнала нулевого логического уровня на выходе элемента ИЛИ-НЕ 3-1 образуется единичный логический уровень, который переключает RS - триггер 1 - 1 в единичное состояние. В результате этого на выходе элемента ИЛИ-НЕ 7-1 образуется нулевой логический уровень, а на выходе элемента ИЛИ-НЕ 7-2 - единичный логический уровень, который устанавливает на выходе элемента ИЛИ-НЕ 5-2 нулевой логический уровень. По окончании первого тактового сигнала на выходах элементов ИЛИ - НЕ 2 и 3 вновь устанавливается нулевой логический уровень, а на выходе элемента ИЛИ-НЕ 5-1 образуется единичный логический уровень. При подаче на шину тактирования 11 второго сигнала нулевого логического уровня на выходе элемента ИЛИ-НЕ 3-2 образуется единичный логический уровень, который переключает RS - триггер 1 - 2 в единичное состояние. В результате этого на выходе элемента ИЛИ-НЕ 7-2 образуется нулевой логический уровень, а на выходе элемента ИЛИ-НЕ 7-3 - единичный логический уровень, который устанавливает на выходе лемента ИЛИ-НЕ 5-3 нулевой логический уровень. По окончании второго тактового сигнала на выходах элементов ИЛИ- НЕ 2 и 3 вновь устанавливается нулевой логический уровень, а на выходе элемента ИЛИ-НЕ 5-2 образуется единичный логический уровень. Далее работа распределителя осуществляется аналогично.

Формула изобретения

Распределитель, содержащий в каждом разряде RS - триггер и шесть элементов ИЛИ-НЕ, выход первого элемента ИЛИ-НЕ соединен с нулевым входом RS - триггера и со входом третьего элемента ИЛИ-НЕ, выход которого соединен со входом первого элемента ИЛИ-НЕ, выход второго элемента ИЛИ-НЕ соединен с единичным входом RS - триггера я со входом четвертого элемента ИЛИ-НЕ, выход которого соединен со входом второго элемента ИЛИ-НЕ, входы пятого элемента ИЛИ-НЕ любого разряда, кроме TiepBoro, соединены с нулевым выходом RS - триггера данного разряда и с единичным выходом RS - триггера предыдущего разряда, входы шестого элемента ИЛИ-НЕ любого разряда, кроме первого, соединены с единичным выходом RS - триггера данного разряда и с нулевым выходом RS - триггера предыдущего разряда, входы пятого элемента ИЛИ-НЕ первого разряда соединены с нулевыми выхода-ми RS - триггеров данного и последнего разрядов, входы шестого элемента ИЛИ-НЕ первого разряда соединены с единичными выходами RS - триггеров первого и последнего разрядов, входы первого и второго элементов ИЛИ - НЕ всех разрядов соединены с шиной тактирования, а выходы - импульсными выходами распределителя, выходы третьего и четвертого элементов ИЛИ- НЕ подключены к потенциальным выходам распределителя, отличающийся тем, что, с целью расширения функциональных возможностей при упрощении конструкции, выходы первого и второго элементов ИЛИ - НЕ предыдущего разряда соединены соответственно со входами первого и второго элементов ИЛИ-НЕ последующего разряда, выходы первого и второго элементов ИЛИ-НЕ последнего разряда соединены соответственно со входами второго и первого элементов ИЛИ-НЕ первого разряда, в каждом разряде выходы пятого и шестого элементов ИЛИ-НЕ соединены соответственно со входами третьего и четвертого элементов ИЛИ- НЕ этого же разряда и с дополнительными потенциальными выходами распределителя.

| название | год | авторы | номер документа |

|---|---|---|---|

| Распределитель импульсов | 1973 |

|

SU484643A1 |

| Распределитель импульсов | 1975 |

|

SU573877A1 |

| Трехканальный кольцевой распределитель | 1976 |

|

SU677105A1 |

| Распределитель | 1976 |

|

SU658737A1 |

| Реверсивный распределитель импульсов | 1981 |

|

SU953728A1 |

| СИСТЕМА ВОЗБУЖДЕНИЯ СИНХРОННОГО ГЕНЕРАТОРА С УПРАВЛЯЕМОЙ ДВУНАПРАВЛЕННОЙ ВНЕШНЕЙ ФОРСИРОВКОЙ | 2021 |

|

RU2781107C1 |

| Распределитель импульсов | 1976 |

|

SU660255A1 |

| Распределитель | 1974 |

|

SU491221A1 |

| Асинхронный распределитель | 1981 |

|

SU997261A1 |

| Устройство для обнаружения ошибок в параллельном @ -разрядном коде с постоянным весом К | 1982 |

|

SU1149260A1 |

3-1 г-г jг (..-.u- J ;J J--if-2-2 1-2-1 УТ8 S-2 Z-n . /-/-/ -2 /7-/ /-/r2 i if-rt- /-7-2

Авторы

Даты

1976-03-30—Публикация

1974-10-30—Подача