импульсов соединен с вторым информа ционным входом третьего коммутатора п-го блока коммутации, второй выход третьего коммутатора первого блока коммутации соединен с вторым входом второго элемента И-НЕ (п+2)-го разряда распределителя импульсов, выход первого элемента И-НЕ и нулевой выход RS-триггера (п+2)-го разряда распределителя импульсов соединены соответственно с вторыми входами первого и второго коммутаторов первого блока коммутации, вькод генератора тактовых импульсов соединен с тактовым входом блока синхронизации, первый и второй выходы которог соединены соответственно с входом синхронизации триггера и с вторыми R-входами RS-триггеров с первого 0 по (п+1)-й разряд распределителя, второй выход блока синхронизации соединен с вторым S-входом (п+2)-го разряда распределителя и входом начальной установки счетчика импульсов по модулю (К+1), единичный выход RS-триггера (п+1)-го разряда распределителя импульсов соединен с первым информационным входом блока синхронизации, выход элемента ИЛИ соединен со счетным входом счетчика импульсов по модулю (К+1), выходы которого, соответствующие весам К и (К+1), соединены соответственно с информационным входом триггера и вторым информационным входом блока синхронизации , выход триггера является выходом контроля устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Пороговый элемент | 1986 |

|

SU1387191A1 |

| Пороговый элемент | 1982 |

|

SU1091344A1 |

| Пороговое устройство (его варианты) | 1984 |

|

SU1352449A1 |

| Пороговый элемент | 1985 |

|

SU1297220A1 |

| Пороговый элемент | 1985 |

|

SU1297219A1 |

| Пороговый элемент | 1987 |

|

SU1647871A1 |

| Устройство для обнаружения ошибок в равновесном коде К из @ | 1987 |

|

SU1564731A1 |

| Устройство для подсчета числа единиц двоичного кода | 1987 |

|

SU1569995A1 |

| Устройство для контроля равновесного кода | 1987 |

|

SU1580563A1 |

| Устройство для контроля двоичного кода по модулю К | 1990 |

|

SU1737736A1 |

УСТРОЙСТВО ДЛЯ ОБНАРУЖЕНИЯ ОШИБОК В ПАРАЛЛЕЛЬНОМ П-РАЗРЯДНОМ КОДЕ С ПОСТОЯННЫМ ВЕСОМ К, содержащее генератор тактовых импульсов, элемент ИЛИ, триггер и (п+2)-разрядный распределитель импульсов, каждый разряд которого содержит RS-триггер, два элемента И-НЕ, причем в каждом разряде распределителя импульсов единичный выход RS-триггера соединен с первым входом первого элемента И-НЕ, выход которого соединен с первым входом второго элемента И-НЕ выход второго элемента И-НЕ соединен с первым R-входом RS-триггера, выход первого элемента И-НЕ и нулевой выход RS-триггера (п+1)-го разряда распределителя импульсов соединены соответственно с первым 8-входом RS-триггера и третьим входом первого элемента И-НЕ (п+2)-го разряда распределителя импульсов, единичный выход RS-триггера (п+2)-го разряда распределителя импульсов соединен с вторым входом второго элемента И-НЕ (п+1)-го разряда распределителя, выход генератора тактовых импульсов соединен с вторыми входами первых элементов И-НЕ всех разрядов распределителя импульсов, отличающееся тем, что, с ВСЕСОШИДЯ .:. у :г..;-.,-. ir.- ,j rj Е целью увеличения быстродействия устройства, в него введены счетчик импульсов по модулю (К+1), блок синхронизации и п блоков коммутации, каждый из которых содержит три коммутатора, причем в каждом i-м блоке коммутации (,п) первый выход первого коммутатора соединен с S-входом RS-триггера i-ro разряда распределителя и i-м входом элемента ИЛИ, вход каждого i-ro разряда контролируемого кода устройства соединен с управляющими входами первого, второго и третьего коммутаторов i-ro блока коммутации, первые выходы второго и третьего коммутаторов i-ro б.локча коммутации соединены соот(Л ветственно с третьим входом первого и вторым входом второго элементов И-НЕ i-ro разряда распределителя импульсов, выход первого элемента И-НЕ, нулевой и единичные в.ыходы RS-триггера i-го разряда распределителя соединены с первьвли инфор J мационными входами соответственно QD первого, второго и третьего О) мутаторов i-ro блока, вторые выходы первого, второго и третьего коммуО таторов 1-го блока соединены соответственно с вторыми информационными входами первого и второго коммутаторов (i+1)-ro блокаде вторым информационньп-1 входом третьего коммутатора (i-l)-ro блока, вторые выходы первого и второго коммутаторов п-го блока соединены соответственно с S-входом RS-триггера и третьим входом первого элемента И-НЕ (п+1)-го разряда распределителя импульсов, единичный выход RS-триггера (п+1)-го разряда распределителя

Изобретение относится к автоматике и вычислительной технике и может использоваться для построения различных устройств обработки дискретной информации.

Известна схема контроля двух и только двух линий из шести, которая содержит пять логических схем, соединенных последовательно. Каасдая схема соединена входами с выходами предьщущей схемы и входной шиной. Каждая логическая схема содержит устройство, реагирующее на наличие . двух и только двух входных сигналов на линиях lj .

Недостатком данной схемы являются ее ограниченные функциональные возможности: она позволяет обнаруживать наличие сигналов на двух линиях из шести, обнаруживать ошибки в кодах большей разрядности или кодах с иным весом она не может. Кроме того схема характеризуется большим объемом оборудования.

Наиболее близким по технической сущности к предлагаемому является устройство для контроля двоичного кода на четность, содержащее элемент ИЛИ, распределитель импульсов, триггер и группу элементов И, первые входы которых соединены с выходми соответствующих контролируемых разрядов, выходы элементов И соединены со входами элемента ИЛИ, выход которого соединен со счетным входом триггера, выход которого является выхсд.М устройства, выходы распределителен импульсов соединены со вторыми входами соответствующих элементов И группы, первьй выход распределителя импульсов соединен с нулевым входом триггера,тактовьш вход устройства соединен со входом распределителя 2.

Однако известное устройство обладает маль№1 быстродействием, поскольку для получения результата требуется {п+1) тактов работы, и малыми функциональными возможностями, так как оно не позволяет обнаруживать ошибк в кодах с постояннь1М весом.

Целью изобретения является повы,шение быстродействия устройства.

Указанная цель достигается тем, что в устройство для обнаружения ошибок в параллельном п-разрядном коде с постоянным весом К, содержащее генератор тактовых импульсов, элемент,ИЛИ, триггер и (п+2)-разрядный распределитель импульсов, каждый разряд которого содержит RS-триггер, два элемента И-НЕ, причем в каждом разряде распределителя.

импульсов единичный выход RS-триггера соединен с первым входом первого элемента И-НЕ, выход которого соединен с первым входом второго элемента И-НЕ, выход второго элемента И-НЕ соединен с первым R-BXOдом RS-триггера, выход первого элемента И-НЕ и нулевой выход RS-триггера (п+1).-го разряда распределителя : импульсов соединены соответственно с первым S-входом RS-триггера и третьим входом первого элемента И-НЕ (п+2)-го разряда распределителя импульсов, единичный выход RS-триггера (п+2)-го разряда распределителя импульсов соединен со втррым входом второго элемента И-НЕ (п+1)-гр разряда распределителя, выход генератора тактовых импульсов соединен со вторыми входами перЬьк элементов И-НЕ всех разрядов распределителя импульсов, введены счетчик импульсов по модулю (К+1), блок синхронизации и п блоков коммутации каждый из которых содержит три коммутатора, причем, в каждом i-м блоке коммутации (,n) первый выход первого коммутатора соединен с S-вxoдo RS-триггера i-ro разряда распределителя и i-M входом элемента ИЛИ, вход каждого i-ro разряда контролируемого кода устройства соединен с управляющими входами первого, второго и третьего коммутаторов i-ro блока коммутации, первые выходы второго и третьего коммутаторов i-ro блока коммутации соединены соответственно с третьим входом первого и вторым входом второго элементов И-НЕ i-го разряда распределителя импульсов, выход первого элемента И-НЕ, нулевой и единичные выходы RS-1pиггepa 1-го разряда распределителя импульсов соединены с первыми информационными входами соответственно первого, второго и третьего коммутаторов i-ro блока коммутации, вторые выходы первого, второго и третьего коммутаторов i-ro блока коммутации соединены соответственно со вторыми информационными входами первого и второго коммутаторов (i+1)-ro блока коммутации,со вторым информационным входом третьего коммутатора (i-l)-r блока коммутации, вторые выходы первого и второго коммутаторов п-го блока коммутации соединены .соответственно с S-входом RS-триггера и третьим входом первого элемента И-НЕ (п+1)-го разряда распределителя импульсов, единичный выход 5 RS-триггера (п+1)-го разряда распределителя импульсов соединен со вторым информационным входом третье го коммутатора п-го блока коммутации, второй выход третьего коммута-

О тора первого блока коммутации соединен со вторьм входом второго эле,мента И-НЕ (п+2)-го разряда распре|делителя импульсов, выход первою элемента И-НЕ и нулевой выход

5 RS-триггера ()-го разряда распределителя импульсов соединены соответственно со вторыми входами первого и второго коммутаторов первого блока коммутации, выход генератора тактовых импульсов соединен с тактовым входом блока синхронизации, первый и второй выходы которого соединены соответственно со входом синхронизации триггера и со вторыми

. R-входами RS-триггеров с первого по (п+1)-й разряд распределителя, второй выход блока синхронизации соединен со вторым S-входом (п+2)-го разряда распределителя и входом начальной установки счетчика импульсов по модулю (К+1), единичный выход RS-триггера (п-«-1)-го разряда распределителя импульсов соединен с первьш информационным входом блока синхронизации, выход элемента ИЛИ соединен со счетным входом счетчика импульсов по модулю (К+1), выходы которого, соответствующие весам К и (K-fl), соединены соответственно

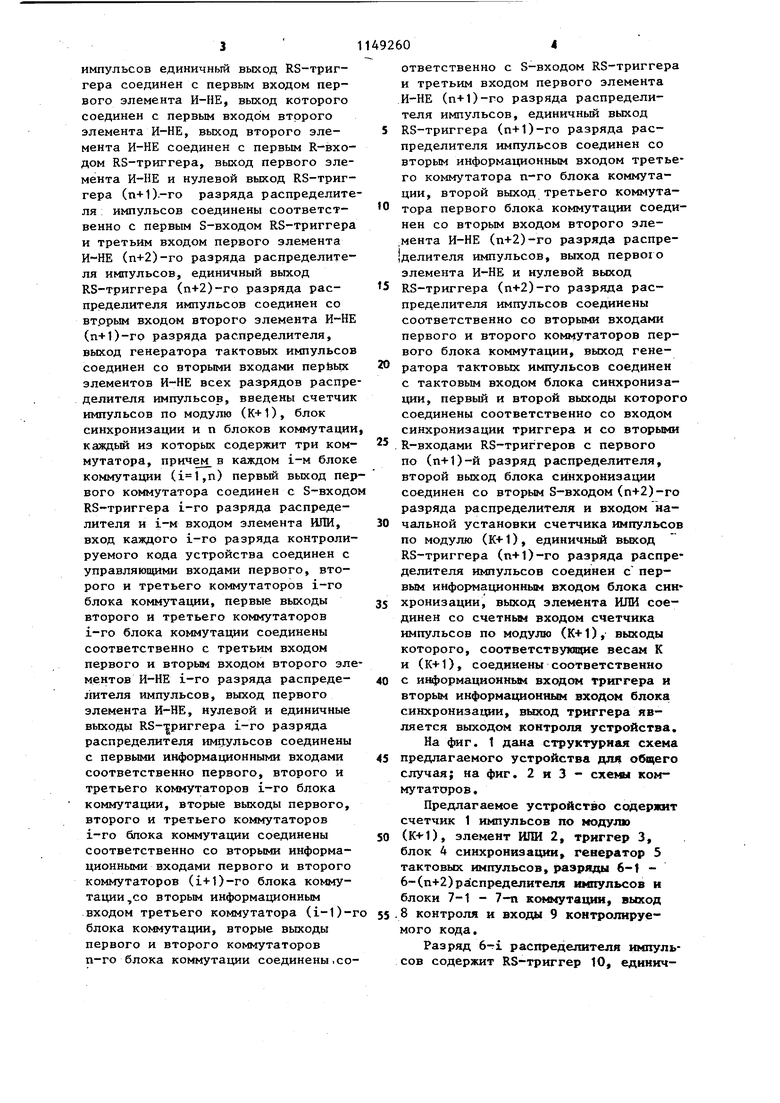

0 с информационным входом триггера и вторым информационным входом блока синхронизации, выход триггера является выходом контроля устройства, На фиг. 1 дана структурная схема

5 предлагаемого устройства для общего случая; на фиг. 2 и 3 - коммутаторов.

Предлагаемое устройство содержит счетчик 1 импульсов по модулю

0 (К4-1), элемент ИЛИ 2, триггер 3, блок А синхронизации генератор 5 тактовых импульсов, разряды 6-1 6-(п+2)распределителя инпульсов и блоки 7-1 - 7-п коммутации, выход

5 - 8 контроля и входал 9 контролируемого кода.

Разряд 6-г1 распределителя га пульсов содержит RS-триггер 10, единичный вькод которого соединен с первым входом элемента И-НЕ 11, вьосод которого соединен с первым входом элемента И-НЕ 12, соединенного выходом с первым R-входом RS-триггера 10.

Блок 7-i коммутации содержит три коммутатора 13, 14 и 15, причем первьй выход коммутатора 13 и его первый информационный вход соединены соответственно (фиг. 1) с входом RS-триггера 10 и выходом элемента И-НЕ 11 разряда 6-i распределителя импульсов, первьй выход коммутатора 14, его первьй информационный вход соединены соответственно с третьим входом элемента И-НЕ 11 и инверсным выходом триггера 10 разряда 6-i, первьй выход и первьй информационный вход коммутатора 15 соединены соответственно с вторым входом элемента И-НЕ 12 и прямым выходом триггера 10 разряда 6-1. Управляющие входы KONMyTaTopoB 13, 14, 15 блока 6-i соединены с i-й входной шиной х.

Вторые выходы коммутаторов 13 и Т4 и второй информационньй вход коммутатора 15 блока 7-i (,2..., n-1) соединены соответственно с первыми информационными входами коммутаторов 13, 14 и вторым выходом коммутатора 15 блока 7-(i+1), а выход блока 7-п - с S-входом триггера 10, третьим входом элемента И-НЕ 11 и прямым выходом триггера 10 разряда 6-(п4-1) распределителя импульсов соответственно. Выход элемента И-НЕ 11, инверсньй выход триггера 10 и второй вход элемента И-НЕ 12 (п+1)-го разряда 6-(п+1) распределителя импульсов соединены соответственно с первым S-входом триггера 10, вторьм входом элемента И-НЕ 11 и прямым выходом триггера 10 разряда 6-(п+2) распределителя импульсов. Выход элемента И-НЕ 11, инверсньй выход триггера 10 и второ вход элемента И-НЕ 12 разряда 6-(п-4-2) распределителя импульсов сое динены соответственно, с первым информационным входом коммутатора 13, первым информационным входом коммутатора 14 и вторым выходом коммутатора 15 блока 7-1.

Входы элемента ИЛИ 2 соединены с 8-входами триггеров 10 разрядов 6-1 - 6-п распределителя импульсов,

соединенными с первыми выходами коммутаторов 13 соответствующих блоков 7-1 - 7-п, а выход - со счетным входом счетчика 1 импульсов по 5 модулю (К+1), вход начальной установки которого соединен с К-входами триггеров 10 разрядов 6-1 - 6-(п+1) распределителя импульсов, вторым S-входом триггера 10 разряда 6-(п+2) распределителя импульсов и вторым выходом блока 4 синхронизации, первьй выход счетчика 1, соответствующий весу К, соединен с информационным входом триггера 3, а второй 5 выход, соответствующий весу (к+1) с вторым входом блока 4 синхронизации, тактовьй вход которого соединен с вторыми входами элементов И-НЕ 11 разрядов 6-1 - 6-(п+2) распределителя импульсов и выходом генератора 5 тактовых импульсов, первьй вход - с прямым выходом триггера 10 разряда 6-(п+1) распределителя импульсов, а первьй выход - с входом 5 синхронизации триггера 3.

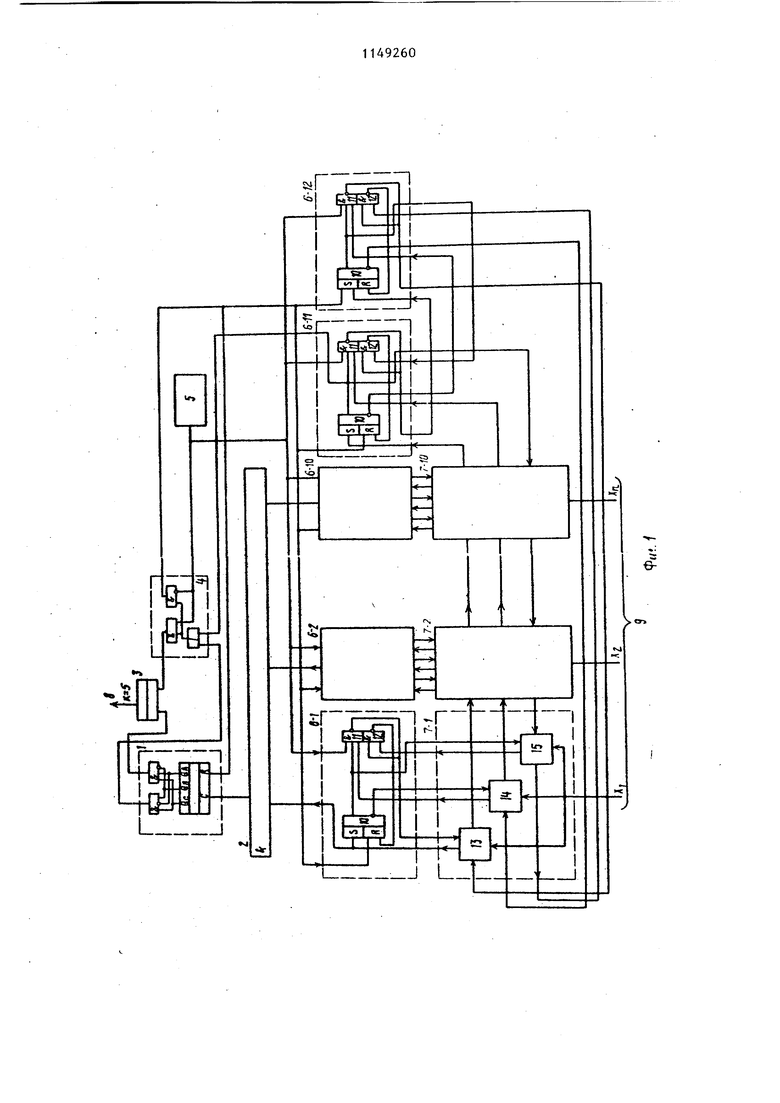

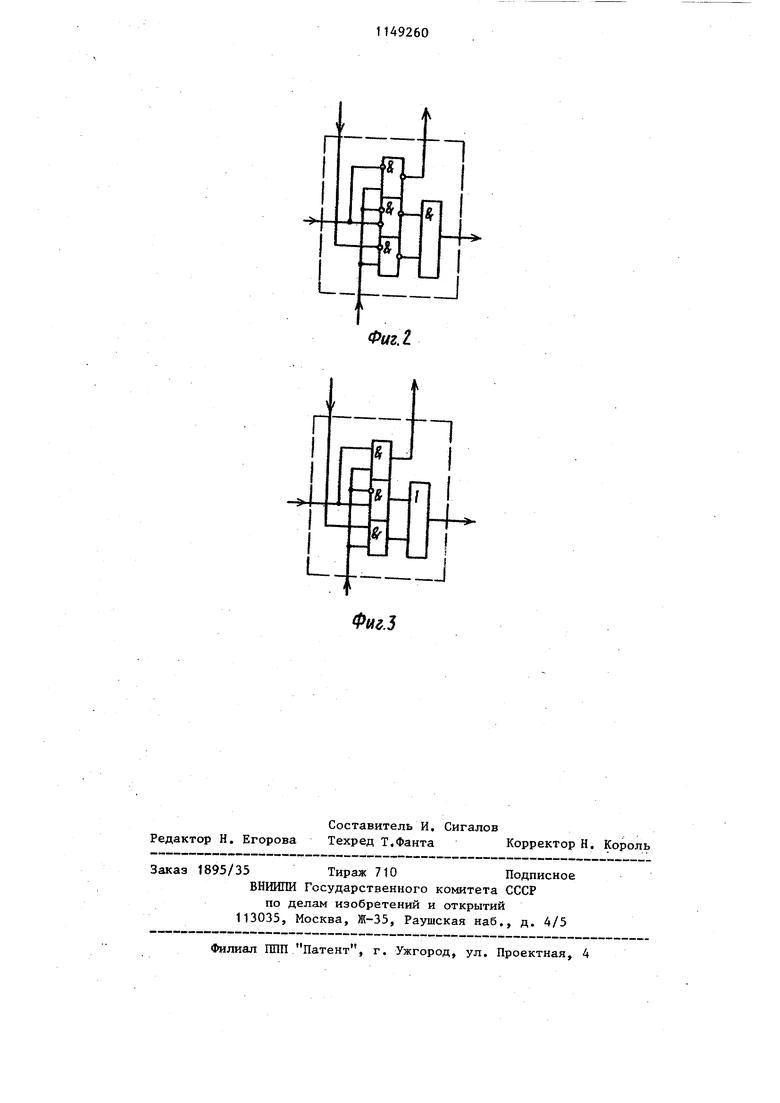

Предлагаемое устройство может быть реализовано при любой регулярной реализации распределителя импульсов (разница заключается в требуемом 0 количестве коммутаторов в каждом

блоке 7-i) по числу пар входов-выходов переноса в разряде распределителя и.хг;ульсов 6-i. Причем с входами каждого коммутатора соединяются 5 одноименные выходы данного и предыдущего (последующего), если перенос в данньй разряд по данному входу происходит из последующего разряда распределителя импульсов. 0 Схемная реализация коммутатора для случая импульсов отрицательной полярности показана на фиг. 2, а для случая импульсов положительной полярности - на фиг. 3. 5 Счетчик 1 импульсов по модулю (К+1) выполняется в виде счетчика на log2(K-i-2)f разрядов, выходы которого соединены с входами двух элементов И, формирующих на выходах 0 единичный потенциал, когда счетчиком сосчитано К (К+1) импульсов, соединяется прямыми входами с выходами счетчика, вес которых равен весу ненулевых разрядов двоичного 5 представления числа К (К+1), а инверсными входами - с остальными разрядами счетчика. Выход элемента И, формирующего на выходе единичньй

потенциал, когда счетчиком сосчитано К импульсов, является первым выходом накопителя, а выход другого элемента И - его вторым выходом.

Блок 4 синхронизации реализует следующие логические функции:

на первом выходе (у, v у) УЗ

на втором выходе (у v Уг ) УЗ где У,,У2 сигнал на первом и втором входах соответственно;УЗ - сигнал на тактовом входе

Функционирование устройства для . обнаружения ошибок в параллельном п-разрядном коде с постоянным весом К происходит следующим образом.

В.исходном состоянии счетчик 1 по модулю (К+1), разряды 6 распределителя импульсов и триггер 3 сброшены. При этом в единичном состоянии находится разряд 6-(п+2) распределителя импульсов.

Разряды 6 распределителя импульсов с блоками 7 коммутации и элементом ИЛИ 2 образуют управляемый сканирующий мультиплексор, который в течение цикла работы формирует на выходе элемента ИЛИ 2 последовательность из m импульсов, где m - число единичных потенциалов на входах устройства, т.е. преобразует количество единичных потенциалов на входах в унитарный код. Последнее осуществляется следующим образом. Если на входную шину XJ подан нулевой потенциал, то блок 7-i коммутации отключает входы - выходы разряда 6...i распределителя импульсов и работает в режиме трансляции сигналов, поступакицих на входы коммутаторов с выходов блоков 7-(i+1) и 7-(i-1) коммутации на входы блоков 7-(i-l) и 7-(i+1) коммутации соответственно. Если xj 1, то блок 7-i коммутации подключает входы-выходы разряда 6 распределителя импульсов к входам-выходам коммутаторов блоков 7-(i-1)и 7-(i+lX В результате все разряды распределителя импульсов, для которых , оказываются отключенными и образуется распределитель импульсов только из разрядов, для которых .

При подаче тактовых импульсов осуществляется последовательное формирование на выходе элемента ИЛИ 2 импульсов по числу разрядов входного кода, для которых х; 1. Таким

образом исключается опрос входных шин, для которых Xj О, что и обеспечивает повьшение быстродействия. Формируемые на выходе элемента 5 ИЛИ 2 импульсы считаются счетчиком 1 импульсов по модулю (К+1). Функционирование таким образом происходит либо до момента, когда счетчиком 1 будет сосчитан (К+1) импульс, 0 Iп

чтЪ имеет место при Z х, К, либо

1

дд опроса всех входов Х , при

. t X, к.

5 V

В первом случае в момент прихода на вход счетчика 1 (К+1)-го импульса единичньй потенциал пропадает на его первом выходе-и появляется

0 на втором выходе, поступая на вход блока 4 синхронизации. При этом на выходе блока 4 синхронизации, соединенном с входом синхронизации триггера 3, формируется разрешающий

5 потенциал, и в триггер 3 записывается нулевой потенциал с первого выхода счетчика 1 импульсов по модулю (К+1). По окончании тактового импульса разрешающий потенциал на

0 выходе блока 4 синхронизации, соединенном с входом синхронизации триггера 3, пропадает, а на его втором выходе появляется сигкал сброса, поступающий на входы сброса

5 разрядов 6 распределителя импульсов и вход начальной установки счетчика 1 импульсов по модулю (К+1), устанавливая их в «сходное состояние.После сброса счетчика 1 импульсов единичный потенциал на его втором выходе пропадает и сигнал сброса на втором выходе блока 4 синхронизации оканчивается.

п

Во втором случае Z х с к единичный потенциал на втором выходе счетчика 1 импульсов по модулю (К+1). не появляется. Единичный потенциал поступает на вход блока 4 синхронизации с выхода разряда 6-(п+1) распределителя импульсов после опроса последнего входа х: 1 в момент прихода очередного тактового импульса. При этом в течение дли-

5 тельности тактового импульса происходит запись в триггер 3 потенциала с первого выхода счетчика 1 импульсов по модулю (К+1) (нулевого, если

т х к и единичного, если 21 ),

А по его окончании сброс разрядов 6 распределителя импульсов и начальная установка счетчика 1 импульсов no модулю (К-«-1). После сброса разряов 6 распределителя импульсов единичный потенциал на выходе разряда 6-(п+1) пропадает и сигнал сброса оканчивается.

Цикл работы устройства окончен, в триггер 3 записан результат. Все локи возвращены в исходное состояние. Со следующего такта начинается новый цикл работы.

Предлагаемое устройство обеспечивает повьшение быстродействия. Цикл работы известного устройства составляет N, (п+1) такт. Цикл работы предлагаемого устройства

составляет

fnи

§1 Х-+1при Z х- g к «ftt 1

К+1при X ; К

тактов.

14926010

В таблице приведены сравнительные данные числа тактов цикла работы известного и предлагаемого устройств для случая п 10 и К 5 5 для различных входных кодов.

Для рассмотренного примера достигается повышение быстродействия более в чем в два раза.

...

Таким образом П едлагаемое устройство для обнаружения ошибок обеспечивает повьш1ение быстродействия.

Г

1

U

Фиг. I

-I-

j

IJ

Фи.З

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Патент США № 3851307, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Авторское свидетельство СССР. | |||

| 1972 |

|

SU428385A1 | |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-04-07—Публикация

1982-06-22—Подача