1

Изобретение относится к вычислительной технике, предназначено для распределения сигналов последовательно по п вы.ходным ипгпам при большом количестве помех.

Известны распределители, содержащие в каждом разряде триггер с раздельными входами и две схемы «И-НЕ. Выход иервой схемы «И-НЕ соединен с единичным входом триггера данного разряда, с иулевым входом триггера предыдущего разряда, со входом первой схемы «И-НЕ последующего разряда и со входом второй схемы «PI-НЕ данного разряда, выход которой соединен со входом первой схемы «И-НЕ данного разряда. Единичный выход триггера данного разряда соединен со входом второй схемы «И- НЕ последующего разряда. Один из входов первых схем «И-НЕ всех разрядов соединен с шиной тактирования, а единичный вход триггера первого разряда и нулевые входы триггеров всех последующих разрядов соединены с шиной начальной установки. Нулевые входы триггера данного разряда соединены с нулевыми выходами триггеров предь1дуи1его и последующего разрядов. Едииичиые выходы триггеров соедииены с потеппиальными выходами устройства, а выходы первых схем «И- НЕ - с импульсными выходами.

Цель изобретеиия - ускорение восстановления исходного состояния распределителя при случайных сбоях.

Предлагаемый раснределптель отличается тем, что входы донолпительной схемы «И- НЕ соедииепы с иулевыми вы.ходами триггеров п-1 младших разрядов, а выход связан с едииичиым входом триггера я-ного разряда, пулевой выход триггера данного разряда соединен с нулевыми входами триггеров всех младших разрядов.

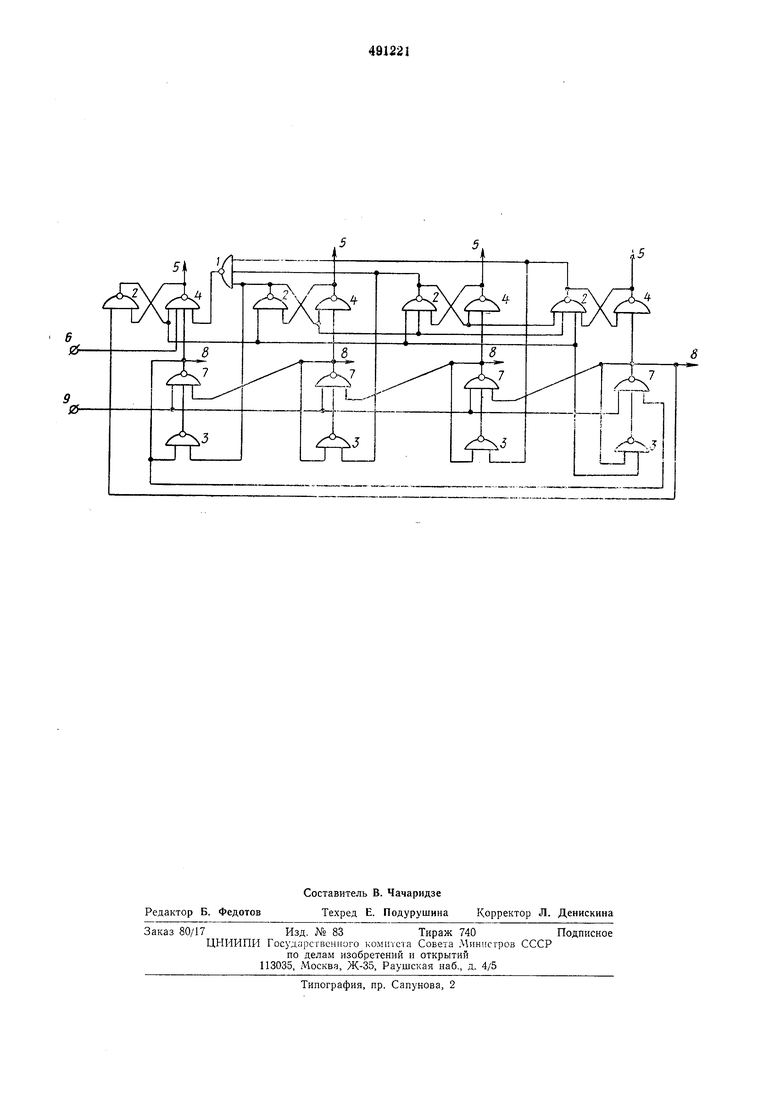

С.хема распрелтелителя представлена на чертеже.

Входы доиолиительной схемы 1 соединены с выходами схемы «И-НЕ 2, которые образуют нулевые выходы триггеров младших разрядов, а выход связан с еднничным входом триггера последнего разряда. Выход схемы «И-НЕ 2, который образует нулевой выход триггера данного разряда, соединен с нулевыми входами триггеров всех младших разрядов и со входом с.хемы «И-НЕ 3 последующего разряда. Выходы схем «И-НЕ 4, образующие единичные выходы триггеров, соединены с потенцнальиыми выходами 5 устройства. Шина начальной установки 6 подключена к едииичному входу триггера последнего разряда. Выход схемы «И-НЕ 7 соединен с едииичны.м в.ходом триггера данного разряда, со входом схемы «И-НЕ 7 последующего разряда, со входом схемы «И- НЕ 3 данного разряда и с импульсным выходом 8 устройства, а входы соединены с шиной тактирования 9 и выходом схемы «И- НЕ 3 данного разряда. Выход схемы «И-НЕ 7 первого разряда соединен с нулевым входом триггера последнего разряда.

Работает распределитель следующим образом.

В начальный момент времени входного сигнала, подаваемого на шину тактирования 9, нет, и триггер последнего разряда устанавливается в единичное состояние. Следовательно, на выходе схемы «И-НЕ 2 последнего разряда оказывается сигнал, равный логическому нулю, который устанавливает триггеры младших разрядов в нуль. В этом случае на выходах схем «И-НЕ 1, 2 последнего разряда, схем «И-НЕ 4 младших разрядов, схем «И-НЕ 3 всех разрядов, кроме первого, - логический нуль, на выходах схем «И-НЕ 4 последнего разряда, схем «И- НЕ 2 младших разрядов, схем «И-НЕ 7, 3 первого разряда - логическая единица.

С появлением входного сигнала на выходе схемы «И-НЕ 7 первого, разряда появляется сигнал, соответствующий логическому нулю, который устанавливает триггер последнего разряда в нуль, а триггер первого разряда - в единицу. Носкольку выход схемы «И-НЕ 7 первого разряда, кроме того, связан со схемой «И-НЕ 7 второго разряда и такой же схемой первого разряда, то на выходах этих схем логический нуль не появляется, хотя триггеры последнего и второго разрядов изменяют свое состояние. Действительно, сигнал со схемы «И-НЕ 7 первого разряда поступает на схему «И-НЕ 7 второго разряда и такую же схему первого разряда до изменения значения сигналов с триггеров последнего и второго разрядов. Таким образом, единица из триггера последнего разряда переписывается в триггер первого разряда.

После окончания действия входного сигнала, на выходах схем «И-НЕ 4 старших разрядов, схем «И-НЕ 2 первого разряда, схем «И-НЕ 3 всех разрядов, кроме второго, оказывается логический нуль, а на выходах схем «И-НЕ 1, 2 старших разрядов, схем «И-НЕ 4 первого разряда, схем «И-НЕ 7, 3 второго разряда - логическая едипица. С появлением следующего входного сигнала

логический нуль появляется на выходе схемы «И-НЕ 7 второго разряда. Он устанавливает триггер второго разряда в единицу, а логический нуль, появившийся на выходе схемы «И-НЕ 2 второго разряда, устанавливает триггер первого разряда в нуль. Связи с выхода схемы «И-НЕ 7 второго разряда на входы схемы «И-НЕ 3 этого разряда и схемы «И-НЕ 7 третьего разряда препятствуют появлению на выходах этих схем логического нуля. Следовательно, единица из триггера первого разряда переписывается в триггер второго разряда и т. д. Когда все триггеры находятся в состоянии «нуль, срабатывает схема «И-НЕ 1, и триггер последнего разряда переходит в единицу, т. е. распределитель возвращается в исходное положение. В распределителе также не может существовать больше одного триггера, находящегося в

единичном состоянии.

Нредмет изобретения

Распределитель, содержащий в каждом разряде триггер с раздельными входами и две

схемы «И-НЕ, выход первой схемы «И- НЕ соединен с единичным входом триггера данного разряда, со входом первой схемы «И-НЕ последующего разряда и со входом второй схемы «И-НЕ данного разряда, выход которой соединен со входом первой схемы «И-НЕ данного разряда, нулевой выход триггера данного разряда соединен со входом второй схемы «И-НЕ последующего разряда, а выход первой схемы «И-НЕ

первого разряда соединен дополнительно с нулевым входом триггера п-ного разряда, один из входов первых схем «И-НЕ всех разрядов соединен с шиной тактирования, а единичный вход триггера п-ного разряда соединен с шиной начальной установки, единичные выходы триггеров соединены с потенциальными выходами устройства, а выходы первых схем «И-НЕ - с импульсными выходами устройства, отличающийся тем,

что, с целью ускорения восстановления исходного состояния при случайных сбоях, входы дополнительной схемы «И-НЕ соединены с нулевыми выходами триггеров п-1 младших разрядов, .а выход соединен с единичным входом триггера я-ного разряда, нулевой выход триггера данного разряда соединен с нулевыми входами триггеров всех младших разрядов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Делитель частоты на 3,5 | 1975 |

|

SU539382A1 |

| Распределитель | 1977 |

|

SU680171A1 |

| Сумматор | 1974 |

|

SU541173A2 |

| Распределитель | 1982 |

|

SU1077051A1 |

| Следящий аналого-цифровой преобразователь | 1979 |

|

SU799129A1 |

| УСТРОЙСТВО ДЛЯ ВЫБОРА ДОСТОВЕРНОЙ ИНФОРМАЦИИ | 1973 |

|

SU394790A1 |

| Делитель частоты с дробным переменным коэффициентом деления | 1974 |

|

SU506130A1 |

| Устройство для вычисления элементарных функций | 1984 |

|

SU1168930A1 |

| Счетчик с переменным коэффициентом счета | 1986 |

|

SU1401600A1 |

| Распределитель | 1981 |

|

SU959278A1 |

Авторы

Даты

1975-11-05—Публикация

1974-02-15—Подача