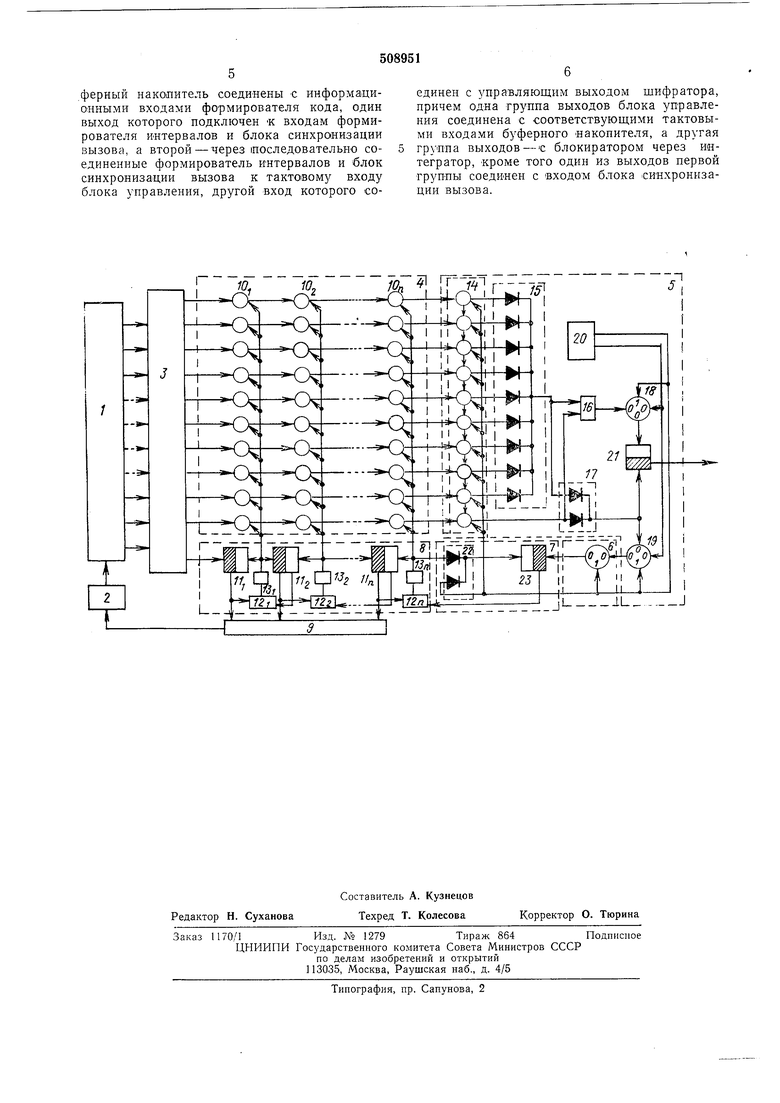

же -количество п элементарных блоков управления, состоящих из триггеров Иь Ib,..., Пп, схем 12, 122,..., 12п совпадения и элементов 13ь 132,..., 13„ задержки. Формирователь 5 кода состоит из регистра 14 сдвига, девятивходовой собирательной схемы 15, схемы 16 совпадения, собирательной -схемы 17, схем 18 и 19 запрета, тактового генератора 20 и выходного зстройства 21. Блок 7 синхронизации вызова состоит из собирательной схемы 22 и триггера 23.

Датчик кода Морзе работает следующим образом.

При нажатии одной из клавиш блока 1 ввода по одному из его выходов, соответствующему выбранному знаку, в шифратор 3 поступает сигнал, который распределится по десяти его выходам в соответствии с (промежуточным десятиразрядным кодом. С выходов шифратора 3 код поступает на соответствующие входы буферного накопителя 4 и залисывается -в запоминающую линейку 10, ячейки которой в соответствии с кодом записываемого слова переходят в состояние «1. Одновременно с каждым вводимым знаком в шифратор 3 с его управляющего выхода производится запуск блока 8 управления. При этом триггер 111 срабатывает и выдает сигнал «I на схему 12i совпадения, на другом входе которой уже имеется сигнал «1 от последующего триггера Ib. Схема 12i совпадения срабатывает и через элемент 13i задержки производит считывание информации с запоминающей линейки lOi буферного накопителя 4 и запись ее в последующую заломинающую линейку 102. Одновременно триггер 111 возвращается в исходное состояние, и выводится из исходного состояния триггер 112, который тем самым обеспечивает совпадение сигналов на следующей схеме 122 совпадения с аналогичным продвижением информации в следующую запоминающую линейку. Такое продвижение информации осущест1вляется вплоть до записи в последнюю запоминающую линейку 10п с соответствующей работой каждого элементарного блока 8 управления. Элементы 13ь 132,..., 13п задержки необходимы для того, чтобы запись информации в запоминающие линейки буферного накопителя 4 произошла раньше, чем поступит на них сигнал считывания от элементарных блоков блока 8 управления. Считывание с последней запоминающей линейки Ютг производится по сигналу от триггера 23 блока 7 синхронизации вызова, которая в свою очередь получает сигнал от формирователя 6 интервалов. Необходимая скорость выхода (формирование) кода из датчика в знаках в минуту в соответствии со средней скоростью работы оператора устанавливается регулировкой частоты тактового генератора 20. При этом благодаря буферной памяти допустимы некоторые отклонения скорости ввода от скорости вывода, вызываемые как неравномерностью кода, так и неравномерностью работы оператора на клавиатуре. Блок 7 синхронизации вызова исключает совпадение импульсов с последней запоминающей линейки 10 буферного накопителя 4 и импульса считывания от тактового генератора 20, поступающих на регистр 14 сдвига, так как совпадение этих импульсов привело бы к их взаимной компенсации и, следовательно, потере вводимого в регистр 14 сдвига кодового слова.

Таким образом, продвижение информации с одной запоминающей линейки буферного накопителя 4 на другую происходит по мере считывания ее с последней запоминающей линейки 10„ по сигналу от блока 7 синхронизации вызова. В случае резкого превышения скорости ввода, т. е. при заполнении всех запоминающих линеек буферного накопителя 4, срабатывает блокиратор 2, управляемый интегратором 9, когда все триггеры 11, Ib, .., Пи блока 8 управления выйдут из исходного состояния. При работе датчика тактовый генератор 20 по одному выходу производит запись «1 в схемы 18, 19 запрета и формирователь 6 интервалов, продвигает в регистре 14 сдвига записанную в нем информацию и приводит триггер 23 через собирательную схему 22 в исходное состояние. С другого выхода такто;вый генератор 20 -производит считывание записанной «1 со схем 18 и 19 запрета. При считывании со схемы 18 запрета выходное устройство 21 приводится в бестоковое состояние. В случае совпадения сигналов на входах схемы 16 совпадения последняя выдает сигнал, которым запрещается запись «1 в схему 18 запрета, и выходное устройство 21 не приводится в бестоковое состояние, формируя при этом тире. При считывании со схемы 19 запрета сигнал с ее выхода через формирователь 6 интервалов выводит триггер 23 из исходного состояния, который тем самым дает разрешение на запись информации в регистр 14 сдвига с последней запоминающей линейки 10и буферного накопителя 4 и одновременно с записью информации в регистр 14 сдвига приводится через собирательную схему 22 в исходное состояние. Сигнал с выхода схемы 19 запрета поступает на формирователь 6 интервалов лишь в случае отсутствия информации в регистре 14 сдвига, т. е. при отсутствии сигнала запрета на схему 19 запрета от собирательной схемы 17.

Ф о р м у л а изобретения

Датчик КОда Морзе, содержащий последовательно соединенные блок ввода, управляющий ВХОД которого соединен с блокиратором, шифратор и формирователь кода, отличающийся тем, что, с целью повышения точности формирования элементов кода независимо от скорости и неравномерности работы манипулятора, введены буферный накопитель, блок управления, блок синхронизации вызова, формирователь интервалов и интегратор, при этом выходы шифратора через буферный накопитель соединены -с информационными входами формирователя кода, один выход которого нодключен К входам формирователя интервалов и блока синхронизации вызова, а второй-через тоследовательн-о соединенные формирователь интервалов и блок синхронизации вызова к тактовому входу блока управления, другой вход которого соединен с управляющим выходом шифратора, нричем одна группа выходов блока управления соединена с соответствующими тактовыми входами буферного накопителя, а другая группа выходов - с блокиратором через интегратор, -кроме того один из выходов первой группы соединен с входом блока синхронизацин вызова.

| название | год | авторы | номер документа |

|---|---|---|---|

| Датчик кода Морзе | 1981 |

|

SU1001496A1 |

| Датчик телеграфного кода | 1984 |

|

SU1210230A1 |

| Преобразователь равномерного кода в код Морзе | 1984 |

|

SU1229973A2 |

| Преобразователь равномерного кода в код Морзе | 1983 |

|

SU1107310A1 |

| ВСЕСОЮЗНАЯ | 1973 |

|

SU372729A1 |

| Устройство автоматизированной подготовки программ для станков с ЧПУ | 1986 |

|

SU1354160A1 |

| Устройство для передачи информации псевдослучайными сигналами | 1986 |

|

SU1392625A1 |

| Датчик кода морзе | 1979 |

|

SU886294A2 |

| Устройство для ретрансляции речевых сигналов | 1990 |

|

SU1830627A1 |

| Устройство для формирования кода морзе | 1973 |

|

SU523532A1 |

J

Авторы

Даты

1976-03-30—Публикация

1973-04-06—Подача