Этот сигнал поступает на адресный вход блока 3 и обеспечивает запись кода,который уЬтановлен во входном регистре 2.Пропадание информации на запись исключается вследствие того, что она временно хранится во входном

Изобретение относится к технике связи и может использоваться для построения датчиков телеграфных кодов, в частности датчиков кода Морзе.

Цель изобретения - повышение точности формирования телеграфного кода.

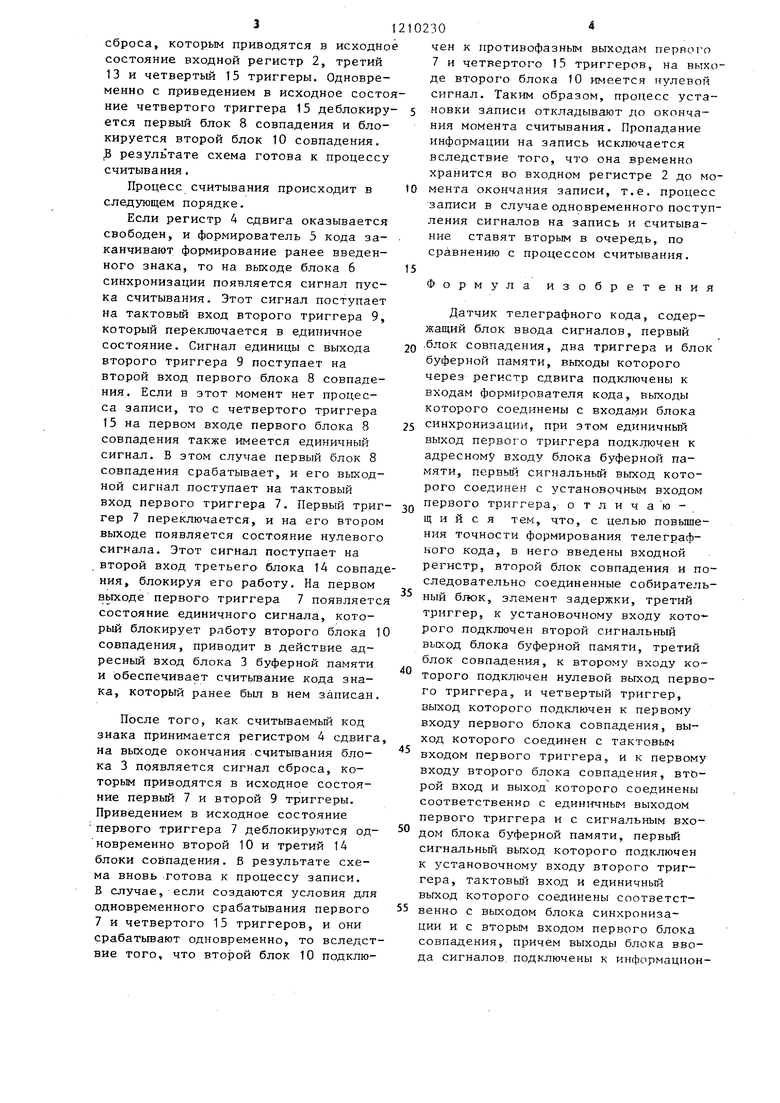

На чертеже представлена структурная электрическая схема предложенного датчика.

Датчик телеграфного кода содер- Iжит блок 1 ввода сигналов, входной регистр 2, блок 3 буферной памяти, регистр 4 сдвига, формирователь 5 |кода, блок 6 синхронизации, первый триггер 7, первьй блок 8 совпадения, второй триггер 9, второй блок 10 совпадения, собирательньй блок 11, элемент 12 задержки, третий триггер 13, третий блок 14 совпадения и четвертьй триггер 15.

Датчик работает следующим образом.

При записи оператор с помощью блока 1 вводит необходимый знак. С выхода блока 1 ввода сигналов код выбранного знака поступает на входной регистр 2. Последний может быть выполнен в виде статических триггеров, количество которых соответствует разрядности кода на выходе блока 1. Сигналы набранного кода параллельно поступают на информационный вход блока 3 буферной памяти и на собирательньй блок 11, который необходим для того, чтобы независимо от разрядности набранного кода знака, был произведен пуск датчика на процесс записи. Сигнал с выхода собирательного блока 11 поступает на вход элемента 12 задержки. Элемент 12 задержки может быть выполнен в йиде ждущего мультивибратора (формирователя одиночного импульса) и необходим для

того, чтобы исключить влияние на запись переходных процессов блока t ввода сигналов. Переходные процессы в блоке 1 ввода сигналов проявляются 5 в виде дребезга контактов клавиатуры, которая является обычной составной частью блоков ввода сигналов. После завершения переходных процессов в блоке 1 ввода сигналов задним фрон 0 том импульса элемента 12 задержки переключается в единичное состояние третий триггер 13. Сигнал единицы с выхода третьего триггера 13 постуЬа- ет на первый вход третьего блока 14

tS совпадения. Если в этот момент нет процесса считывания, то с первого триггера 7 на втором-входе третьего блока 14 совпадения также имеется единичный сигнал, В этом случае тре20 тий блок 14 совпадения срабатьшает, и его выходной сигнал поступает на тактовый вход четвертого триггера 15. Последний переключается, и на его втором выходе появляется нулевой

25 сигнал. Этот сигнал поступает на первый вход первого блока 8 совпадения, блокируя его работу, и на первый вход второго блока 10 совпадения. Если в этот момент нет процесса счи30 тыдания, то с первого выхода первого

триггера 7 поступает нулевой сигнал 1

на первый вход второго блока 10 совпадения. Второй блок 10 совпадения срабатьтает при наличии на его вхо35 дах нулевых сигналов. На выходе второго блока 10 совпадения при этом появляется сигнал установки записи. Этот сигнал поступает на адресньй вход блока 3 буферной памяти и обес40 печивает запись кода, который установлен во входном регистре 2. После того,как прием кода знака заканчивается, на выходе окончания записи блока 3 буферной памяти появляется сигнал

регистре 2 до момента окончания записи. Если одновременно поступают сигналы на запись и считьгоание, то процесс записи будет вторым по сравнению с процессом считывания , I ил о

3

сброса, которым приводятся в исходно состояние входной регистр 2, третий 13 и четвертый 15 триггеры. Одновременно с приведением в исходное состоние четвертого триггера 15 деблокируется первый блок 8 совпадения и блокируется второй блок Ю совпадения. JB результате схема готова к процессу считывания.

Процесс считывания происходит в следующем порядке.

Если регистр 4 сдвига оказывается свободен, и формирователь 5 кода заканчивают формирование ранее введенного знака, то на выходе блока б синхронизации появляется сигнал пуска считывания. Этот сигнал поступает на тактовый вход второго триггера 9, который переключается в единичное состояние. Сигнал единицы с выхода второго триггера 9 поступает на второй вход первого блока 8 совпадения. Если в этот момент нет процесса записи, то с четвертого триггера 15 на первом входе первого блока 8 совпадения также имеется единичный сигнал. В этом случае первый блок 8 совпадения срабатывает, и его выходной сигнал поступает на тактовый вход первого триггера 7. Первый триггер 7 переключается, и на его втором выходе появляется состояние нулевого сигнала. Этот сигнал поступает на второй вход третьего блока 14 совпадния, блокируя его работу. На первом вьгходе первого триггера 7 появляетс состояние единичного сигнала, который блокирует работу второго блока 1 совпадения, приводит в действие адресный вход блока 3 буферной памяти и обеспечивает считьгоание кода знака, который ранее был в нем записан.

После того, как считываемьй код знака принимается регистром 4 сдвига на выходе окончания считывания блока 3 появляется сигнал сброса, которым приводятся в исходное состояние первый 7 и второй 9 триггеры. Приведением в исходное состояние первого триггера 7 деблокируются одновременно второй 10 и третий 14 блоки совпадения. В результате схема вновь готова к процессу записи. В случае, если создаются условия для одновременного срабатывания первого 7 и четвертого 15 триггеров, и они срабатьшают одновременно, то вследствие того, что второй блок 10 подклю: 0

чен к противофазным выходам первого 7 и четвертого 15 триггеров, на вьгх о- де второго блока 10 имеется ттулевой сигнал. Таким образом, процесс установки записи откладывают до окончания момента считывания. Пропадание информации на запись исключается вследствие того, что она временно хранится во входном регистре 2 до момента окончания записи, т.е. процесс записи в случае одновременного поступления сигналов на запись и считывание ставят вторым в очередь, по сравнению с процессом считывания.

Формула изобретения

Датчик телеграфного кода, содержащий блок ввода сигналов, первый

.блок совпадения, два триггера и блок буферной памяти, выходы которого через регистр сдвига подключены к входам формирователя кода, выходы которого соединены с входами блока

синхронизации, при этом единичный выход первого триггера пoдкJ7Ючeн к адресному входу блока буферной памяти, первый сигнальньй выход которого соединен с установочным входом первого триггера, о тлича ю- щ и и с я тем, что, с целью повьше- ния точности формирования телеграфного кода, в него введены входной регистр, второй блок совпадения и последовательно соединенные собирательный блок, элемент задержки, третий триггер, к установочному входу кото рого подключен второй сигнальный вьсх од блока буферной памяти, третий блок совпадения, к второму входу которого подключен нулевой выход первого триггера, и четвертый триггер, выход которого подключен к первому входу первого блока совпадения, выход которого соединен с тактовым входом первого триггера, и к первому входу второго блока совпадения, второй вход и выход которого соединены соответственно с единичным выходом первого триггера и с сигнальным входом блока буферной памяти, первый сигнальньш выход которого подключен к установочному входу второго триггера, тактовый вход и единичный выход которого соединены соответствеяно с выходом блока синхронизации и с вторым входом первого блока совпадения, причем выходы блока ввода сигналов, подключены к информацион

$1210230 6

ным BxoAasvj входного регистра, выходы установочным входом входного регистра, которого подключены к информационным выходы которого подключены к входам входам блока буферной памяти, второй собирательного блока, и с установоч- сигнальный выход которого соединен с ным входом четвертого триггера.

| название | год | авторы | номер документа |

|---|---|---|---|

| Датчик кода морзе | 1973 |

|

SU508951A1 |

| Датчик телеграфного кода | 1985 |

|

SU1261127A1 |

| Датчик кода Морзе | 1981 |

|

SU1001496A1 |

| Устройство для сопряжения вычислительной машины с телеграфными каналами связи | 1986 |

|

SU1392571A1 |

| Устройство для отображения информации | 1985 |

|

SU1354183A1 |

| Многокоординатный цифровой интерполятор | 1984 |

|

SU1200246A1 |

| Устройство для контроля линейных динамических объектов | 1990 |

|

SU1795422A1 |

| Устройство для отображения информации | 1984 |

|

SU1229802A1 |

| Буферное запоминающее устройство | 1986 |

|

SU1374279A1 |

| Устройство для редактирования | 1982 |

|

SU1117669A1 |

Изобретение относится к технике связи. Цель изобретения - повышение точности формирования Телеграфного кода. Датчик телеграфного кода содержит блок 1 ввода сигналов, входной регистр 2, блок 3 буферной памяти, регистр 4 сдвига, формирователь 5 кода, блок 6 синхронизации, первый триггер (т) 7, первый блок совпадения (ВО) 8, второй Т 9, второй БС 10, собирательный блок (СБ) 11, элемент 12 задержки, третий Т 13, третий БС 14, четвертый Т 15. Цель достигается введением входного регистра 2, БС 10 и последовательно соединенных СБ 11, элемента 12 задержки, Т 13, к которому подключен выход блoka 3 буферной памяти, БС 14, к которому подключен нулевой выход Т 7, и Т 15. СБ 11 необходим для того, чтобы независимо от разрядности набранного кода знака был произведен пуск датчика на процесс записи. Элемент 12 за- держки необходим для того, чтобы исключить влияние на запись переходных процессов блока 1. БС 10 срабатывает при наличии на его входах нулевых сигналов, на его выходе появляется сигнал установки записи. § (Л

| Датчик кода Морзе | 1981 |

|

SU1001496A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1986-02-07—Публикация

1984-08-09—Подача