(54) УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ КОНТРОЛЬНОГО

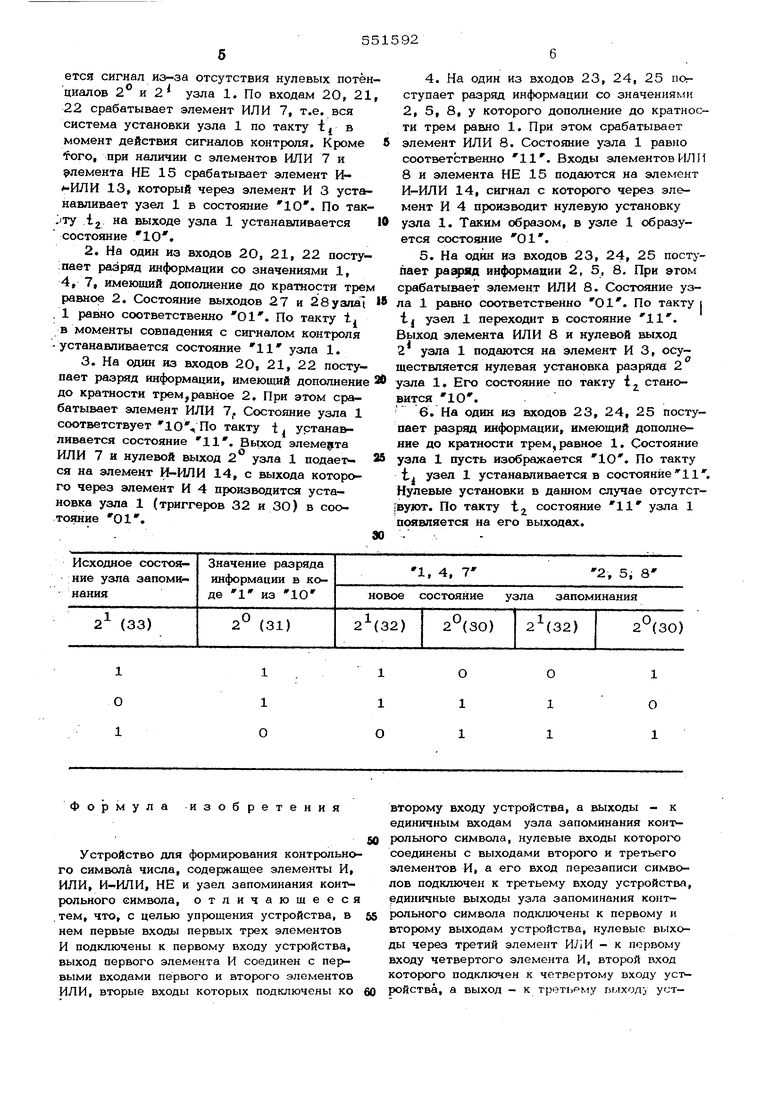

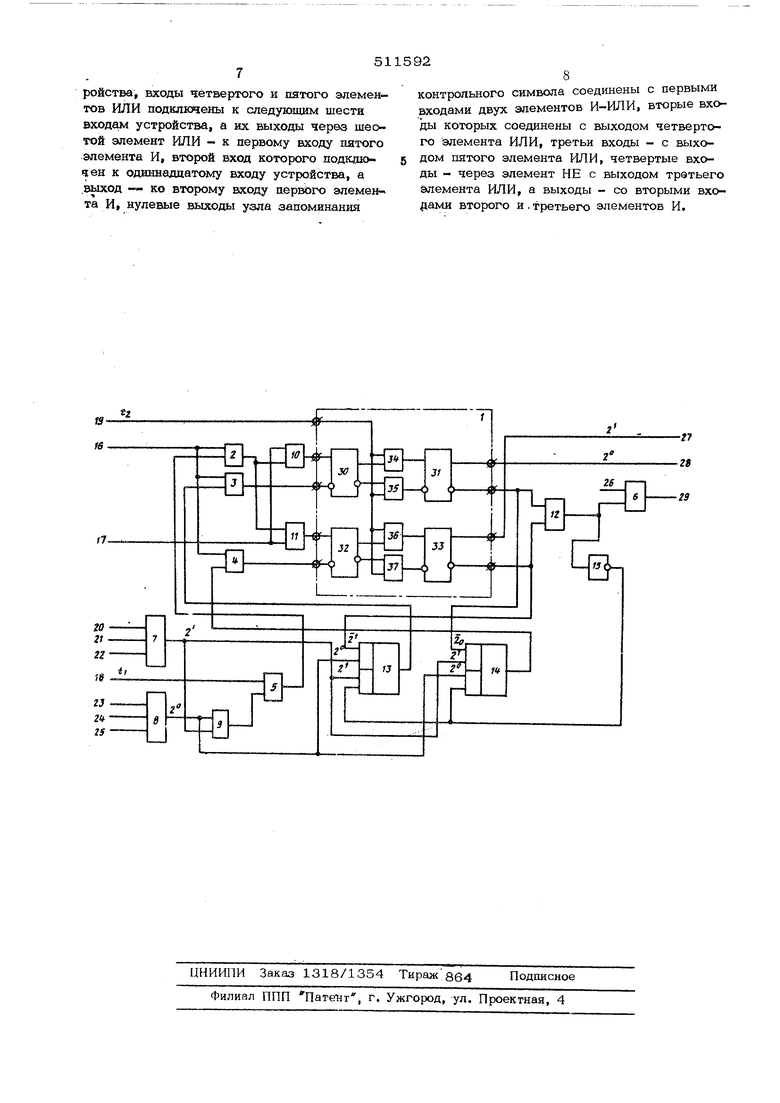

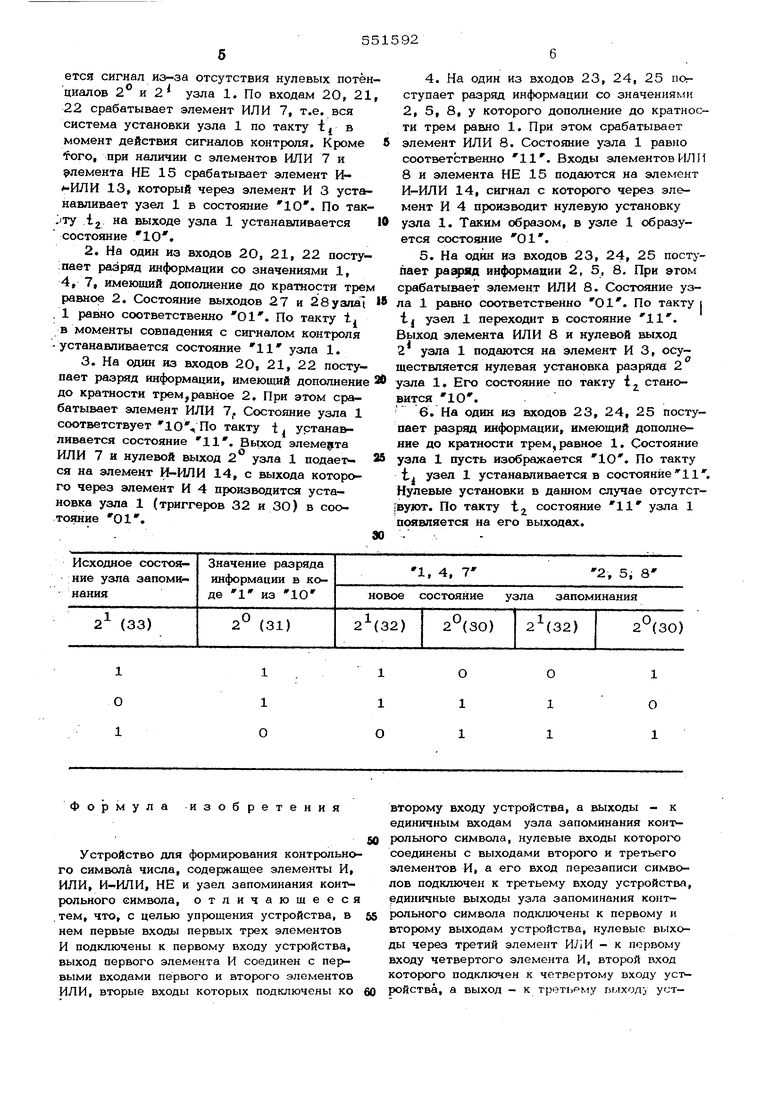

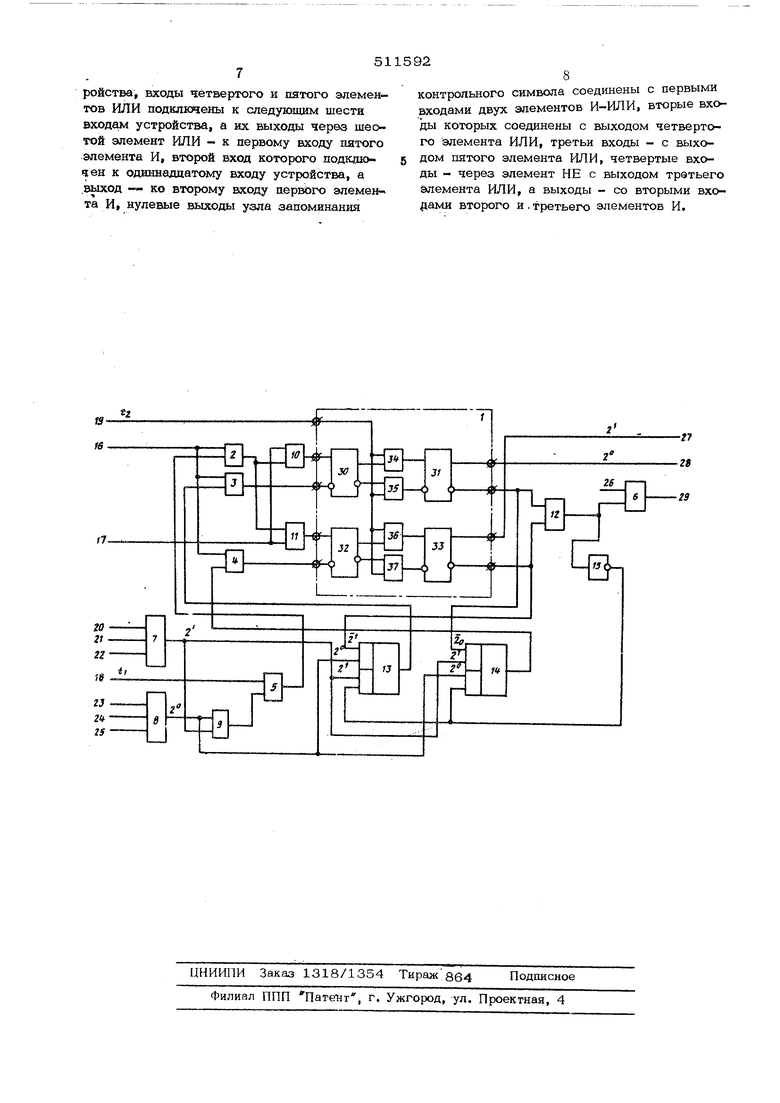

СИМВОЛА ЧИСЛА 2-6, элементов ИЛИ 7-12, элементов ИИЛИ 13, 14, элемента НЕ 15. На вход 16 подаются синхроимпульсы раарвдов числа, на вход 17 - начальная установка (запись тройки), иа вход 18 - , тактовые импульсы ij, синхронные с разряд ми числа, на вход 19 - тактовые импульсы tj, следующие в промежутках мезвду t , на вход 20, 21, 22 потенциалы цифр 1, 4, 7, на входы 23, 24, 25 - потенциалы, , цифр 2, 5, 8. На вход 26 поступает сигнал опрос сбоя На выходы 27, 28 выдаются 2 , 2 конт рольного символа, на выход 29 - сигнал сбоя.. Устройство производит форми 9ование конролшого символа и ксжтроль правильности его обработки. Для этого используется принЬип кратности трем , заключающийся в том что величина контрольного символа должна дополнять число до кратности трем. При nei вичном вводе чисел устройство производит формирование контрольного символа. При вычислениях и передачах чисел в ус-р ройстве аналогично формируется контрольный символ и осуществляется контроль получёвн ного контрольного символа на равенство егО тройке, означающей арвввльность обработки информации и вычисяеиий. Устройство представляет собой вакапливаюшую схему, состояние которой изменяет ся при последовательном поступлении разрядов контролируемой} числа. Ох:то1гаие этой схемы хранится в двоичном- коде (2, 2 Узел 1 запоминания может, , соо- тоять из двух пар триггеров 30, 31 и 32, 33 и элементов И 34, 35, 36, 37. На три герах 30, 31 запоминается 2 , а на триггерах 32, 33 - 2 контрольного символа. В этот узел по двум., его входам зщшсывается контрольный символ 2° или 2 , по дру гим двум входам стирается значение 2 или 2 . Кро)е того, имеется вход перезаписи контрольных символов для анализа последуюшего его значения. Узел выдает 2, 2° и Z, 2 контрол ного символа. Контрольный символ формируется комбинационным образом. Величина этого символа определяется значением разряда контролируемого числа и состоянием узла запоминания контрюльного символа к моменту поступления этого разряда (см. таблицу). Состояние схемы запоминания ОО может быть в результате сбоя нлн отказа и выявляется при контроле. Новое состояние узла 1 устанавливается по прямым и инверсным шинам по наличию импульсов контроля на входе 16, поступак -ус на элементы И 2, 3 и 4, с выходов оторых сигналы передаются через элемен-; ь1 ИЛ1И 10 и 11. Перепись нового состояий узла 1 производится по такту t (вход19) через элементы И узла 1. Перед подачей числа в устройство по ходу 17 производится начальная установа узла 1 путем записи состояния три через элементы ИЛИ 10 и 11, т.е. запись двоичного кода 11. Далее при подаче каждого разряда чйсла, синхронизируемого сигналами контроля по :Входу 17, вырабатывается контрольный следующим образом: каждый разряд , имеющий некоторое дополнение до крат .ности 3, поступает в устройство в коде из 10. На: входы 20, 21, 22 поступают числа 1, 4, 7, а на входы 23, 24, 25числа 2, 5, 8. На элементе ИЛИ 7 объединяются числа 1, 4, 7, требующие одинакового дополнения до кратности - 2, на эл&менте ИЛИ 8 объединяются числа 2, 5, 8, требующие-дополнения до кратности трем-1. Общий сигнал, соответствующий разрядам информации, имеющим дополнения до Kpai ности трем, вырабатывается на элементе ИЛИ 9, объединяющим сигналы с элементов ИЛИ 7 и 8. Принцип установки узла 1 в необходимые состояния по сигналу контроля сводится к записи состояния в узел 1 .по такту t| в моменты контроля при наличии сигнала с элемента ИЛИ 9. Сигнал с выхода элемента ИЛИ 9 по такту t , поступающему со входа 18, запускает элемент И 5, от которого при наличии снгнала контроля на входе 16 срабатывает эло- . мент - И 2. Сигнал элемента И 2 через элементы ИЛИ 1О и 11 устанавливает узел 1 в состояние при этом запись нулёйв узел 1 осуществляется при помощи элементов 13, 14. При наличии снгна;Лов на входах элементов И-ИЛИ 13, 14 и сигнала контроля на входе 16 срабатывают элементы И 3 и 4, которые записывают нули в узел 1. Вьщача контрольного символа производится с выходов 27, 28 из узла 1. По окончании обработки числа в устройство поступает сигнал опрос сбоя на вход 26, при помощи которого выявляется отсутствие тройки в узле 1. Отсутствие тройки фиксируется при помощи элемента ИЛИ 12, срабатывающего хотя бы по одному из нулевых состояний узла 1, что оэначает сбойное состояние. С приходом сигнала опрос сбоя сэлемента И 6 выдаерся сигнал сбой. Возможные следующие BtipaaHi-oi работы устройства (см. таблицу): 1. На один из входов 20, 21. 22 поступает разряд информации со значениями 1, 4, 7, имеющий дополнение до кратности трем, равное 2. С выхода элемента НЕ 15 выда-г ется сигнал из-за отсутствия нулевых потен циалов 2° и 2 узла 1. По входам 20, 21 22 срабатывает элемент ИЛИ 7, т.е. вся система установки узла 1 по такту t в момент действия сигналов контроля. Кроме foro, при наличии с элементов ИЛИ 7 и элемента НЕ 15 срабатывает элемент 13, который через элемент И 3 устанавливает узел 1 в состояние 10. По такJiTy tj на выходе узла 1 устанавливается состояние 10. 2.На один из входов 20, 21, 22 поступает разряд информации со значениями 1, 4, 7, имеющий дополнение до кратности трем равное 2. Состояние выходов 27 и 28узла . 1 равно соответственно О1. По такту t. в моменты совпадения с сигналом контроля устанавливается состояние 11 узла 1. 3.На один из входов 20, 21, 22 поступает разряд информации, имеющий дополнение до кратности трем,равное 2. При этом срабатывает элемент ИЛИ 7,, Состояние узла 1 соответствует 10 , По такту t устанавливается состояние 11. Выход элемента ИЛИ 7 и нулевой выход 2° узла 1 подает ся на элемент И-ИЛИ 14, с выхода которого через элемент И 4 производится установка узла 1 (триггеров 32 и ЗО) в состояние 01. 4. На один из входов 23, 24, 25 погступает разряд информации со значениям 2, 5, 8, у которого дополнение до кратности трем равно 1. При этом срабатывает элемент ИЛИ 8. Состояние узла 1 равно соответственно 11. Входы элементов ИЛ 11 8 и элемента НЕ 15 подаются на элемент И-ИЛИ 14, сигнал с которого через элемент И 4 производит нулевую установку узла 1. Таким образом, в узле 1 образуется состояние 01. 5. На один из входов 23, 24, 25 поступает раяряп информации 2, 5, 8. При этом срабатывает элемент ИЛИ 8. Состояние узла 1 равно соответственно О1. По такту i tj узел 1 переходит в состояние 11. Выход элемента ИЛИ 8 и нулевой выход 2 узла 1 подаются на элемент И 3, осуществляется нулевая установка разряда 2 узла 1. ЕГО состояние по такту i. становится 10. 6. На один из входов 23, 24, 25 поступает разряд информации, имеющий дополнение до кратности трем, равное 1. Состояние узла 1 пусть изображается 1О. По такту ti узел 1 устанавливается в состояние 11 . Нулевые установки в данном случае отсутстГвуют. По такту состояние 11 узла 1 появляется на его выходах.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля информации по модулю три | 1976 |

|

SU634282A1 |

| Устройство для формирования контрольного кода числа | 1977 |

|

SU690484A1 |

| СБОЕУСТОЙЧИВОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 2015 |

|

RU2610264C1 |

| УСТРОЙСТВО ХРАНЕНИЯ И ПЕРЕДАЧИ ИНФОРМАЦИИ С ОБНАРУЖЕНИЕМ ДВОЙНЫХ ОШИБОК | 2009 |

|

RU2403615C2 |

| Устройство для счета метража и определения теоретического веса проката | 1975 |

|

SU595741A1 |

| УСТРОЙСТВО ХРАНЕНИЯ ИНФОРМАЦИИ С ОБНАРУЖЕНИЕМ ОДИНОЧНЫХ И ДВОЙНЫХ ОШИБОК | 2011 |

|

RU2450332C1 |

| Устройство для управления и микродиагностики | 1981 |

|

SU968815A1 |

| УСТРОЙСТВО ХРАНЕНИЯ И ПЕРЕДАЧИ ИНФОРМАЦИИ ПОВЫШЕННОЙ ДОСТОВЕРНОСТИ ФУНКЦИОНИРОВАНИЯ | 2010 |

|

RU2422923C1 |

| Устройство для контроля мажоритарных схем | 1983 |

|

SU1117643A1 |

| Устройство для контроля вычислений | 1972 |

|

SU470809A1 |

1 О 1

1 1 О Формула -изобретения Устройство для формирования контрольно го символа числа, содержащее элементы И, ИЛИ, И-ИЛИ, НЕ и узел запоминания контрольного символа, отличающееся тем, что, с целью упрощения устройства, в нем первые входы первых трех элементов И подключены к первому входу устройства, выход первого элемента И соединен с первыми входами первого и второго элементов ИЛИ, вторые входы которых подключены ко

1 о 1

О

о 1

1

1

1 второму входу устройства, а выходы - к единичным входам узла запоминания контрольного символа, нулевые входы которого соединены с выходами второго и третьего элементов И, а его вход перезаписи символов подключен к третьему входу устройства, единичные выходы узла запоминания контрольного символа подключены к первому и второму выходам устройства, нулевые выходы черюз третий элемент ИЛИ - к первому входу четвертого элемента И, второй вход которого подключен к четвертому входу ус ройства, а выход - к трет1.рму п(лходу устройства, входы четвертого и пятого элементов ИЛИ подключены к следующим шести входам устройства, а юс выходы через шестой элемент ИЛИ - к первому входу пятого элемента И, второй вход которого подклк чен к одиннадцатому входу устройства, а выход - ко второму входу первого элемента И, нулевые выходы узла запоминания

контрольного символа соединены с первыми входами двух элементов И-ИЛИ. вторые входы которых соединены с выходом четвертого элемента ИЛИ, третьи входы - с выходом пятого элемента ИЛИ, четвертые входы - через элемент НЕ с выходом третьего Элемента ИЛИ, а выходы - со вторыми входами второго и , третьего элементов И,

Авторы

Даты

1976-04-25—Публикация

1974-01-03—Подача