1

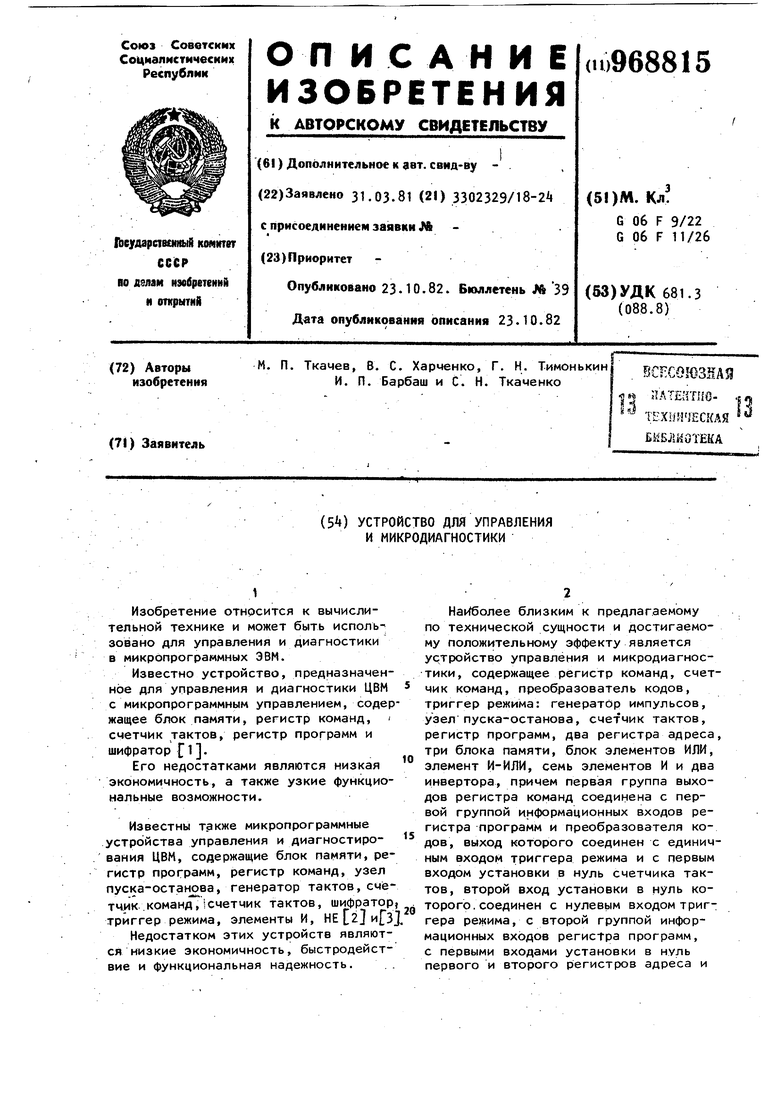

Изобретение относится к вычислительной технике и может быть исполь зовано для управления и диагностики в микропрограммных ЭВМ.

Известно устройство, предназначенное для управления и диагностики ЦВМ 5 с микропрограммным управлением, содержащее блок памяти, регистр команд, счетчик тактов, регистр программ и шифратор Г11-

Его недостатками являются низкая экономичность, а также узкие функциональные возможности.

Известны тэкже микропрограммные устройства управления и диагностирования ЦВМ, содержащие блок памяти, регистр программ, регистр команд, узел пуска-останова, генератор тактов, c4ieтчик.команд,Iсчетчик тактов, шифратор, триггер режима, элементы И,

Недостатком этих устройств являются низкие экономичность, быстродействие и функциональная надежность.

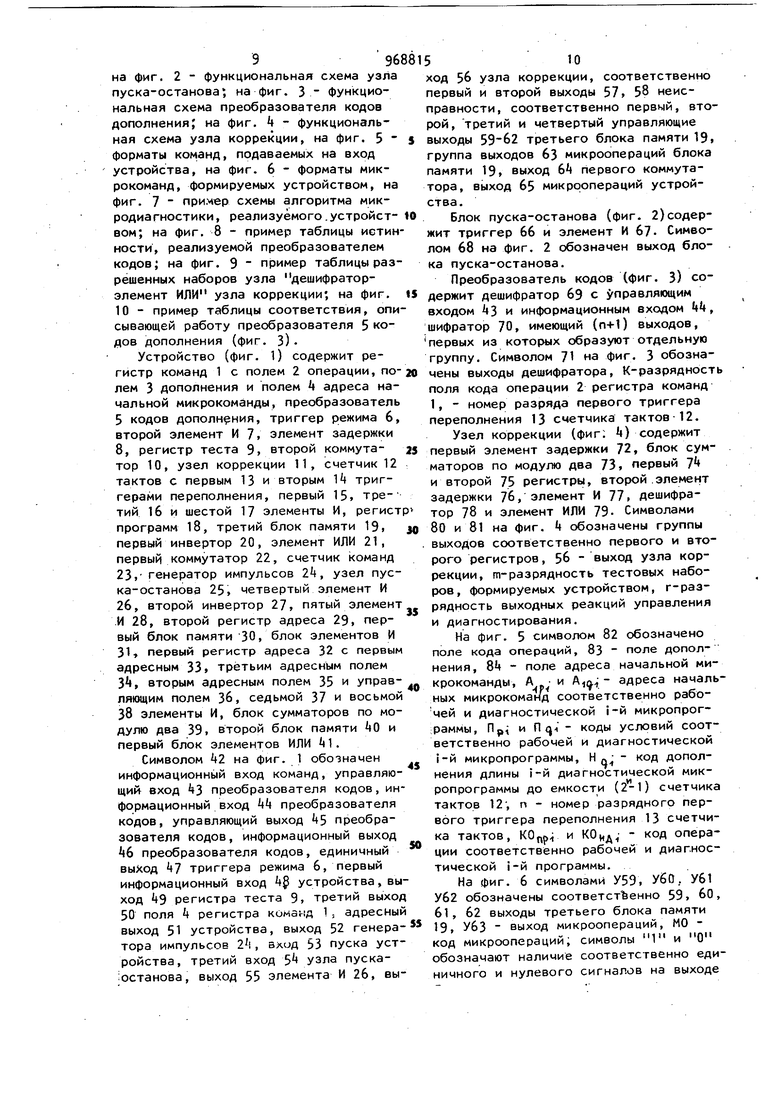

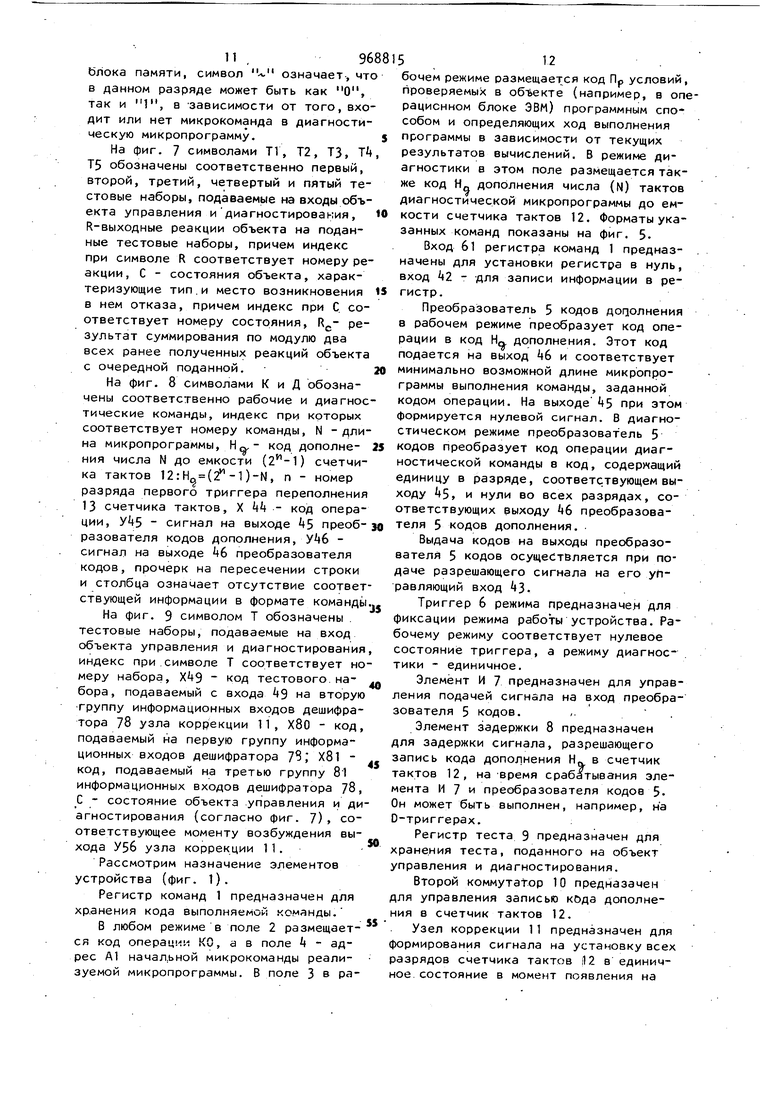

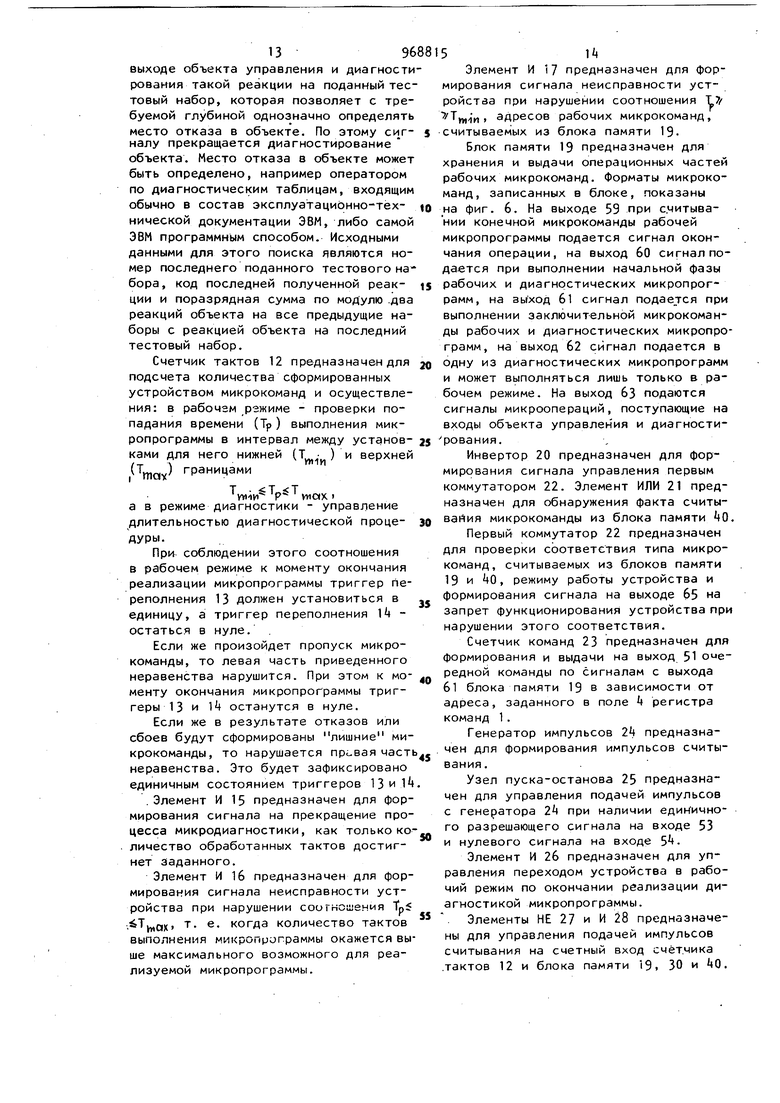

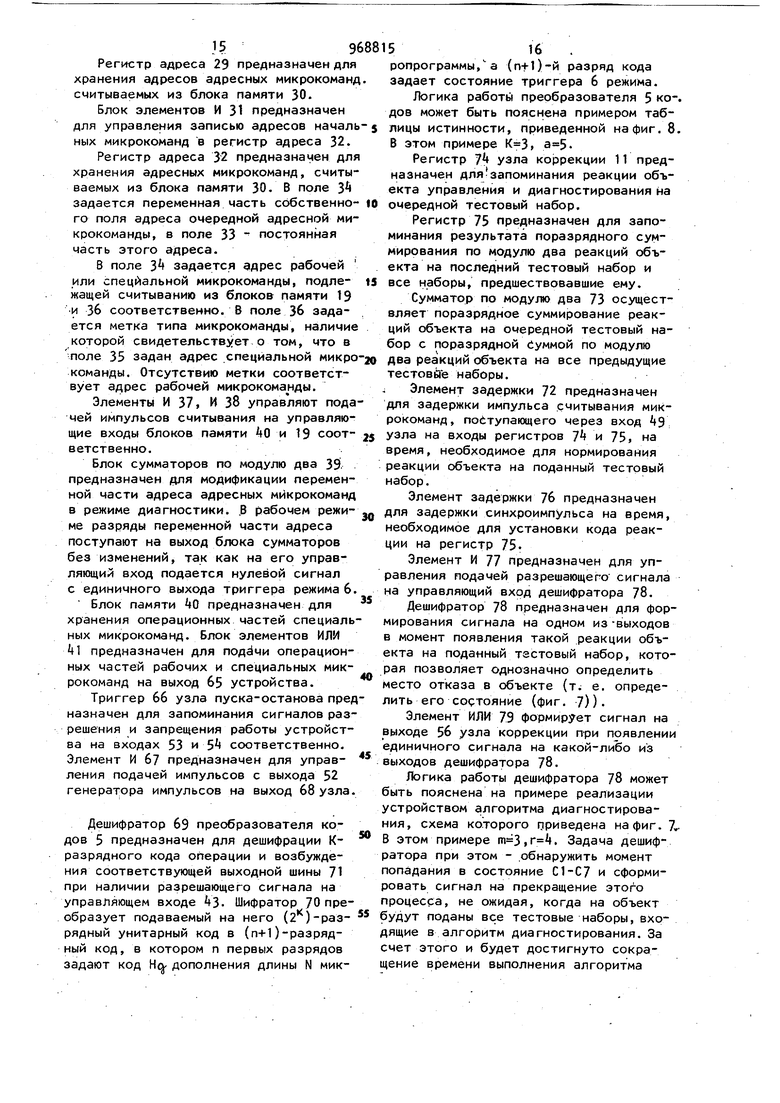

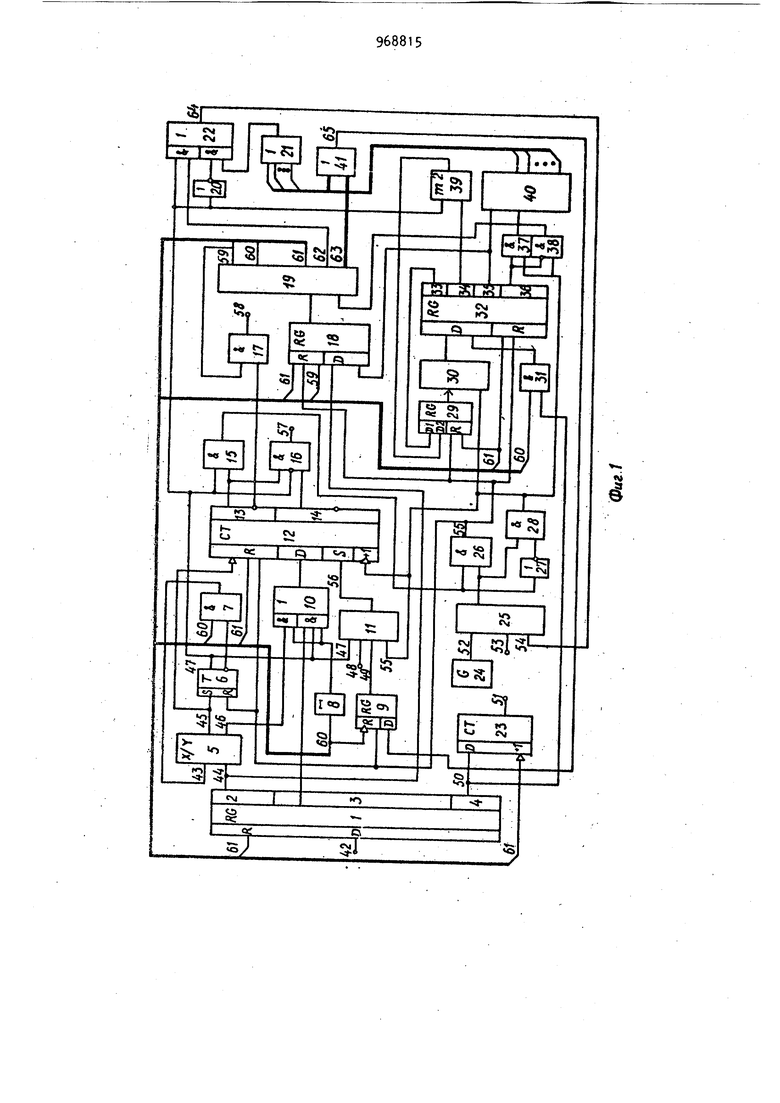

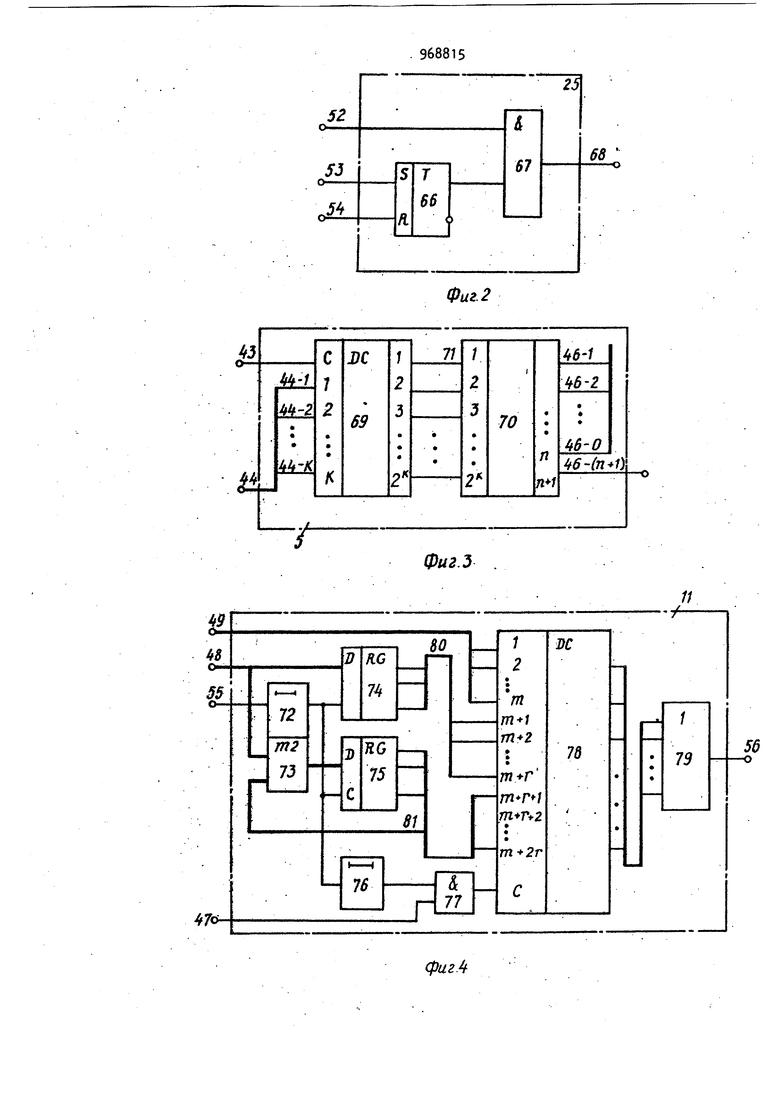

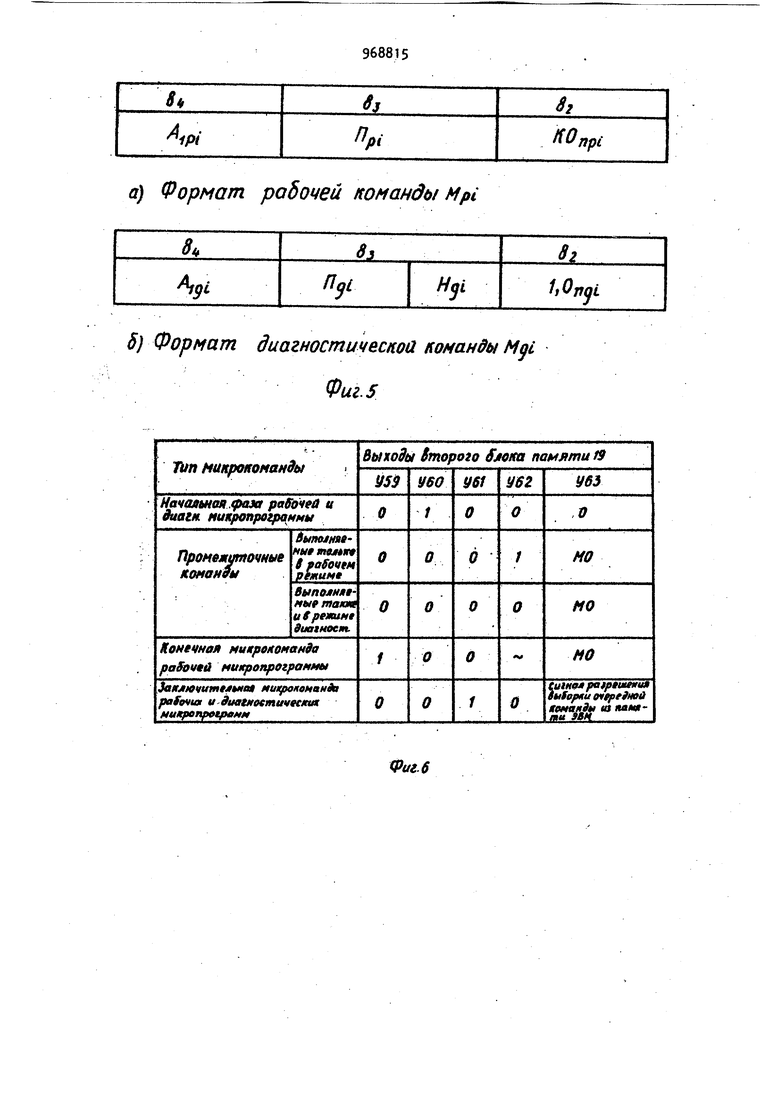

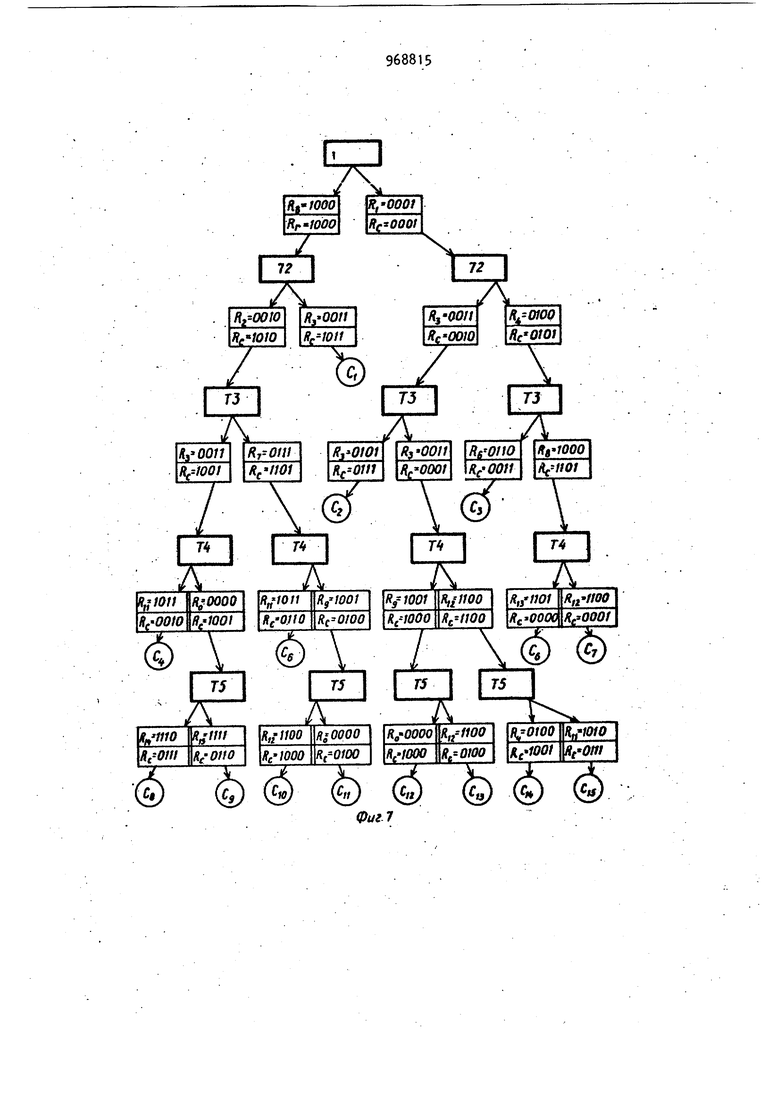

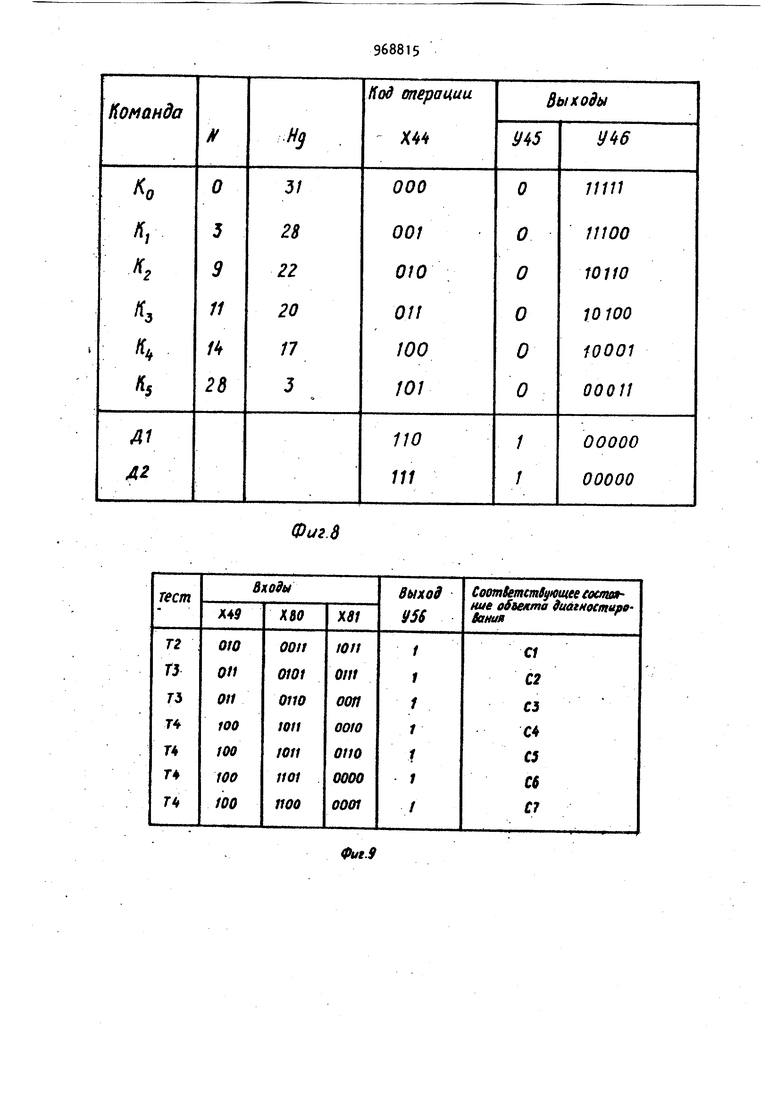

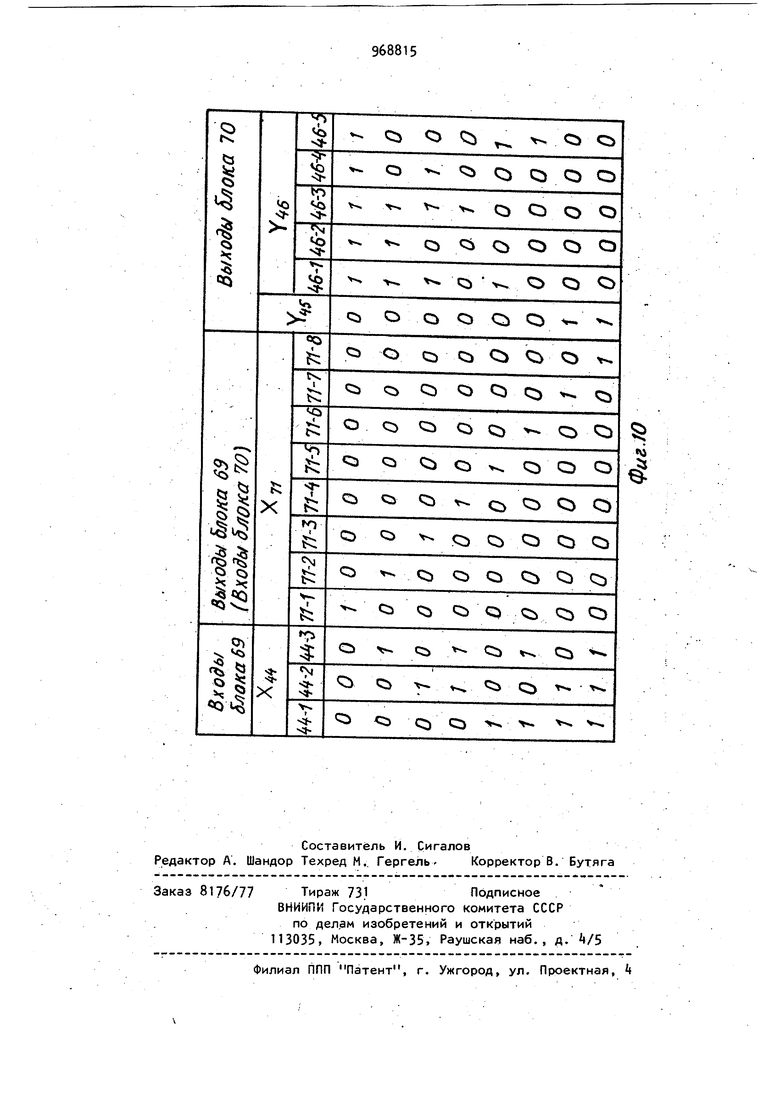

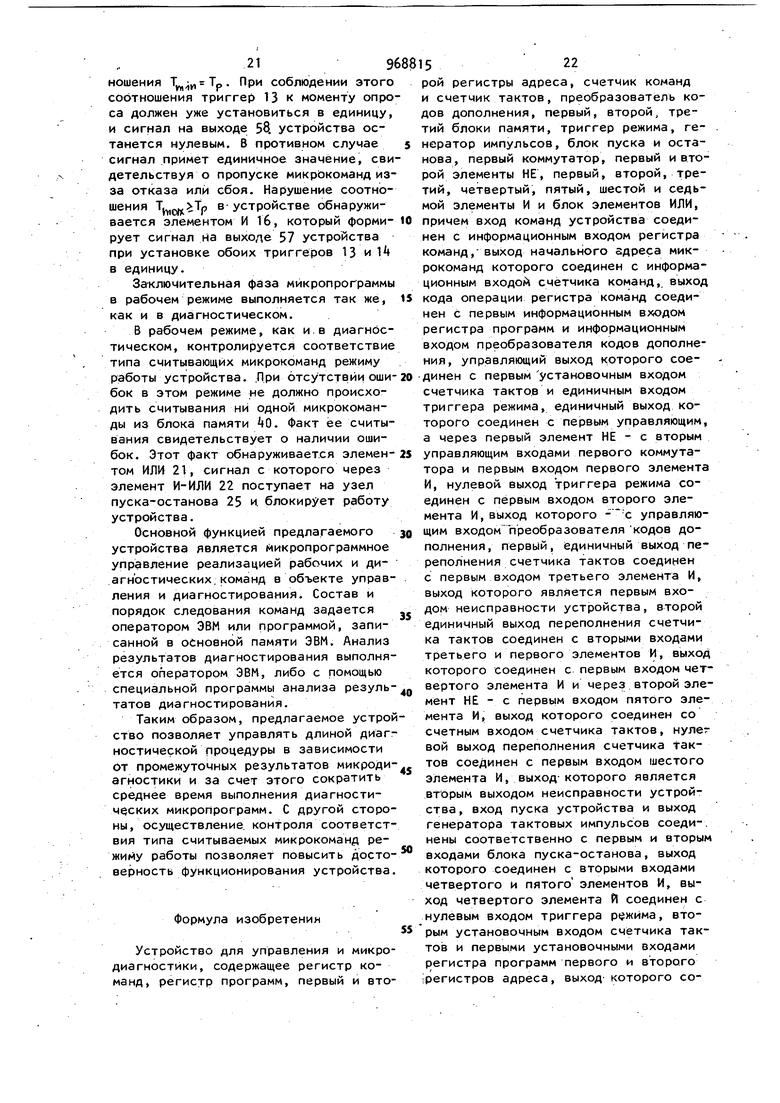

Наи(более близким к предлагаемому по технической сущности и достигаемому положительному эффекту является устройство управления и микродиагностики, содержащее регистр команд, счетчик команд, преобразователь кодов, триггер режима: генератор импульсов, узел пуска-останова, счетчик тактов, регистр программ, два регистра адреса, три блока памяти, блок элементов ИЛИ, элемент И-ИЛИ, семь элементов И и два инвертора, причем первая группа выходов регистра команд соединена с первой группой информационных входов регистра программ и преобразователя кодов, выход которого соединен с единичным входом триггера режима и с первым входом установки в нуль счетчика тактов, второй вход установки в нуль которого, соединен с нулевым входом триггера режима, с второй группой информационных входов регистра программ, с первыми входами установки в нуль первого и второго регистров адреса и выходом первого элемента И, первый вход которого соединен с выходом узла пуска-останова и с первым входом второго элемента И, выход которого соединен со счетным входом счетчика тактов, а через третий элемент И - со считывающим входом первого блока памяти, группа выходов которого через первые входы блока элементов ИЛИ соединена с первой группой выходов устройства; выход регистра программ соединен с адресным входом второго блока памяти, первый вход которого соединен с входами установки в нуль регистра программ, регистра команд, с вторым входом установки в нуль регист ра адреса, с третьим входом установки в нуль счетчика тактов и со счетным входом счетчика команд ёыход которого является вторым выходам устройства причем группа установочных входов счет чика команд соединена с второй группо выходов регистра команд, третья групп выходов которого является третьим выходом устройства, а группа информационных входов регистра команд является первым входом устройства; второй 6Ь1ход второго блока памяти через четвер тый элемент И соединен с сийхронизирующим входом преобразователя кодов, причем второй вход четвертого элемента И соединен с нулевым выходом триггера режима, единичный выход которого через пятый элемент И соединен с вторым входом первого элемента И и входом первого инвертора, выход которого соединен с вторым входом второго элемента И, причем единичный выход триггера режима соединен также с первым входом первой группы входов элемента И-ИЛИ и с входом второго инвертора, выход которого соединен с первым входом второй группы входов элемента ИИЛИ, второй вход пятого элемента И соединен с единичным выходом первого триггера переполнения счетчика таКтов и с первым входом шестого элемента И, выход которого является четвертым выходом устройства, а второй вход этого элемента соединен с единичным выходом второго триггера переполнения счетчика тактов, причем нулевой выход первого триггера переполнения счетчика тактов соединен с пятым выходом устройства через седьмой элемент И, второй вход которого соединен с третьей группой информационных входов регистра программ и с третьим выходом второго блока памяти, группа выходов которого соединена с вторыми входами блока элементов ИЛИ, выход генератора импульсов соединен с первым входом узла пуска-останова, второй вход которого является вторым входом устройства i вЫход второго регистра адреса соединен с адресным входом третьего блока памяти, группа выходов которого соединена с первой группой информационных входов первого регистра адреса, первая группа выходов которого соединена с адреснь1м входом первого блока памяти, а вторая группа выходов регистра соединена спервой группой информационнь1Х входов второго регистра адреса Г ЗНедостатком этого устройства является низкая достоверность функционирования и низкое быстродействие. Низкая достоверность функционирования устройЬтва обуславливается отсутствием контроля Считывания микр5 команд. В рабочем режиме устройство управляет выполнением обычных вычислительных команд ЭВМ по рабочим микропрограммам, которые состоят из рабочих микрокоманд, записанных во втором ;блоке памяти. При этом каждая микрокоманда имеет поле адреса, в котором задается адрес очередной микрокоманды. Одновременно с выполнением рабочей микропрограммы осуществляется контроль нижней и верхней границы времени ее выполнения. . В режиме диагностики устройства управляет диагностированием объекта управления. В состав диагностической микропрограммы входят специальные Диагностические микрокоманды, которые записаны в первом блоке памяти, а также некоторые рабочие микрокоманды, причем порядок следования последних в составе диагностической и рабочей микропрограммы может отличаться от их |порядка в составе рабочей микропрограммы. Для задания последовательности адреса рабочих и специальных микрокоманд в составе диагностической микропрограммы используется третий блок памяти. Из него одновременно со считыванием микрокоманды из первого и второго блоков памяти считывается адресная микрокоманда, которая задает адрес очередной рабочей или специальной микрокоманды. В режиме диагностики адресная информация, считанная из второго блока памяти, блокируется. Низкое быстродействие устройства обусловлено тем, что длина диагностической процедуры в устройстве задается перед ее началом и не изменяется в зависимости от результатов диагностирования, в то время, как при безусловном диагностировании имеется возможность сократить среднее число проверок, а следовательно, и время диагностирования, за счет реализации безусловного последовательного алгоритма диагностирования. Целью изобретения является повышение достоверности функционирования и быстродействия устройства. Поставленная цель достигается тем, что в устройство управления и микродиагностики, содержащее регистр команд, регистр программ, первый и второй регистры адреса, счетчик команд и счетчик тактов, преобразователь кодов дополнения, первый, второй и третий блоки памяти, триггеры режима, генератор импульсов, блок пуска-останова, первый коммутатор, первый и BTOрой элементы НЕ, первый, второй, третий, четвертый, пятый, шестой, седьмой элементы И и блок элементов ИЛИ, причем вход команд устройства соединен с информационным входом регистра команд, выход начального адреса микро команд которого соединен с информационным входом счетчика команд, выход кода операции регистра команд соединен с первым информационным входом регистра программ и информационным вхо дом преобразователя кодов дополнения, управляющий выход которого соединен с .первым установочным входом счетчика тактов и единичным входом триггера рб жима, единичный выход которого соединен с первым управляющим, а через пер вый элемент НЕ - с вторым управляющим входом первого коммутатора и первым входом первого элемента И, нулевой выход триггера режима соединен с первым входом второго элемента И, выход которого соединен с управляющим входом .преобразователя кодов дополнения, пер вый единичный выход переполнения счет чика тактов соединен с первым входом третьего элемента И, выход которого является первым выходом неисправности устройства, второй единичный выход переполнения счетчика токтоз соединен с вторыми входами третьего и первого элементов И, выход которого соединен с первым входом четвертого элемента И, и через второй элемент НЕ - с первым входом пятого элемента И, выход . которого соединен со счетным входом счетчика тактов, нулевой выход переполнения счетчика тактов соединен с первым входом шестого элемента И,выход которого .является вторым выходом неисправности устройства, вход пуска устройства и выход генератора тактовых импульсов соединены соответственно с первым и вторым входами блока пуска-останова, выход которого соединен с вторыми входами четвертого и пятого элементов И, выход четвертого элемента И соединен с нулевым входом триггера режима, вторым установочным входом счетчика тактов и первь1м установочными входами регистра программ первого и второго регистров адреса, выход которого соединен с адресными входами первого блока памяти, выход первого блока памяти соединен с первым информационным входом первого регистра адреса, первый адресный выход которого соединен с первым информационным входом регистра адреса, управляющий выход первого регистра адреса соединен с первым входом седьмого элемента И, выход которого соединен с управляющим входом второго блока памяти, второй адресный выход первого регистра адреса соединен с адресным входом второго блока памяти, выходы которого соединены с первыми входами блока элементов ИЛИ, выход микрооператора третьего блока памяти соединены с вторыми входами блока элементов ИЛИ, выход которого является выходом микроопераций устройства, выход регис тре программ соединен с.адресными входами третьего блока памяти, первый управляющий выход которого соединен со вторым входом шестого элемента И и вторым установочным входом регистра программ, второй и третий управляющие выходы третьего блока памяти соединены соответственно со вторым входом второго элемента И и вторым установочным входом первого регистра адреса, третьим установочным входом регистра программ, третьим установочным входом счетчика тактов, установочным входом регистра команд и счетным входом счетчика команд, выход которого является выходом адреса устройства, выход второго регистра адреса соединен с адресными входом первого блока памяти, введены регистр теста, блок коррекции, второй коммутатор, блок элементов И, восьмой элемент И, эле-мент ИЛИ, элемент задержки, сумматор по модуж) два причем информационный, вход устройства соединен с информационным входом бло ка коррекции, выход которого соединен с единичным установочным входом счетчика тактов, информационный выход преобразователя кодов дополнения и выход поля дополнения регистра команд соединены соответственно с первым и вторым информационными входами второго коммутатора, выход которого соединен с информационными счетчика, тактов, . второй управляющий выход третьего блока памяти соединен с первым установочным входом регистра теста,.первым входом блока элементов И и через элемент задержки - с первыми управляющими входами второго коммутатора, единичный выход триггера режима соединен с вторым управляющим входом второго коммутатора, первым управляющим входом коррекции, входом первого элемента НЕ, первым входом сумматора по модулю два и инверсным входом третьего элемента И, выход четвертого элемента И соединен с вторым установочным.входом регистра тестов, выход которого соединен с вторым информационным входом блока коррекции, выход Пятого элемента И соединен с управляющим входом первого блока памяти, вторым управляющим входом блока коррекции, вторым входом седьмого элемента И и прямым входом восьмого элемента И, выход которого соединен с управляющим вхОдом третьего блока памяти, управляющий, второй и третий адресный выходы первого регистра адреса соединены соответственно с инверсным входом восьмого элемента И, вторым информационным входом регистра программ и вторым вхо дом сумматора по модулю два,выход ко торого соединен с вторым информационным входом второго регистра адреса, третий управляющий выход третьего бло ка памяти соединен с вторым установоч ным входом второг;о регистра адреса, выход начального адреса микрокоманд регистра команд соединен с вторым вхо дом блока элементов.И, выход которого соединен с вторым информационным входом первого регистра адреса, выходы второго блока памяти соединены с входами элементов ИЛИ, выходы которых соединены- с первым информационным входом первого коммутатора, управляющий выход метки второго блока памяти соединен с вторым информационным входом первого коммутатора, выход которого соединен с третьим входом блока пуска; Останова, выход блока элементов ИЛИ соединен с информационным входом ре- . гистра теста,. Кроме того, узел коррекции содержит первый и второй регистры, дешифратор, первый и второй элементы задержки, сумматор по модулю два, элемент И, элемент ИЛИ, причем первы1й и второй управляющие входы блока соединены соответственно с первым входом элемента И и входом первого элемента задержки, выход которого соединен с синхронизирующими входами первого и второго регистров и через второй элемент задержки с вторым входом элемента И, выход второго элемента И соединен с управляющим входом дешифратора, выход которого соединен со входами элемента ИЛИ, выход элемента ИЛИ является выходом блока, первый информационный вход .блока соединен с информационным входом первого регистра и первым входом сумматора по-модулю два, выход которого соединен с информационными входами второго регистра, второй информационный вход блока и выход первого регистра соединен соответственно с первым и вторым информационными входами дешифратора, выход второго регистра соединен с третьим информационным входом дешифратора и вторым входом сумматора по модулю два. Изобретение обеспечивает повышение быстродействия и достоверность функционирования устройства. Повышение быстродействия достигается за счет обеспечения возможности управления длиной условной диагностической процедуры путем реализации безусловного последовательного алгоритма диагностирования. Повышение достоверности функционирования устройства достигается за счет осуществления контроля соответствия считываемых микрокоманд режиму работы. Введение указанных элементов и связей позволяет осуществлять контроль соответствия считанных микрокоманд режиму работы устройства, формировать рабочие и диагностические микропрограммы при однократной записи адресов рабочих микрокоманд, а также управлять длиной микродиагностической процедуры. За счет этого повышается достоверность функционирования и быстродействие устройства. На фиг. 1 изображена функциональная схема предлагаемого ycтpoйctвa, 9 96 на фиг, 2 - функциональная схема узла пуска-останова; на фиг. 3 функциональная схема преобразователя кодов дополнения; на фиг, k - функциональная схема узла коррекции, на фиг. 5 форматы команд, подаваемых на вход устройства, на фиг. 6 - форматы микрокоманд, формируемых устройством, на фиг, 7 пример схемы алгоритма микродиагностики, реализуемого.устройством; на фиг, 8 - пример таблицы истин ности, реализуемой преобразователем кодов; на фиг, 9 пример таблицы разрешенных наборов узла дешифраторэлемент ИЛИ узла коррекции; на фиг, 10 - пример таблицы соответствия, опи сывающей работу преобразователя 5 кодов дополнения (фиг, 3). Устройство (фиг, 1) содержит регистр команд 1 с полем 2 операции, полем 3 дополнения и полем k адреса начальной микрокоманды, преобразователь 5 кодов дополнения, триггер режима 6, второй элемент И 7, элемент задержки 8, регистр теста 9 второй коммутатор 10, узел коррекции 11, счетчик 12 тактов с первым 13 и вторым 14 три1- герами переполнения, первый 15, тре- тий 16 и шестой 17 элементы И, регист программ 18, третий блок памяти 19, первый инвертор 20, элемент ИЛИ 21, первый коммутатор 22, счетчик команд 23, генератор импульсов 2, узел пуска-останова 25, четвертый элемент И 2б, второй инвертор 27, пятый элемент И 28, второй регистр адреса 29, первый блок памяти 30, блок элементов И 31 первый регистр адреса 32 с первым адресным 33 третьим адресным полем З, вторым адресным полем 35 и управляющим полем Зб, седьмой 37 и восьмой 38 элементы И, блок сумматоров по модулю два 39, второй блок памяти «О и первый блок элементов ИЛИ Ц. Символом 42 на фиг. 1 обозначен информационный вход команд, управляющий вход 43 преобразователя кодов, информационный вход Ц преобразователя кодов, управляющий выход kS преобразователя кодов, информационный выход 46 преобразователя кодов, единичный выход 47 триггера режима 6, первый информационный вход 4§ устройства, выход 49 регистра теста 9, третий выход 50 поля 4 регистра команд 1, адресный выход 51 устройства, выход 52 генератора импульсов 2h, вход S3 пуска устройства, третий вход 54 узла пускапостанова, выход 55 элемента И 26, вы510ход 5б узла коррекции, соответственно первый и второй выходы 57 58 неисправности, соответственно первый, второй , третий и четвертый управляющие выходы третьего блока памяти 19, группа выходов 63 микроопераций блока памяти 19, выход 64 первого коммутатора, выход б5 микроопераций устройства. Блок пуска-останова (фиг. 2)содержит триггер 66 и элемент И 67. Символом 68 на фиг, 2 обозначен выход блока пуска-останоаа. Преобразователь кодов (фиг, 3) содержит дешифратор 69 с управляющим входом 43 и информационным входом 44, шифратор 70, имеющий (п+1) выходов, первых из которых образуют отдельную группу. Символом 71 на фиг. 3 обозначены выходы дешифратора, К-разрядность поля кода операции 2 регистра команд 1, - номер разряда первого триггера переполнения 13 счетчика тактов 12. Узел коррекции (фиг: 4) содержит первый элемент задержки 72, блок сумматоров по модулю два 73, первый 74 и второй 75 регистры, второй .элемент задержки 76, элемент И 77, дешифратор 78 и элемент ИЛИ 79. Символами 80 и 81 на фиг, 4 обозначены группы выходов соответственно первого и второго регистров, 5б - выход узла коррекции, т-разрядность тестовых наборов, формируемых устройством, г-разрядность выходных реакций управления и диагностирования. На фиг, 5 символом 82 обозначено поле кода операций, 83 - поле дополнения, 84 - поле адреса начальной микрокоманды, А и A,(j. - адреса начальных микрокоманд соответственно рабочей и диагностической i-й микропрограммы, Пр и коды условий соответственно рабочей и диагностической i-й микропрограммы, Н „ - код дополнения длины i-й диагностической микропрограммы до емкости () счетчика тактов 12, п - номер разрядного первого триггера переполнения 13 счетчика тактов, K0j,p4 и - код операции соответственно рабочей и диагностической i-й программы. На фиг, 6 символами У59, УбО. Уб1 Уб2 обозначены соответственно 59, 60, 61, 62 выходы третьего блока памяти 19, УбЗ выход микроопераций, МО код микроопераций; символы 1 и О обозначают наличие соответственно единичного и нулевого сигналов на выходе briOKa памяти, символ л. означает, что в данном разряде может быть как О, так и 1, в зависимости от того, входит или нет микрокоманда в диагностическую микропрограмму. На фиг. 7 символами TV, Т2, ТЗ, Т Т5 обозначены соответственно первый, второй, третий, четвертый и пятый тестовые наборы, подаваемые на входы объекта управления идиагностирования, R-выходные реакции объекта на поданные тестовые наборы, причем индекс при символе R соответствует номеру реакции, С - состояния объекта, характеризующие тип.и место возникновения в нем отказа, причем индекс при С. соответствует номеру состояния, результат суммирования по модулю два всех ранее полученных реакций объекта с очередной поданной. На фиг. 8 символами К и Д обозначены соответственно рабочие и диагнос тические команды, индекс при которых соответствует номеру команды, N - длина микропрограммы, HQ,- код дополнения числа N до емкости () счетчика тактов 12:Но (/-1)-N, п - номер разряда первого триггера переполнения 13 счетчика тактов, X kk - код операции, ykS - сигнал на выходе 45 преобразователя кодов дополнения, сигнал на выходе 46 преобразователя кодов, прочерк на пересечении строки и столбца означает отсутствие соответ ствующей информации в формате команды На фиг. 9 символом Т обозначены . тестовые наборы, подаваемые на вход объекта управления и диагностирования индекс при.символе Т соответствует но меру набора, Х+9 - код тестового, набора, подаваемый с входа Э на вторую группу информационных входов дешифратора 78 узла коррекции 11, ХЗО - код, подаваемый на первую группу информационных входов дешифратора Х81 код, подаваемый на третью группу 81 информационных входов дешифратора 78, С - состояние объекта управления и ди агностирования (согласно фиг. 7) соответствующее моменту возбуждения выхода У5б узла коррекции 11. Рассмотрим назначение элементов устройства (фиг. 1). Регистр команд 1 предназначен для хр.анения кода выполняемой команды. В любом режиме в поле 2 размещается код операции КО, а в поле 4 - адрес А1 начальной микрокоманды реализуемой микропрограммы. В поле 3 в рабочем режиме размещает ся код Пр условий, проверяемых в объекте (например, в операционном блоке ЭВМ) программным способом и определяющих ход выполнения программы в зависимости от текущих результатов вычислений. В режиме диагностики в этом поле размещается также код Н„ дополнения числа (N) тактов диагностической микропрограммы до емкости счетчика тактов 12. Форматы указанных команд показаны на фиг. 5Вход б1 регистра команд 1 предназначены для установки регистра в нуль, вход 42 - -для записи информации в регистр. Преобразователь 5 кодов доаолнения в рабочем режиме преобразует код операции в код HQ. дополнения. Этот код подается на выход 46 и соответствует минимально возможной длине микропрограммы выполнения команды, заданной кодом операции. На выходе 45 при этом формируется нулевой сигнал. В диагностическом режиме преобразователь 5 кодов преобразует код операции диагностической команды в код, содержащий единицу в разряде, соответствующем выходу 45, и нули во всех разрядах, соответствующих выходу 46 преобразователя 5 кодов дополнения. Выдача кодов на выходы преобразователя 5 кодов осуществляется при подаче разрешающего сигнала на его управляющий вход 43. Триггер 6 режима предназначен для фиксации режима работы устройства. Рабочему режиму соответствует нулевое состояние триггера, а режиму диагностики - единичное. Элемент И 7 предназначен для управления подачей сигнала на вход преобразователя 5 кодов. /. . Элемент задержки 8 предназначен для задержки сигнала, разрешающего запись кода дополнения Нг. в счетчик тактов 12, на Время срабатывания элемента И 7 и преобразователя кодов 5. Он может быть выполнен, например, на D-триггерах. Регистр теста 9 предназначен для хранения теста, поданного на объект управления и диагностирования. Второй коммутатор 10 предназачен для управления записью кода дополнения в счетчик тактов 12. Узел коррекции 11 предназначен для формирования сигнала на установку всех разрядов счетчика тактов 112 в единичное, состояние в момент появления на

1396

выходе объекта управления и диагностирования такой реакции на поданный тестовый набор, которая позволяет с требуемой глубиной однозначно определять место отказа в объекте. По этому сигналу прекращается диагностирование объекта. Место отказа в объекте может быть определено, например оператором по диагностическим таблицам, входящим обычно в состав эксплуатационно-технической документации ЭВМ, либо самой ЭВМ программным способом. Исходными данными для этого поиска являются номер последнего поданного тестового набора, код последней полученной реакции и поразрядная сумма по модулю .два реакций объекта на все предыдущие наборы с реакцией объекта на последний тестовый набор.

Счетчик тактов 12 предназначен для подсчета количества сформированных устройством микрокоманд и осуществления: в рабочгм режиме - проверки попадания времени (Тр) выполнения микропрограммы в интервал между установнами для него нижней (Т ) и верхней

/т- лГПИ

границами

mw Р vrtdx а в режиме диагностики - управление

длительностью диагностической процедуры.

При соблюдении этого соотношения в рабочем режиме к моменту окончания реализации микропрограммы триггер переполнения 13 должен установиться в единицу, а триггер переполнения остаться в нуле. .

Если же произойдет пропуск микрокоманды, то левая часть приведенного неравенства нарушится. При этом к моменту окончания микропрограммы три|- геры 13 и И останутся в нуле.

Если же в результате отказов или сбоев будут сформированы лишние микрокоманды, то нарушается правая 4acTb неравенства. Это будет зафиксировано единичным состоянием триггеров 13 и И .Элемент И 15 предназначен для формирования сигнала на прекращение процесса микродиагностики, как только количество обработанных тактов дости - нет заданного.

Элемент И 16 предназначен для формирования сигнала неисправности устройства при нарушении соогношения Тр5 .., т. е. когда количество тактов выполнения микропрограммы окажется выше максимального возможного для реализуемой микропрограммы.

Элемент И 17 предназначен для формирования сигнала неисправности устройства при нарушении соотношения Т7/ адресов рабочих микрокоманд, считываемых из блока памяти 19.

Блок памяти 19 предназначен для хранения и выдачи операционных частей рабочих микрокоманд. Форматы микрокоманд, записанных в блоке, показаны на фиг. 6. На выходе 59 при с.читывании конечной микрокоманды рабочей микропрограммы подается сигнал окончания операции, на выход 60 сигнал подается при выполнении начальной фазы рабочих и диагностических микропрограмм, на выхоД 61 сигнал подается при выполнении заключительной микрокоманды рабочих и диагностических микропрограмм, на выход 62 сигнал подается в одну из диагностических микропрограмм и может выполняться лишь только в рабочем режиме. На выход 63 подаются сигналы микроопераций, поступающие на входы объекта управления и диагностирования.

Инвертор 20 предназначен для формирования сигнала управления первым коммутатором 22. Элемент ИЛИ 21 предназначен для обнаружения факта считывайия микрокоманды из блока памяти ЦО.

Первый коммутатор 22 предназначен для проверки соответствия типа микрокоманд, считываемых из блоков памяти 19 и , режиму работы устройства и формирования сигнала на выходе 65 на запрет функционирования устройства при нарушении этого соответствия.

Счетчик команд 23 предназначен для формирования и выдачи на выход 51 оиередной команды по сигналам с выхода 61 блока памяти 19 в зависимости от адреса, заданного в поле А регистра команд 1.

Генератор импульсов предназначен для формирования импульсов считывания.

Узел пуска-останова 25 предназначен для управления подачей импульсов с генератора при наличии едикичного разрешающего сигнала на входе 53 и нулевого сигнала на входе 5.

Элемент И 26 предназначен для управления переходом устройства в рабочий режим по окончании реализации диагностикой микропрограммы. . Элементы НЕ 27 и И 28 предназначены для управления подачей импульсов считывания на счетный вход счётчика тактов 12 и блока памяти 19, 30 и kO. Регистр адреса 29 предназначен для хранения адресов адресных микрокоманд считываемых из блока памяти 30. Блок элементов И 31 предназначен для управления записью адресов началь ных микрокоманд в регистр адреса 32. Регистр адреса 32 предназначен для хранения адресных микрокоманд, считываемых из блока памяти 30. В поле 3 задается переменная часть собственного поля адреса очередной адресной микрокоманды, в поле 33 - постоянная часть этого адреса. В поле 3 задается адрес рабочей или специальной микрокоманды, подлежащей считыванию из блоков памяти 19 и 36 соответственно. В поле 36 задается метка типа микрокоманды, наличие которой свидетельствует о том, что в поле 35 задан адрес специальной микро команды. Отсутствию метки соответствует адрес рабочей микрокома 1ды. Элементы И 37. И 38 управляют подачей импульсов считывания на управляющие входы блоков памяти 40 и 19 соответственно. Блок сумматоров по модулю два 39 предназначен для модификации переменной части адреса адресных микрокоманд в режиме диагностики. В рабочем режиме разряды переменной части адреса поступают на выход блока сумматоров без изменений, так как на его управляющий вход подается нулевой сигнал с единичного выхода триггера режима 6 Блок памяти 0 предназначен для хранения операционных частей специаль ных микрокоманд. Блок элементов ИЛИ tl предназначен для подёчи операционных частей рабочих и специальных микрокоманд на выход б5 устройства. Триггер 66 узла пуска-останова пре назначен для запоминания сигналов раз решения и запрещения работы устройства на входах 53 и 5 соответственно. Элемент И б7 предназначен для управления подачей импульсов с выхода 52 генератора импульсов на выход 68 узла Дешифратор 69 преобразователя кодов 5 предназначен для дешифрации Кразрядного кода операции и возбуждения соответствующей выходной шины 71 при наличии разрешающего сигнала на управляющем входе Шифратор 70 преобразует подаваемый на него ()-разрядный унитарный код в (п+1)-разрядный код, в котором п первых разрядов задают код Htv дополнения длины N микропрограммы,а (п+1)-й разряд кода задает состояние триггера 6 режима. Логика работы преобразователя 5 ко-, дов может быть пояснена примером таблицы истинности, приведенной на фиг. 8. В этом примере , . Регистр 74 узла коррекции 11 предназначен для-запоминания реакции объекта управления и диагностирования на очередной тестовый набор. Регистр 75 предназначен для запоминания результата поразрядного суммирования по модулю два реакций объекта на последний тестовый набор и все наборы, предшествовавшие ему. Сумматор по модулю два 73 осуществляет поразрядное суммирование реакций объекта на очередной тестовый набор с поразрядной Суммой по модулю два реакций объекта на все предыдущие тестовйе наборы. Элемент задержки 72 предназначен для задержки импульса считывания микрокоманд, поступающего через вход 43 УЗла на входы регистров Ik и 75, на время, необходимое для нормирования реакции объекта на поданный тестовый набор. Элемент задержки 76 предназначен для задержки синхроимпульса на время, необходимое для установки кода реакции на регистр 75Элемент И 77 предназначен для управления подачей разрешающего сигнала на управляющий вход дешифратора 78. Дешифратор 78 предназначен для формирования сигнала на одном из-выходов в момент появления такой реакции объекта на поданный тестовый набор, которая позволяет однозначно определить место отказа в объекте (т; е. определить его состояние (фиг. 7)). Элемент ИЛИ 79 формирует сигнал на выходе 5б узла коррекции п-ри появлении единичного сигнала на какой-либо из выходов дешифратора 78. Логика работы дешифратора 78 может быть пояснена на примере реализации устройством алгоритма диагностирования, схема которого приведена на фиг. этом примере . Задача дешифратора при этом - .обнаружить момент попадания в состояние С1-С7 и сформировать сигнал на прекращение этого процесса, не ожидая, когда на объект будут поданы все тестовые наборы, входящие в алгоритм диагностирования. За счет этого и будет достигнуто сокращение времени выполнения алгоритма 1796 диагностирования, а следовательно, бу дет обеспечено и повышение быстродействия устройства. Так как каждому ука занному состоянию однозначно соответствует определенная комбинация кода тестового набора, реакция объекта на этот набор и суммы по модулю два этой реакции со всеми предыдущими реакциями, то выходы дешифратора 78 должны возбуждать только при появлении указанных комбинаций сигналов на его выходах. Это и показано в соответствующей фиг. 7 таблице разрешенных наборов узла дешифратор 78 - элемент ИЛИ представленной на фиг. 9 и соответствующей алгоритму на фиг. 7Элементы задержки 72 и 76 могут быть выполнены, например, на D-триггерах. Рассмотрим работу устройстваi Она возможна в диагностическом и рабочем режимах. Независимо рт режима, перед запуском устройства в работу все его элементы памяти устанавливаются в нуль. Затем в регистр команд 1 записывается код команды. Рабочая команда имеет формат, представленный на фиг. 5 а, диагностическая - на фиг. 56. С поля 2 регистра 1 на информацйонный вход регистра программ 18 поступает код операции, устанавливающий на регистре адрес микрокоманды, которая называется начальной фазой микропрограммы. С нее начинается любая диагностическая и рабочая микропрограмма. Далее при подаче разрешающего сиг нала на вход 53 устройства импульс считывания от генератора 2k проходит через блок 25 пуска-останова и элемент И 28 на считывающий вход блока памяти 30. Так как в регистре 29 при этом установлен нулевой код, то состояние выходов блока памяти 30 при .этом останется нулевым. Через элемент |И 38 импульс также поступает на счи1ты6ающий вход блока памяти 19 и считывает из него начальную фазу микропрограммы. При этом подается единич1НЫЙ сигнал на выход 60 блока, по которому через открытый элемент И 7 подается разрешающий сигнал на вход 3 преобразователя кодов 5 и устанавливается в нуль регистр теста 9. Если код, подаваемый на группу информационных входов 44 преобразователя кодов 5 задает диагностическую микропрограмму, то сигналы на его гру пе выходов 46 останутся нулевыми, а 18 сигнал на выходе 45 станет единичным и установит триггер 6 режима в единичное состояние, зафиксировав переход устройства в режим диагностики. После срабатывания преобразователя кодов 5 сигнал с выхода 60 блока памяти 19 через элемент задержки 8 открывает входы второго коммутатора 10, в результате чего код дополнения Н длины N диагностической микропрограммы до емкости () счетчика тактов 12 с поля 3 регистра 1 поступает на вход счетчика тактов 12 и записывается в него. Тем же сигналом с выхода 60 блока памяти 19 открывается блок элементов И 31, в результате чего с поля 4 в регистр адреса 32 поступает адрес первой адресной микрокоманды и адрес первой микрокоманды диагностической микропрограммы. Адрес первой адресной микрокоманды с полей 33 и 34 поступает в регистр адреса 29, при этом переменная часть адреса с поля 34 модифицируется блоком сумматоров по модулю два 39, на управляющий вход которого подан единичный сигнал с единичного выхода триггера 6 режима. Адрес первой микрокоманды диагностической микропрограммы с поля 35 подается на блок памяти 40, а через регистр 18 на блок памяти 19. При этом сигналом с поля Зб (метка типа микрокоманды) открывается элемент И 37 или И 38, подготавливая путь для прохождения импульса считывания. Если в поле 35 записан адрес рабочей микрокоманды, то метка в поле 36 отсутствует, вследствие чего открытым окажется элемент И 38, который подает очередной импульс считывания на блок памяти 19 Если же в поле 35 записан адрес специальной микрокоманды, в поле 36 будет записана метка, по которой будет закрыт элемент И 38 и откроется элемент И 37, через который очередной импульс считывания поступает на блок памяти 40. Сигналы микроопераций считанной диа|- ностической микрокоманды через блок элементов ИЛИ 41 поступают на выход 65 устройства. Этим же импульсом в счетчик тактов 12 добавляется единица, а из блока памяти 30 считывается первая адресная микрокоманда, которая записывается в регистр 31. С полей 33 и 34 регистра в регистр эдреса 29 поступает сформированный аналогично вышеописанному адрес следующей адресной микрокоманды. Адрес очередной диагностической / микрокоманды с поля 35 регистра 32 поступает на блоки памяти kO и 19Одновременно этот же импульс считывания поступает на счетный вход счетчика тактов 12 и добавляет в него единицу. По следующему тактовому импульсу устройство работает так же, как и при считывании первой микрокоманды,

выдавая микрооперации диагностической 10 жиме контролируется соответствие межмикропрограммы на выход 65 с одновре- ду режимом работы и типом рабочих микменным подсчетом тактов счетчиком 12. При считывании конечной микрокоманды диагностической микропрограммы первый триггер переполнения 13 устанавливается в единицу и открывает эле мент И 15 единичным сигналом с выхода которого через инвертор 27 закры- вается элемент И 28, запрещая подачу импульсов считываний на блоки памяти 19, 30, Зб. Кроме того, открыв элемент И 26, через который следующий импульс с выхода узла пуска-останова 25 установит в нуль регистры 29, 32,, счетчик тактов 12, регистр теста 9 и триггер режима 6. В регистр программ 18 при этом будет установлен адрес заключительной микрокоманды, которая завершает любую диагностическую и рабочую микропрограмму. Так как при этом триггер 6 режима устанавливается в нуль, то элемент И 15 вновь закрывается, открывая .через инвертор 27 элемент И 28. Через этот элемент очередной импульс считывания узла пускаостанов.а 25 поступает на управляющий .вход блока памяти 19, считывая из него заключительную микропрограмму, которая возбуждает выход б1 блока. Сигналом с этого выхода добавляется единица 8 счётчик команд 23 и устанавливаются в нуль регистр команд 1, счетчик тактов 12, регистры адреса 29, 32 и регистр программ 18. С выхода 63 блока памяти 19 на выход б5 устройства подается сигнал на разрешение выборки очередной команды из основной памяти ЭВМ и запись ее в регистр команд 1. В диагностическом режиме в устройстве осуществляется управление длиной микродиагностической процедуры путем реализации последовательного безуслов ного алгоритма диагностирования. В момент появления на выходе объекта такой реакции на поданный тестовый набор, которая позволяет одночасно определить место отказа в объекте, сигналом с выхода 5б узла коррекции 11

все триггеры счетчика тактов устанавливаются в единицу. При этом возбуждается выход элемента И 15. аналогич-но описанному выше прекращается выполнение диагностической микропрограммы, не ожидая окончания выдачи на объект всех .тестовых наборов, предусмотренных этой микропрограммой

Кроме того, в диагностическом рерокоманд, считываемых из блока памяти 19. Считывание из него микрокоманды, которая не входит в состав ни одной из диагностических микропрограмм, свидетельствует об ошибке в работе устройства. В такой микрокоманде на выход 62 подается сигнал, который через первый KOMMyTatop 22 поступает на вход 5 узла пуска-останова и бло-. кирует работу устройства. В рабочем режиме устройство формирует микрокоманды, управляющие выполнением вычислительных команд в объекте управления. При этом контролируется попадание времени (Тр) выполнения микропрограммы в установленный для нее интервал между установленными для нее нижней (.) и верхней () границами. Отличие процесса выполнения начальной фазы рабочей микропрограммы от диагностической состоит в том, что по соответствующему коду операции на выходе 45 преобразователя 5 кодов формируется нулевой сигнал, а на группе выходов формируется код Но, дополнения. Этот код по сигналу на выходе элемента задержки устанавливается через второй коммутатор 10 на счетчике тактов 12. Триггер режима 6 при этом остается в нулевом состоянии, фиксируя рабочий режим в устройстве. Первая и последняя микрокоманды рабочей микропрограммь формируются так же, как и в диагностическом режиме. Отличие от диагностического режима при этом состоит в том, что разряд метки в поле 36 регистра 32 постоянно сохраняет нулевое значение, вследствие чего считывание микрокоманд из блока памяти 0 не происходит. Кроме того, при считывании конечной микрокоманды рабочей микропрограммы на выходе 59 блока памяти 19 формируется сигнал конца операции, по которому открывается элемент И 15, опрашивая состояние первого триггера переполнения 13 и проверяя тем самым выполнение соот2196ношения Р соблюдении этого соотношения триггер 13 к моменту опроса должен уже установиться в единицу, и сигнал на выходе 58. устройства останется нулевым, В противном случае сигнал примет единичное значение, свидетельствуя о пропуске микрокоманд изза отказа или сбоя. Нарушение соотношения Ти,( в- устройстве обнаруживается элементом И 16, который формирует сигнал на выходе 57 устройства при установке обоих триггеров 13 и И в единицу. Заключительная фаза микропрограммы в рабочем режиме выполняется так же, как и в диагностическом. В рабочем режиме, как и.в диагностическом, контролируется соответствие типа считывающих микрокоманд режиму работы устройства. При отсутствии оши бок в этом режиме не должно происходить считывания ни одной микрокоманды из блока памяти 40. Факт ее считывания свидетельствует о наличии ошибок. Этот факт обнаруживается элементом ИЛИ 21, сигнал с которого через элемент И-ИЛИ 22 поступает на узел пуска-останова 25 и. блокирует работу устройства. Основной функцией предлагаемого устройства является микропрограммное управление реализацией рабочих и диагностических, команд в объекте управления и диагностирования; Состав и порядок следования команд задается оператором ЭВМ или программой, записанной в основной памяти ЭВМ. Анализ результатов диагностирования выполняется оператором ЭВМ, либо с ромощью специальной программы анализа результатов диагностирования. Таким образом, предлагаемое устрой ство позволяет управлять длиной диагностической процедуры в зависимости от промежуточных результатов микродиагностики и за счет этого сократить среднее время выполнения диагностических микропрограмм. С другой стороны, осуществление контроля соответствия типа считываемых микрокоманд режиму работы позволяет повысить достоверность функционирования устройства. Формула изобретении Устройство для управления и микродиагностики, содержащее регистр команд, регистр программ, первый и вто15рой регистры адреса, счетчик команд и счетчик тактов, преобразователь кодов дополнения, первый, второй, третий блоки памяти, триггер режима, генератор импульсов, блок пуска и останова, первый коммутатор, первый и второй элементы НЕ, первый, второй, третий, четвертый, пятый, шестой и седьмой элементы И и блок элементов ИЛИ, причем вход команд устройства соединен с информационным входом регистра команд, выход начального адреса микрокоманд которого соединен с информационным входой счетчика команд, выход кода операции регистра команд соединен с первым информационным входом регистра программ и информационным входом преобразователя кодов дополнения, управляющий выход которого соединен с первымустановочным входом счетчика тактов и единичным входом триггера режима, единичный выход которого соединен с первым управляющим, а через первый элемент НЕ - с вторым управляющим входами первого коммутатора и первым входом первого элемента И, нулевой выход триггера режима соединен с первым входом второго элемента И, выход которого управляющим входом преобразователя кодов дополнения, первый, единичный выход переполнения счетчика тактов соединен с первым входом третьего элемента И, выход которого является первым входом неисправности устройства, второй единичный выход переполнения счетчика тактов соединен с вторыми входами третьего и первого элементов И, выход которого соединен с первым входом четвертого элемента И и через.второй элемент НЕ - с первым входом пятого элемента И, выход которого соединен со счетным входом счетчика тактов, нуле вой выход переполнения счетчика тактов соединен с первым входом шестого элемента И, выход которого является вторым выходом неисправности устройства , вход пуска устройства и выход генератора тактовых импульсов соеди-. нены соответственно с первым и вторым входами блока пуска-останова, выход которого соединен с вторыми входами четвертого и пятого элементов И, выход четвертого элемента И соединен с нулевым входом триггера р(;жйма, вторым установочным входом счетчика тактов и первыми установочными входами регистра программ первого и второго регистров адреса, выход- которого соединен с адресными входами первого блока памяти, выход первого блока памяти соединен с первым информационным вхо- . дом первого регистра адреса, первый адресный выход которого соединен спервым входом седьмого элемента И, выход которого соединен с управляющим входом второго блока памяти, второй адресный выход первого регистра адреса соединен с адресным входом второго блока памяти, выходы которого соединены с первыми входами блока элементов ИЛИ, выходы микроопераций третьего блока памяти соединены с вторыми входами блока элементов ИЛИ, выход ко- 15 торого является выходом микроопераций устройства, выход регистра программы соединен с адресным входом третьего блока памяти, первый управляющий выход которого соединен с вторым входом 20 шестого элемента И и вторым установочным входом регистра программ, второй и третий управляющие выходы третьего блока памяти соединены соответственно с вторым входом второго элемента И и 25 вторым установочным входом первогр регистра адреса, третьим установочным входом регистра программ, третьим установочным входом счетчика тактов, установочным входом регистра команд з0 И счетным входом счетчика команд, выход которого является выходом адреса устройства, выход блока памяти, о тличающееся тем, что, с целью повышения достоверности функционирования и быстродействия устройства, в него введены регистр теста, блок коррекции, второй коммутатор, блок элементов И, восьмой элемент И, элемент ИЛИ, элемент задержки, сумматор по модулю два, причем информационный вход устройства соединен с информационным входом блока коррекции, выход которого соединен с единичным установочным входом счетчика тактов, информационный выход преобразователя кодов допол нения и выход поля дополнения регистра команд соединены соответственно с первым и вторым информационными входами второга коммутатора, выход которого соединен с информационными входами счетчика тактов, второй управляющий выход третьего блока памяти соединен с первым установочным .входом регистра теста, первым входом блока элементов И и через элемент задержки с первыми управляющими входами второго коммутатора, единичный выход триггера режима соединен с вторым уп10

дом сумматора по модулю два, выход которого соединен с вторым информационным входом второго регистра адреса, третий управляющий выход третьего блока памяти соединен с вторым установочным входом второго регистра адреса, выход начального адреса микрокоманд соединен с вторым входом блока элеравляющим-входом второго коммутатора, первым управляющим входом блока коррекции, входом первого элемента НЕ, первым входом сумматора по модулю дйа и инверсным входом третьего элемента И, выход четвертого элемента И соедииен с вторым установочным входов регистра тестов, выход которого соединен с .вторым информационным входом блока коррекции, выход пятого элемента И соединен с управляющим входом первого блока памяти, вторым управляющим входом блока коррекции, вторым входом седьмого элемента И, выход которогр соединен с управляющим входом третьего блока памяти, управляющий второй и третий адресные выходы первого регистра адреса соединены соответственно с инверсным входом восьмого элемента И, вторым информационным входом регистра программ, и вторым вхоментов И, выход которого соединен с вторым информационным входом первого регистра адреса, выходы второго блока памяти соединены с входами элементов ИЛИ, выходы которых соединены с первым информационным входом первого коммутатора, управляющий вход второго блока памяти соединен с вторым информационным входом первого коммутатора, выход которого соединен с третьим входом блока пуска-останова, выход блока элементов ИЛИ соединен с информационным входом регистра теста. 2. Устройство по п. Г, о т л и чающееся тем, что блок коррекции содержит первый и второй регистры, дешифратор, первый и второй элементы задержки, сумматор по МОДУ.ЛЮ два, элемент И, элемент ИЛИ, причем первый и второй управляющие входы блока соединены соответственно с первым входом элемента И и входом первого элемента задержки, выход которого соединен с синхронизирующими входами первого и второго регистров и через второй элемент задержки - с вторым входом эле- ме.нта И, выход второго элемента И соединен с управляющим входом дешифратора, выход которого соединен с входами элемента ИЛИ, выход которого яв25968815

ляется выходом блока, первый информаг

ционный вход блок Соединен с информационным входом первого регистра и пер вым входом сумматора.по модулю два, выход которого соединен с информационными .входами второго регистра, второй информационный вход блока и выход первого регистра соединены соответственно с первым и вторым информацион|ными входами дешифратора, выход второго регистра соединен с третьим информационным входом дешифратора и вто рым входом сумматора по модуле два.

26 Источники информации.

принятые во внимание при экспертизе

1. Авторское свидетельство СССР W 503239, кл. G 06 F 9/06, 1976.

2.Авторское свидетельство СССР № «бОёО, кл. G Об F 9/06, 197.

3.Авторское свидетельство СССР № , кл. G 06 F 9/06, 1980.

. Авторское свидетельство СССР № 7910t, кл. G Об F 9/06, 1980. (птотип) .

Фиг. 2

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления | 1983 |

|

SU1142833A1 |

| Микропрограммное устройство управления | 1986 |

|

SU1381506A1 |

| Устройство для микропрограммного управления и контроля | 1987 |

|

SU1497621A1 |

| Микропрограммное устройство для тестового диагностирования и управления | 1984 |

|

SU1242946A1 |

| Микропрограммное устройство управления | 1988 |

|

SU1621027A1 |

| Устройство для программного управления | 1989 |

|

SU1656498A1 |

| Устройство для обучения | 1987 |

|

SU1559366A1 |

| Микропрограммный процессор | 1981 |

|

SU980095A1 |

| Устройство для управления восстановлением микропрограмм при сбоях | 1982 |

|

SU1056193A1 |

| Микропрограммное устройство управления | 1987 |

|

SU1490676A1 |

Фиг.

(риг4

5) Формат диагностичеспол команды Mgi

Фиг.5

Фиг. 6 ton НеООЮ Я ЮО Л. Л ||д //// 1(,ОП1 Ис-ОПО 7

Фиг.в

«vj

Авторы

Даты

1982-10-23—Публикация

1981-03-31—Подача