I

Изобретение относится к области вычислительной техники и может найти применение в различных устройствах ввода цифровой информации.

Известны устройства для формирования контрольных кодов чисел, содержащие элементы И, ИЛИ Н НЕ и выпйлняющие формирование контрольного остаточного кода по модулю 3 1|.

Недостаток известных устройств состоит в их аппаратурной сложности.

Наиболее близким к данному изобретению по сущности технического решения является устройство для формирования контрольного кода чисел, содержащее дешифратор дополнений, первая и вторая группы входов которого являются первой и второй группой входов устройства, а управляющий вход - вход,ом.- главных тактов, и первый элемент И, управляющий вход и выход которого являются соответственно входом опро са наличия., сбоя и выходом наличия сбоя устройства.

Недостаток этого устройства заключает ся в его аппаратурной сложности.

Цель изобретения состоит в сокращении аппаратурных затрат.

Поставленная цель достигается Tei, что в устройство введены элемент ИЛИ, второй элемент И и распределитель, причем входы

элемента ИЛИ соединены соответственно с выходом второго элемента И и первым выходом деши(})ратора дополнений, второй выход которого и вход дополнительиых так-тов подключены к соответствующим входам второго элемента И, выход элемента ИЛИ

и вход начальной установки устройства соединены соответственно с входом сдвига и |Входом начальной установки расп1ределйтеля, первый и второй выходы которого являются выходами контрольного кода устройства,

третий выход распределителя подключен к входу первого элемента И.

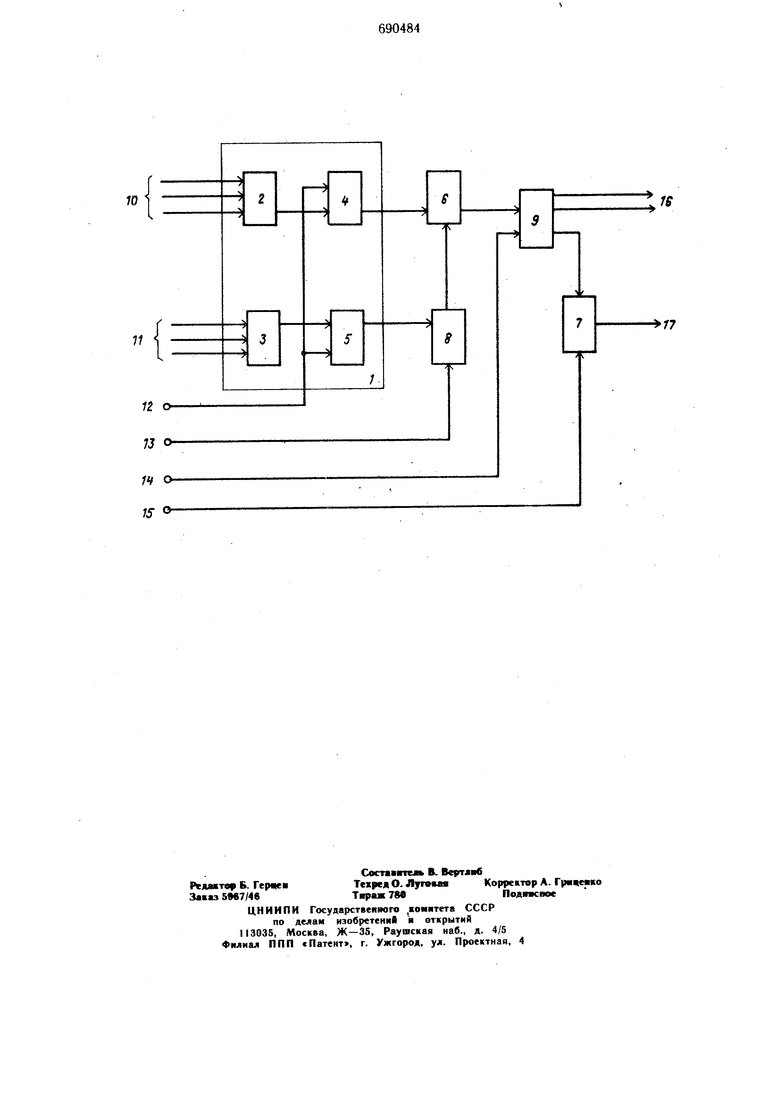

На чертеже показана блок-схема устройства. Устройство содержит дешифратор 1 дополнений, включающий элементы ИЛИ 2 и 3 и элементы И 4 и 5, элемент ИЛИ 6,

первый 7 и второй 8 элементы И, распределитель 9, первую 10 и вторую 11 группу входов устройства,- вход 12 главных тактов

и вход 13 дойолнительных тактов устройства; вход 14 начальной устновки и вход 15 опроса наличия сбоя, выходы 16 контрольного коде числа и выход 17 наличия сбоя.

Устройство производит формирование контрольного символа и контроль правильности его обработки. Для этого используется принцип «кратности трем, заключающийся в том, Что величина контрольного символа ; должна дополнять число до кратности трем. При первичном вводе чисел устройство производит формирование контрольного символа.

При вычислениях и передачах чисел в устройстве аналогично формируртся контрольный Ьимвол и осуществляется контроль полученного контрольного символа на райенство трем, означающей правильность. обработки информации и вычислений.

Устройство работает следующим образом,

Перед подачей числа в устройство по. входу 14 производится начальная установка кольцевого трехбитного распределителя 9 путем записи состояния три (двоичный код

Oil)..:

Далее при лодаче каждого разряда числа, Синхронизированного тактами контроля по входу 12; вырабатывается контрольный симвоп. . ;,;,, .,:,. ,. . : ; г; :

На входы первой группы входов 10 поступают числа два, пять, восемь, требующие одинакового дополнения до кратности трем равного единице. Объединение входов Происходит на элементе ИЛИ 2. На входы второй группы входов 11 поступают числа один, четыре, семь, требующие дополнения до Kpail ности трем равного двум. Объединение вхо; до происходит на элементе ИЛИ 3.i

На выходах элементов И 5 и 4 в момент возникновения такта на входе 12 формируют ся соответственные сигналы дополнений -- один и два. Сигнал с выхода элемента И 4 чероз элемент ИЛИ 6 поступает на вход распределителя 9, вызывая один сдвиг. Сигнал с выхода элемента И 5 поступает На второй элемент И 8 и пОйощью дополнительного такта на входе IB вйзыйает на выходе второго элемента И 8 два импульса которые через элемент ИЛИ 6 поступают на вход сдвига распределителя 9, вызывая два сдвига.. - .

,i.,:J«f- -ii S -Ws ;V--S-.-i:

Значение контрольного символа формируется на выходах 16 распределителя 9.

По окончании обработки чисел в устройство поступает сигнал на вход 15, при помощи которого выявляется отсутствие тройки в распределителе 9. Признаком отсутствия тройки является наличие единицы в третьем разряде распределителя 9, выход которого подключен к первому элементу И 7.

Отсутствие тройки фиксируется сигналом на выходе 17 с приходом сигнала на вход 15.

Следует отметить, что при формировании остатков по модулю больщему чем три, увеличивается соответственно число групп входов дешифратора дополнений, число разрядов распределителя и число дополнительных тактов.. ..

Формула изобретения

Устройство для формирования контрольного кода числа, содержащее дешифратор дополнений, первая и вторая труппа входов которого является первой и второй труппой входов устройства, а управляющий вход - входом главных тактов, и первый элемент И управляющий вход и выход которого нвляютсй соответственно входом опроса наличия сбоя и выходом наличия сбоя устройства, отличающееся тем, что, с целью сокращения аппаратурных затрат, в устройство введены элемент ИЛИ, второй элемент И и распределитель, причем входы элемента ИЛИ соединены .соо1тветственно с выходом второгоэлемента И и первым выходом деЩифратора дополнений, второй выход которого и вход дополнительных тактов подключены к соот:ветствующим входам второго элемента И, выход элемента ИЛИ и вход начальной установки устройства соединены соответственно с входом сдвига и 1входом начальной установки распределителя, первь1Й и второй выходы которого являются выходами контрольного кода устройства, третий выход распределителя подключён к входу первого элемента И. ;;;.. /;:.-

Источники, информации, принятые вО внимание при экспертизе 1. Селлере Ф. Методы обнаружения в работе ЭЦВМ. М., «Мир, 1972. 2. Авторское свидетельство СССР Ль 511592, кл. G 06 f 11/08, 1974.

ТО

re

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для формирования контрольного символа числа | 1974 |

|

SU511592A1 |

| Устройство для контроля информации по модулю три | 1976 |

|

SU634282A1 |

| Устройство для исправления ошибок | 1990 |

|

SU1783622A1 |

| ПРОЦЕССОР ПОВЫШЕННОЙ ДОСТОВЕРНОСТИ ФУНКЦИОНИРОВАНИЯ | 2010 |

|

RU2439667C1 |

| Устройство кодирования-декодирования числовых последовательностей | 1990 |

|

SU1809541A1 |

| Устройство кодирования и декодирования информации | 1990 |

|

SU1783628A1 |

| ПРОЦЕССОР ДЛЯ ЦИФРОВОЙ СИСТЕМЫ ОБРАБОТКИ ДАННЫХ | 1971 |

|

SU305477A1 |

| Устройство для отображения информа-ции HA эКРАНЕ элЕКТРОННОлучЕВОйТРубКи | 1979 |

|

SU822242A1 |

| Генератор -ичного перестановочного кода | 1978 |

|

SU746478A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛОМ СВЯЗИ | 1992 |

|

RU2043652C1 |

Авторы

Даты

1979-10-05—Публикация

1977-06-09—Подача