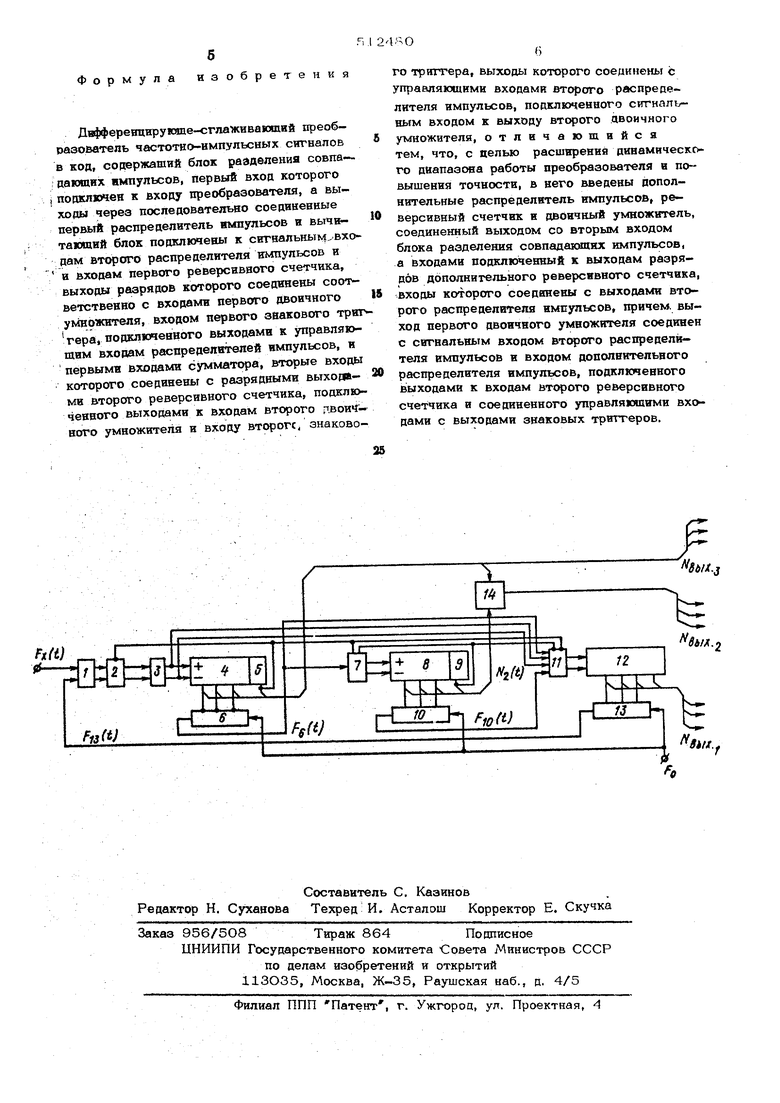

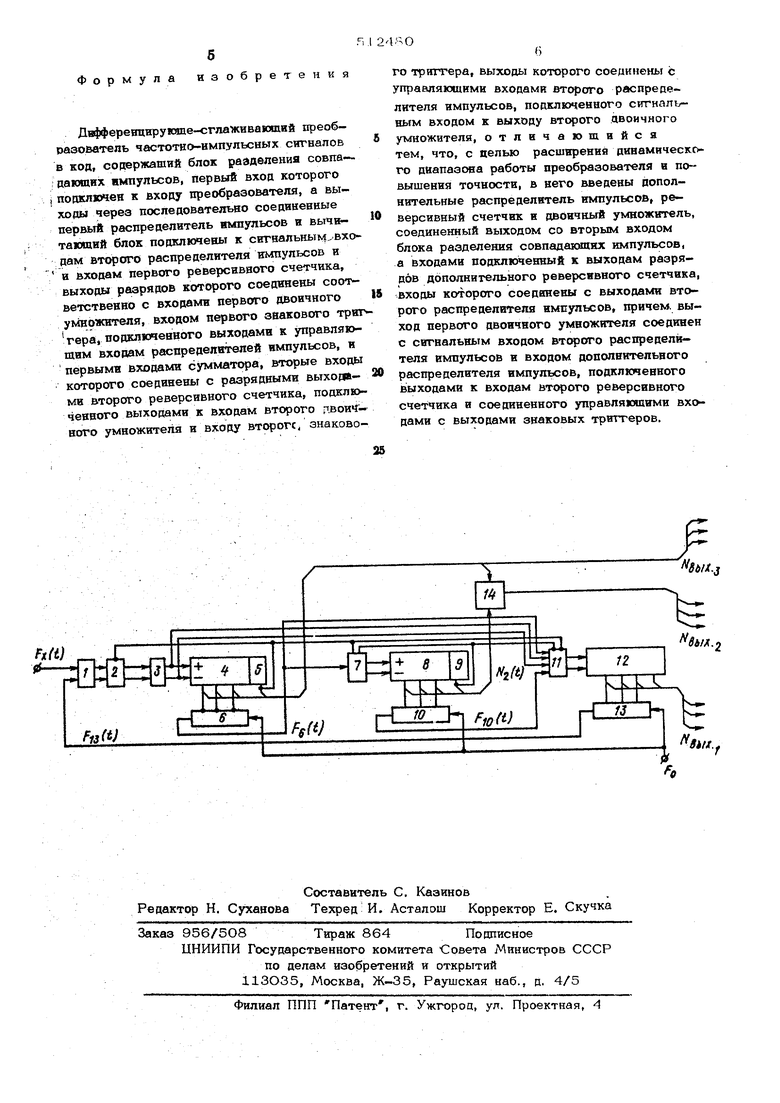

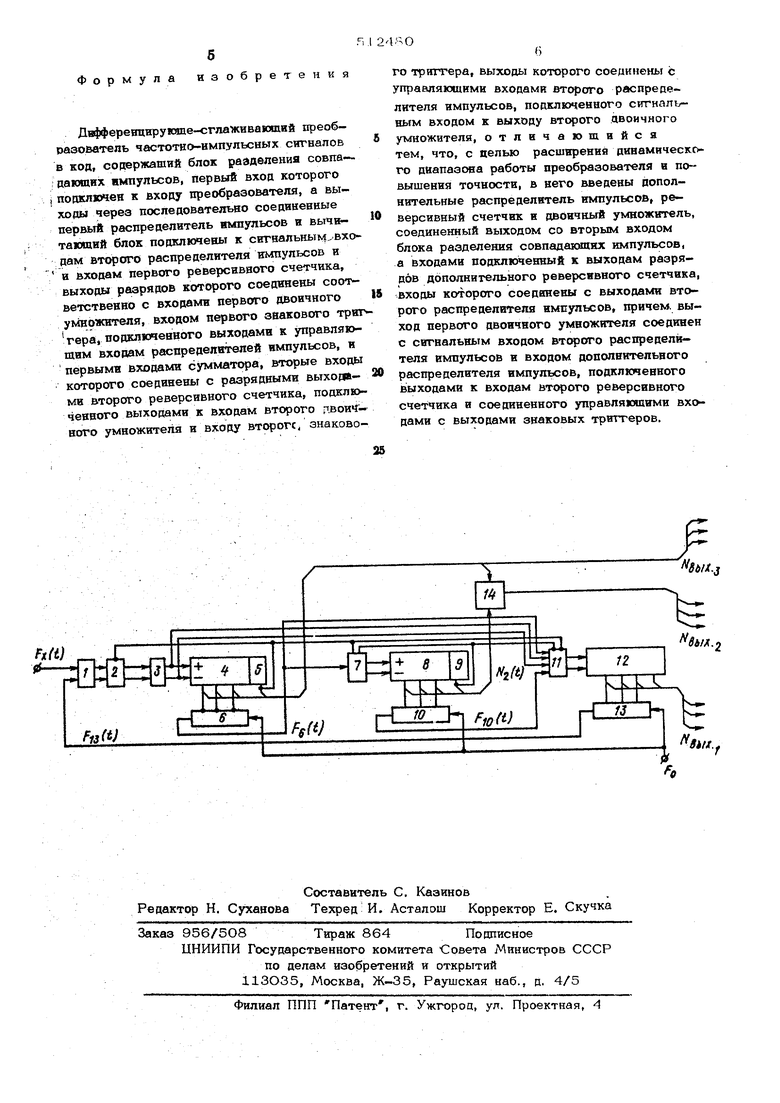

;«множителя соединен с сигнальным входом второго распределителя импульсов н входом пополнительного распределителя импульсов, иоцключенного выходами к входам второго реверсивного счетчика и соединенного управляюшими входами с выходами знаковых Триггеров. На чертеже изображена блок-схема пред лагаемого преобразователя. Преобразователь содержит блок 1 разделения совпадающих импульсов, ра:пределитель 2 импульсов, вычитающий блок 3, реверсивный счетчик 4 со знаковым триггером 5 и двоичным умножителем 6, распределитель 7 импульсов, реверсивный счет чик 8 со знаковым триггером 9 н двоичны З Множйтелем 10, распределитель 11 импул сов, реверсивный счетчик 12, двоичный ум ножитель 13 и сумматор 14. Вход F ( t ) преобразователя через блок 1 разделения совпадающих импульсов, распределитель 2 и вычитающий блок 3 соединен с суммирующим входомреверсивного счетчика 4 и через распределитель 11 - с реверсивным счетчиком 12. Вычитающий вход реверсивного счетчика 4 через вычитающий блок 3, распределитель 2 и блок 1 разделения соединен с выходом двоичного умножителя 13, а также через распределитель 11 - с входом реверсивного счетчика 12. Выходы двоичных умножителей 6 и 10 соединены через распределитель 11 со счетчиком 12. Выход умножителя 6 через распределитель 7 соединен с счетчиком 8. Выход N«u,« счетчика 4 ВЫХ 3 служит для измерения ускорения сигнала f ., ( t ). Сумма сигналов с выходов сче чинов 4 и 8, образующаяся в сумматоре 14 служит для измерения скорости сигнала t ), выход „5t,,x i счетчика 12 ГЛ1 предназначен для цзмерения сигнала . Преобразователь работает следующим образом. Измеряемая частота поступает через блок 1, распределитель 2 н вычитающий блок 3 на входы реверсивных сче -чиков 4 и 12. При этом значения выходов преобразователя описываются выражениями Bb-x., i Г N2it)--2Tr,Jr,(t)dt, . ,(i)-N,(t) NBb,x/),,(t)dt, где n, чиках NBb,x,(t).N2(i), )-r кушие значевия чисея в счетчиках 12, 8, 4, прергтавленные и йрямом коде с фиксированной запятой; Mg: (i)- сумма значенвй счетчиков 4 , которая может вычисляться в сумматоре 14, нредстпвляет несмещенную сглаженную опенку скоростн измейв)8ВГа частоты. Уравнения (1) в операторной форме имеют вид )-, ). BbfXjl) pTj a{P)-.,,,,(),), ВЫХ,(Р)2(Р) (р), (pil, BblXi(P) f БЫх,{Р Значение bix.f ,,, являющиеся корнями с истемы уравнений (2), имеют вид l+рГг + Р Тг-Тэ Вып) Го i+pT -t-P TjiTa pST -T -Tg ,.Р).р.-Т Т-о i-pTa p2T2-VPT,.T,.T3 ,Tx(p} ВЫх, Ч 2 i+pTj,+р Г2Тз+ р Т -Т -Тд Наличие оператора Р в выражении (5) указывает на возможность использования значения N-DL.V ( t ) для оценки второй производной сигнала fv ( t ), равенство первых трех и первых двух коэффициентов в числителе и знаменателе выражений (3) и (4) указывает на отсутствие частоты и ее первой производной. и я Формула изобретен Двфференцируюше-сглаживаюшвй преобоазоватеяь частотно-импульсных сигнапов в код, соцержаший блок разделения совяа- пающнх вмпульсов, первыб вход которого I подключен к входу преобразователя, а выходы через последозатеяьво соединенные первый распре делитель импульсов и вычи тающий блок подключевь к сигнальныц Входам второго распределителя импульсов и Л и входам первого реверсивного счетчика, выходы разрядов которого соединены соответственно с входами первого двоичного умножителя, входом первого знакового триг гера, подклкяениого выходами к управляк шим входам распределителей импульсов, и первыми входами сумматора, вторые входы которого соединены с разрядными выходами второто реверсивного счетчика, подклю ченного выходами к входам второго даоичного умножителя и входу второгс, знаковоо триггера, выходы которого соединены с правляющими входами второго распределителя импульсов, подключенного сигнальным входом к выходу второго двоичного умножителя, отличающийся тем, что, с целью расширения динамического диапазона работы преобразователя н повышения точности, в него введены дополнительные распределитель импульсов реверсивный счетчик и двоичный умножитель, соединенный выходом со вторым входом блока разделения совпадающих импульсов, а входами подключенный к выходам разрядов дополнительного реверсивного счетчика, входы которого соединены с выходами второго распределителя импульсов, причем, выход первого двоичного умножителя соединен с Сигнальным входом второпго распределителя импульсов и входом дополнительного распределителя импульсов, подключенного выходами к входам второго реверсивного счетчика и соединенного управляющими входами с выходами знаковых триггеров.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для дифференцирования частотно-импульсных сигналов | 1980 |

|

SU920722A1 |

| Частотно-импульсное дифференцирующее устройство | 1977 |

|

SU739555A1 |

| Цифровой преобразователь координат | 1985 |

|

SU1257638A1 |

| Цифровой корреляционный фазометр | 1980 |

|

SU943598A1 |

| Устройство для регулирования расхода | 1984 |

|

SU1171759A1 |

| Цифровой преобразователь координат | 1977 |

|

SU742944A1 |

| Преобразователь частота-код | 1974 |

|

SU533877A1 |

| Процентный время-импульсный преобразователь | 1979 |

|

SU968896A1 |

| ДИФФЕРЕНЦИРУЮЩЕ-СГЛАЖИВАЮЩИЙ ЧАСТОТОМЕР | 1970 |

|

SU262513A1 |

| Инкроментный умножитель аналоговых сигналов | 1982 |

|

SU1057970A1 |

Авторы

Даты

1976-04-30—Публикация

1974-07-05—Подача