роговых элементов, подключенных входами к выходу вычитающего узла, а выходами - к информационным входам приоритетного блока, соединенного стробирующим входом со стробирующим входом накапливающего сумматора и с выходом элемента И, а выходами - с выходами кода приращения следящего аналогоцифрового преобразователя и с информационными входами накапливающего сумматора, подключенного управля1ощим входом к выходу нуль-органа и к выходу знака рассогласования следящего аналого-цифрового преобразователя, а выходами разрядов - к входам цифроаналогового преобразователя, соединенного выходом с первым входом вычитающего узла, подключенного вторым входом к информационному входу следящего аналого-цифрового преобразователя, а выходом - к входу нуль-органа, причем входы элемента И являются соответственно тактовым входом и входом разрешения преобразования следящего аналого-цифрового преобразова,теля,-а выход знакового разряда и выходы остальных разрядов накапливающего сумматора являются выходом знака кода результата и выходами модуля кода результата преобразования следящего аналого-цифрового преобразователя соответственно.

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой инкрементный умножитель | 1982 |

|

SU1057971A1 |

| Инкрементный умножитель аналоговых сигналов | 1983 |

|

SU1113820A1 |

| Устройство для вычисления полиномиальной функции от аналогового аргумента | 1990 |

|

SU1737444A1 |

| Аналого-цифровой инкрементный дифференциатор | 1985 |

|

SU1343410A1 |

| Аналого-цифровое устройство для вычисления полиномиальной функции | 1985 |

|

SU1262530A1 |

| Следящий аналого-цифровой преобразователь | 1988 |

|

SU1562972A1 |

| Многоканальное адаптивное аналого-цифровое устройство | 1987 |

|

SU1520660A1 |

| Аналого-цифровой вычислитель логарифмической функции | 1985 |

|

SU1247904A1 |

| Устройство для поворота вектора (его варианты) | 1982 |

|

SU1078431A1 |

| Устройство для вычисления коэффициентов Фурье | 1985 |

|

SU1283790A1 |

1. ИНКРЕМЕНТНЫЙ УМНОЖИТЕЛЬ АНАЛОГОВЫХ СИГНАЛОВ, содержащий сумматор-.вычитатель, выходы которого являются выходом умножителя, и триггер управления, соединенный счетным входом с входом тактовых импульсов, а первым и вторым выходами - с входами разрешения преобразования первого и второго следящих аналого-цифровых преобразователей соответственно, каждый из которых подключен информационным входом к входу соответствующего сомножителя умножителя, а выходами модуля кода результата преобразования. - к соответствующей группе информационных входов первого коммутатора, отличающийся тем, что, с целью расширения частотного диапазона перемножаемых сигналов, в него дополнительно введены второй и третий коммутаторы, сумматоры по модулю два и блок сдвига кода, соединенный выходами с информационными входами сумматора-вычитателя, информационными входами - с выходами первого коммутатора , а.управляющими входами с выходами второго коммутатора, подключенного первой и второй группами информационных входов к выходам кода приращения первого и второго следящих аналого-цифровых преобразователей соответственно, тактовые входа которых соединены с входом тактовой частоты умножителя и со стробирующим входом сумматора-вычитателя, подключенного управляющим входом к выходу третьего коммутатора, соединенного информационными входами с выходами первого и вторюго сумматоров по модулю два, входы первогЬ из которых подключены к выходу знака кода результата преобразования первого следящего аналого-цифрового преобразователя и к выходу знака рассогласования второго следящего аналого-цифрового преобразователя , а входы второго сумматор а по модулю два соединены с выходом СП знака кода результата преобразования второго следящего аналого-цифрового ;о преобразователя и с выходом знака рассогласования первого следящего аналого-цифрового преобразователя, причем управляющие входы коммутаторов подключены к первому и второму выходам триггера управления соответст венно. 2. Умножитель по п. 1, отличающийся тем, что каждый следящий аналого-цифровой преобразователь содержит вычитающий узел, нульорган, элемент И, цифроаналоговый преобразователь, накапливающий сумматор, приоритетный блок и группу пс

. Изобретение относится к автоматике и вычислительной технике и может найти применение в аналого-цифровых и гибридных вычислительных устройствах и системах с различной формой представления информации для перемножения аналоговых сигналов с представлением результата в цифровой форме.

Известен умножитель аналоговых си1- налов с цифровым выходом, содержащий П1эеобрааователи аналог-частота, блок преобразования длительности интервала в напряжение и счетчик результатаj lj.

Известен умножитель аналоговых сигналов с цифровым выходом, содержащий компораторы, генератор тактовых импульсов, делители частоты, генератор линейно-изменяющегося напряжения, распределитель импульсов, элементы И, ИЛИ, И-НЕ, ИЛИ-НЕ, ключи и счетчик результата С2 X

Недостатком умножителей является ограниченный частотный диапазон перемножаемых сигналов.

Наиболее близким к предлагаемому

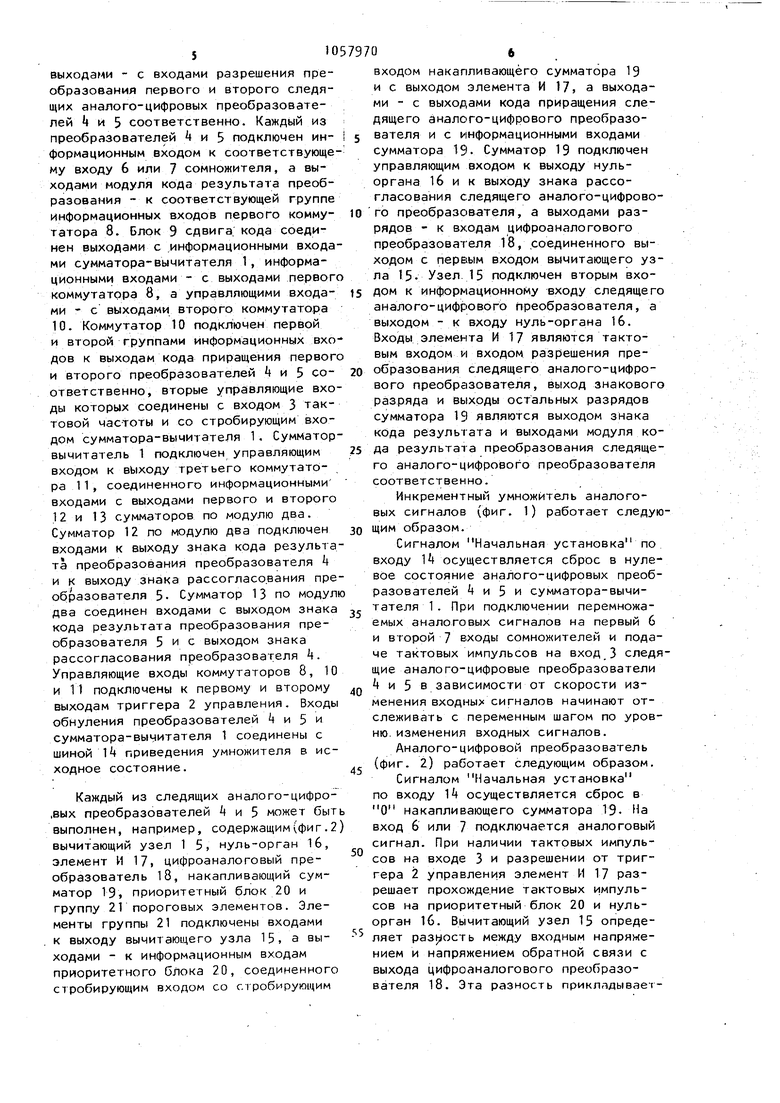

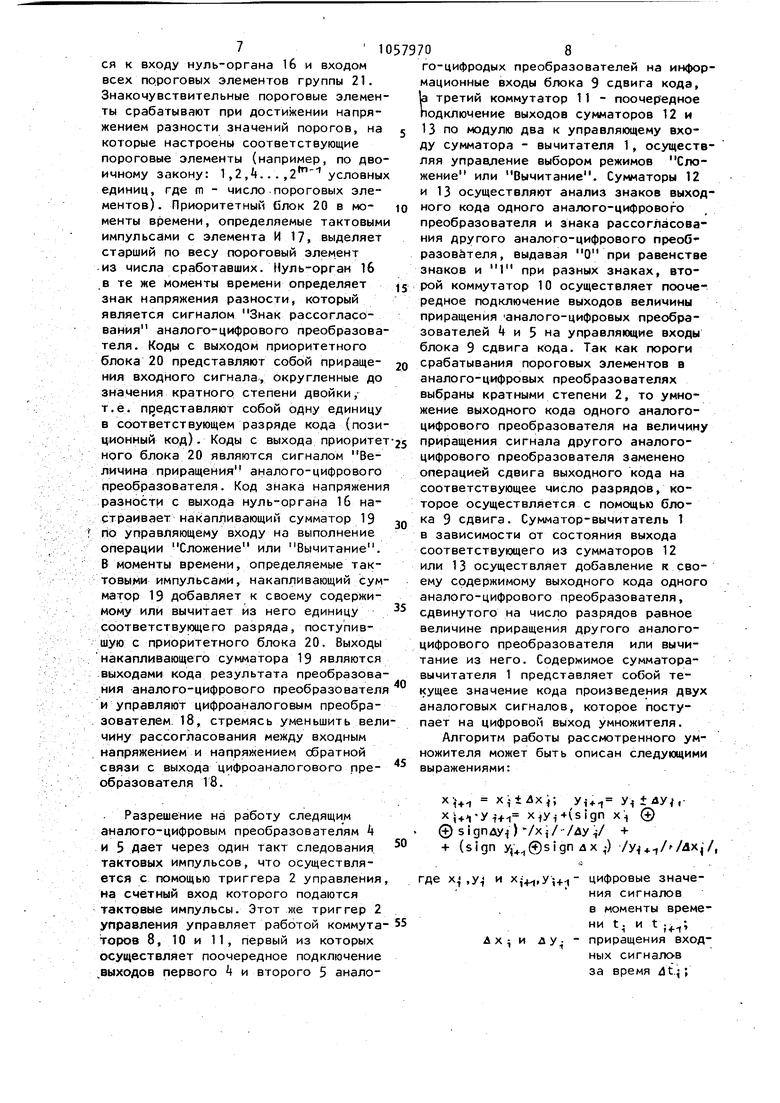

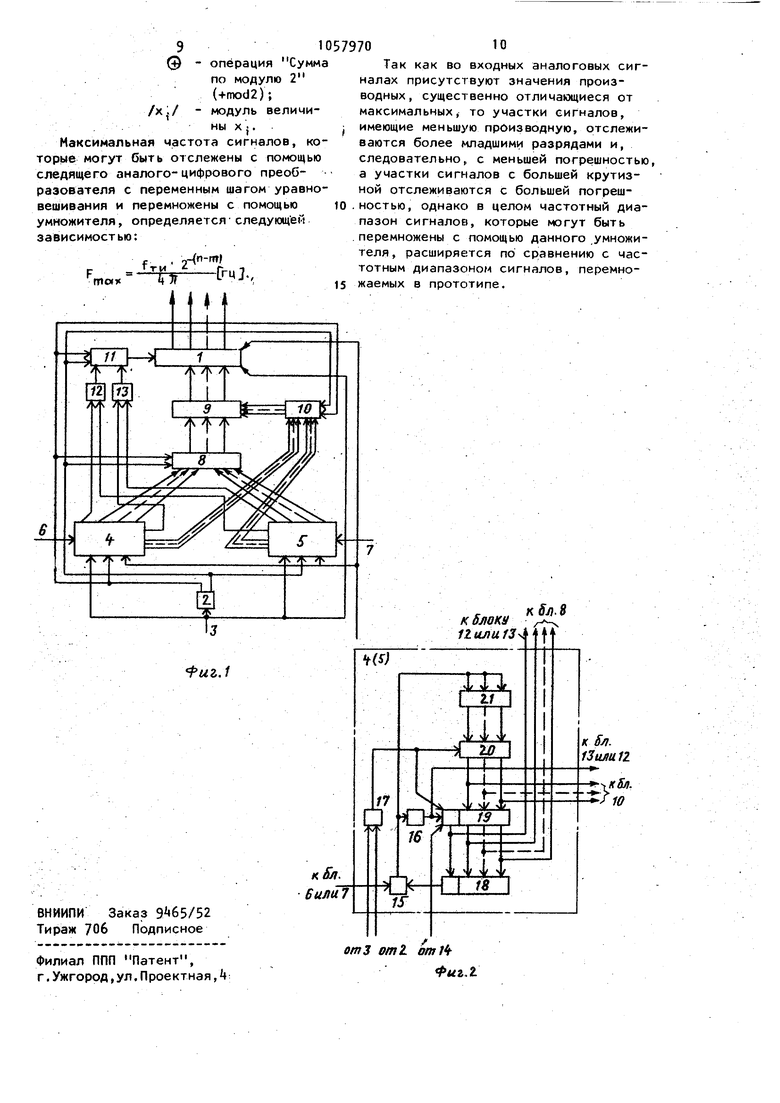

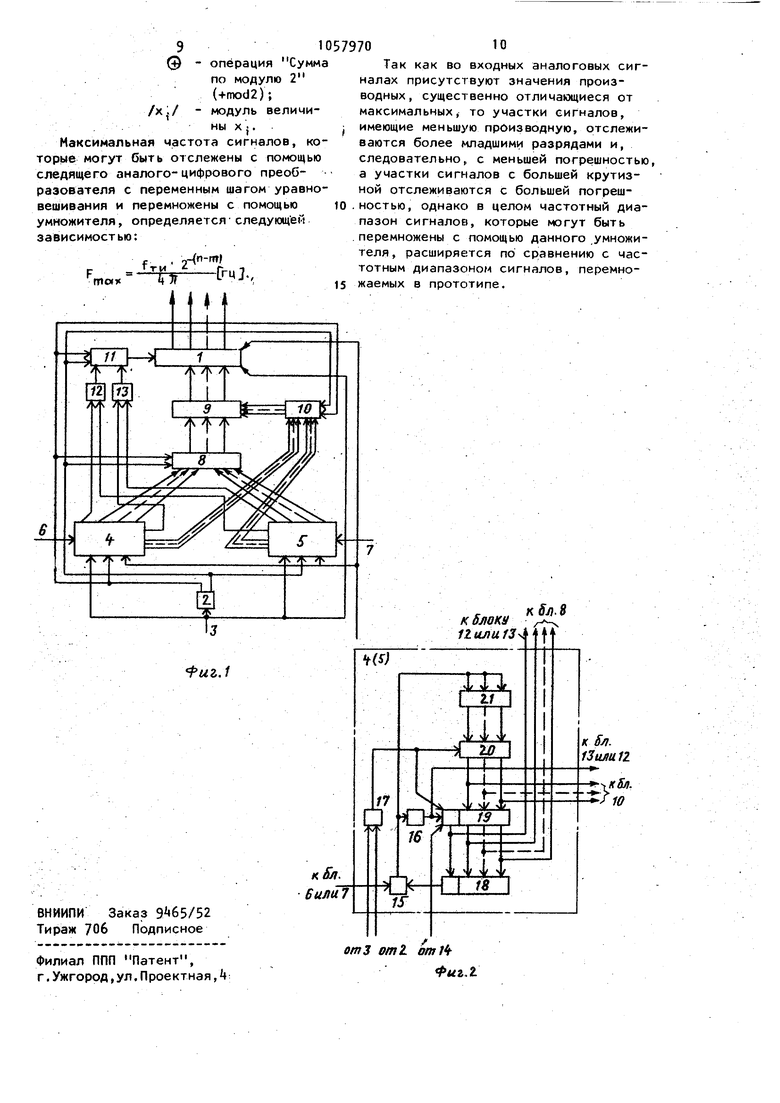

по технической сущности является ин. умножитель аналоговых сигналов, содержащий сумматор-вычитатель выходы которого являются выходом умножителя, и триггер управления, соединенный счетным входом с входом тактовых импульсов, а первым и вторым выходами - с в 1одами разрешения преобразования первого и второго следящих аналого-цифровых преобразователей соответственно, каждый из которых подключен информационным входом к входу соответствующего сомножителя умножителя, а выходами модуля прямого и инверсного кода результата преобразования - к соответствующей группе информационных входов первого коммутатора, соединенного выходами с информац 1онными входами cyMMatopa-вычитателя, подключенного управляющим входом к выходу элемента ИЛИ, соединенного входами с выходами знака рассогласования первого и второго следящих аналого-цифровых преобразователей прямые и инверсные выходы знака рассогласования которых подключены к соответствующим управляющим входам первого ког4мутатора. Каждый следящий аналого-цифровой преобразователь содержит компаратор, подключенный сигнальными входами к информационному входу следящего аналого-цифрового преобразователя и выходу цифроаналогового преобразователя, управляющим входом - к первому управляющему входу следящего аналого-цифрового преобразователя, а прямым и инверсным выходами - к прямому и инверсному выходам знака рассогласования следящего аналого-цифрового преобразователя и к суммирующему и вычитающему входам реверсивного счетчика, соединенного) выходами разрядов с входами цифроаналогового преобразователя З Недостатком умножителя является ограниченный частотный диапазон пере множаемых .аналоговых, сигналов, в частности, максимальная частота изме нения входных сигналов ограничена вы ражением вида г .Ij42-l- -Гги 1 VnaxТПТ где fr; - частота следования тактовых импульсов; 2 - вес единицы младшего разря да п-разрядного аналогоцифрового преобразователя. Цель изобретения расширение час тотного диапазона пёре.множаемых сигналов.V Для достижения цели в инкрементны умножитель аналоговых сигналов, содержащий сумматор-вычитатель, выходы которого являются выходок умножителя и триггер управления, соединенный счетным входом с входом тактовых импульсов, а первым и вторым выходами с входами разрешения преобразования первого и второго следящих аналогоцифровых преобразователей соответственно, каждый из которых подключен информационным входом к входу соответствующего сомножителя умножителя, а выходами модуля кода результата преобразования - к соответствующей группе информационных входов первого коммутатора, дополнительно введены второй и третий коммутаторы, суммато ры по модулю два и блок сдвига кода-, соединенный выходами с информационными входами сумматора-вычитателя, информационными входами - с выходами первого KOMMytaTopa, а управляющими входами - с выходами второго коммутатора, подключенного первой и второ группами информационных входов к выходам кода приращения первого и второго следящих аналого-цифровых преоб разователей соответственно, тактрвые входы которых соединены с входом так товой частоты умножителя и со стробирующим входом сумматора-вычитателя подключенного управляющим входом к выходу третьего коммутатора, соедине ного информационными входами с выходами первого и второго сумматоров по модулю два, входы первого из кото рых подключены к выходу знака кода результата преобразования первого следящего аналого-цифрового преобразователя и к выходу знака рассогларования второго следящего аналогоцифрового преобразователя, а .входы второго сумматора по модулю два соединены с выходом знака кода результата преобразования второго следящего аналого-цифрового преобразователя и с выходом знака рассогласования перво го следящего аналого-цифрового преобразователя, причем управляющие входы коммутаторов подключены к первому и второму выходам триггера управления соответственно. При этом .каждый следящий аналогоцифроёой,преобразователь содержит вычитающий узел, нуль-орган, элемент И, цифроаналоговый преобразователь, на- . капливающий сумматор, приоритетный блок и группу пороговых элементов, подключенных входами к выходу вычитающего узла, а выходами - к информационным входам приоритетного блока, соединенного стробирующим входом со стробирующим входом накапливающего сумматора и с выходом элемента И, а выходами - с выходами кода приращения следящего аналого-цифрового преобразователя и с информационными входами накапливающего сумматора, подключенного управляющим входом к выходу нульоргана и к выходу знака рассогласования следящего аналого-цифрового преобразователя,, а выходами разрядов к входам цифроаналогового преобразователя, соединенного выходом с первым входом вычитающего узла, подключенного вторым входом к информационному входу следящего аналого-цифрового преобразователя, а выходом - к входу , нуль-органа, причем входы элемента И являются соответственно тактовым входом и входом разрешения преобразования следящего аналого-цифроэого преобразователя, а выход знакового разряда и выходы остальных разрядов накапливающего сумматора являются выходом знака кода результата и выходами модуля кода результата преобразования следящего аналого-цифрового преобразователя соответственно. На фиг. 1 изображена блок-схема инкрементного умножителя аналоговых сигналов; на фиг, 2 - блок-схема следящего аналого-цифрового преобразователя. Инкрементный умножитель (фиг. 1) содержит сумматор-вычитатель 1, выходы которого являются выходом умножителя, и триггер 2 управления, соединенный счетным входом с входом 3 тактовых импульсов, а первым и вторым 10 выходами - с входами разрешения преобразования первого и второго следящих аналого-цифровых преобразователей 4 и 5 соответственно. Каждый из преобразователей 4 и 5 подключен информационным входом к соответствующе му входу 6 или 7 сомножителя, а выходами модуля кода результата преобразования к соответствующей группе информационных входов первого коммутатора 8. Блок 9 сдвига кода соединен выходами с информационными входа ми сумматора-вычитателя 1, информационными входами - с выходами первог коммутатора 8, а управляющими входами - с выходами второго коммутатора 10. Коммутатор 10 подключен первой и второй группами информационных вхо дов к выходам кода приращения первог и второго преобразователей и 5 соответственно, вторые управляющие вхо ды которых соединены с входом 3 тактовой частоты и со стробирующим входом сумматора-вычитателя 1. Сумматор вычитатель 1 подключен управляющим входом к выходу третьего коммутатора 11, соединенного информационными входами с выходами первого и второго 12 и 13 сумматоров по модулю два. Сумматор 12 по модулю два подключен входами к выходу знака кода результа та преобразования преобразователя k и к выходу знака рассогласования пре образователя 5- Сумматор 13 по модул два соединен входами с выходом знака кода результата преобразования преобразователя 5 и с выходом знака рассогласования преобразователя k. Управляющие входы коммутаторов 8, 10 и 11 подключены к первому и второму выходам триггера 2 управления. Входы обнуления преобразователей 4 и 5 и сумматора-выуитателя 1 соединены с шиной 14 приведения умножителя в исходное состояние. Каждый из следящих зналого-цифро,вых преобразователей 4 и 5 может быт выполнен, например, содержащим(фиг.2 вычитающий узел 1 5, нуль-орган 16, элемент И 17, цифроаналоговый преобразователь 18, накапливающий сумматор 19, приоритетный блок 20 и группу 21 пороговых элементов. Элементы группы 21 подключены входами к выходу вычитающего узла 15, а выходами - к информационным входам приоритетного блока 20, соединенного С1робирующим входом со сгробирующим 06 входом накапливающего сумматора 19 и с выходом элемента И 17, а выходами - с выходами кода приращения следящего аналого-цифрового преобразователя и с информационными входами сумматора tS- Сумматор 19 подключен управляющим входом к выходу нульоргана 16 и к выходу знака рассогласования следящего аналого-цифрового преобразователя, а выходами разрядов - к входам цифроаналогового преобразователя 18, соединенного выходом с первым входом вычитающего узла 15- Узел.15 подключен вторым вхоДОм к информационному входу следящего аналого-цифрового преобразователя, а выходом - к входу нуль-органа 16. Входы элемента И 17 являются тактовым входом и входом разрешения преобразования следящего аналого-цифрового преобразователя, выход знакового разряда и выходы остальных разрядов сумматора 19 являются выходом знака кода результата и выходами модуля кода результата преобразования следящего аналого-цифрового преобразователя соответственно. Инкрементный умножитель аналоговых сигналов (фиг. 1) работает следующим образом. Сигналом Начальная установка по входу 14 осуществляется сброс в нулевое состояние аналого-цифровых преобразователей i и 5 и сумматора-вычитателя 1. При подключении перемножаемых аналоговых сигналов на первый 6 и второй 7 входы сомножителей и подаче тактовых импульсов на вход 3 следящие аналого-цифровые преобразователи и 5 в зависимости от скорости изменения входных сигналов начинают отслеживать с переменным шагом по уровню, изменения входных сигналов. Аналого-цифровой преобразователь (фиг. 2) работает следующим образом. Сигналом Начальная установка по входу 14 осуществляется сброс в О накапливающего сумматора 19- На вход 6 или 7 подключается аналоговый сигнал. При наличии тактовых импульсов на входе 3 и разрешении от триггера 2 управления элемент И 17 разрешает прохождение тактовых импульсов на приоритетный блок 20 и нульорган 1б. Вычитающий узел 15 определяет pa3hjocTb между входным напряжением и напряжением обратной связи с выхода цифроаналогового преобразователя 18. Эта разность прикладывается к входу нуль-органа 16 и входом всех пороговых элементов группы 21. Знакочувствительные пороговые элементы срабатывают при достижении напряжением разности значений порогов, на которые настроены соответствующие пороговые элементы (например, по двоичному закону: 1,2 ,... , условных единиц, где m - число пороговых элементов). Приоритетный блок 20 в моменты времени, определяемые тактовыми импульсами с элемента И 17, выделяет старший по весу пороговый элемент из числа сработавших. Нуль-орган 16 в те же моменты времени определяет знак напряжения разности, который является сигналом Знак рассогласования аналого-цифрового преобразователя. Коды с выходом приоритетного блока 20 представляют собой приращения входного сигнала, округленные до значения кратного степени двойки, т.е. п(эедставляют собой одну единицу в соответствующем разряде кода (позиционный код). Коды с выхода приоритет ного блока 20 являются сигналом Величина приращения аналого-цифрового преобразователя. Код знака напряжения разности с выхода нуль-органа 16 настраивает накапливающий сумматор 19 rib управляющему входу на выполнение операции Сложение или Вычитание. В моменты времени, определяемые тактовыми импульсами , накапливающий сумматор 19 добавляет к своему содержимому или вычитает из него единицу соответствующего разряда, поступившую с приоритетного блока 20. Выходы накапливающего сумматора 19 являются выходами кода результата преобразования аналого-цифрового преобразователя и управляют цифроаналоговым преобразователем. 18, стремясь уменьшить вел чину рассогласования между входным напряжением и напряжением обратной связи с выхода цифроаналогового преобразователя 18. Разрешение на работу следящим аналого-цифровым преобразователям 4 и 5 дает через один такт следования. тактовых импульсов, что осуществляется с помощью триггера 2 управления на счётный вход которого подаются тактовые импульсы. Этот же триггер 2 управления управляет работой коммута торов 8, 10 и 11, первый из которых осуществляет поочередное подключение .выходов первого 4 и второго 5 анало108 го-цифродых преобразователей на информационные входы блока 9 сдвига кода, la третий коммутатор 11 - поочередное подключение выходов сумматоров 12 и 13 по модулю два к управляющему входу сумматора - вычитателя 1, осуществляя управление выбором режимов Сложение или Вычитание. Сумматоры 12 и 13 осуществляют анализ знаков выходного кода одного аналого-цифрового преобразователя и знака рассогласования другого аналого-цифрового преобразовётеля, выдавая О при равенстве знаков и 1 при разных знаках, второй коммутатор 10 осуществляет поочередное подключение выходов величины приращения аналого-цифровых преобразователей t и 5 на управляющие входы блока 9 сдвига кода. Так как пороги срабатывания пороговых элементов в аналого-цифровых преобразователях выбраны кратными степени 2, то умножение выходного кода одного аналогоцифрового преобразователя на величину приращения сигнала другого аналогоцифрового преобразователя заменено операцией сдвига выходного кода на соответствующее число разрядов, которое осуществляется с помощью блока 9 сдвига. Сумматор-вычитатель 1 в зависимости от состояния выхода соответствующего из сумматоров 12 или 13 осуществляет добавление к своему содержимому выходного кода одного аналого-цифрового преобразователя, сдвинутого на число разрядов равное величине приращения другого аналогоцифрового преобразователя или вычитание из него. Содержимое сумматоравычитателя 1 представляет собой текущее значение кода произведения двух логовых сигналов, которое постут на цифровой выход умножителя. Алгоритм работы рассмотренного умителя может быть описан следующими ажениями: xu-i Uyy тЧ-1 (sign х © @ signAy)/х //лу ;;/ + + (sign y,®sign лх ,.) /у //ЛХ /, цифровые значех ,у и xj+.yU-i ния сигналов в моменты времени t. и t приращения входДX : и ЛУ . ных сигналов за время ut.; 0 - операция Сумм по модулю 2 (+mod2); /xj/ - модуль величи. .НЫ X j. Максимальная частота сигналов, ко торые могут быть отслежены с помощью следящего аналого-цифрового преобразователя с переменным шагом уравно вешивания и перемножены с помощью умножителя, определяется- следующей зависимостью: , Так как во входных аналоговых сигналах присутствуют значения производных, существенно отличающиеся от максимальных, то участки сигналов, имеющие меньшую производную, отслеживаются более младшими разрядами и, следовательно,, с меньшей погрешностью, а участки сигналов с большей крутизной отслеживаются с большей погрешностью, однако в целом частотный диапазон сигналов, которые могут быть перемножены с помощью данного умножителя, расширяется по сравнению с частотным диапазоном сигналов, перемножаемых в прототипе. К 6м КУ

Авторы

Даты

1983-11-30—Публикация

1982-09-17—Подача