1

Изобретение относится к вычислительной технике.

Известны запоминающие устройства, содержащие матрицу из г. двоичных запоминающих элементов на полевых транзистора селекторный коммутатор столбцов, селекторный коммутатор строк, переключатель режима работы, источники постоянного напряжения.

Цель изобретения - повыщение надежное ти устройства.

Предлагаемое устройство отличается те что оно содержит блок переменного напряжения, переключатель переменного напряжения, первый и второй ключи, нагрузочные полевые транзисторы, управляющий элемент, подключенный выходами к переключателю режима работы и через селекторный коммутатор столбцов - к первым выходам П двоичных запоминающих 1элементов матрицы, выходы которых подсоединены к источнику постоянного напряжения через нагрузочные полевые транзисторы, причем входы запоминающих элементов соединены через селекторный коммут

татор строк с переключателем переменного напряжения, подключенным к блоку переменного напряжения, и с первым ключом который подсоединен к источнику постояяного напряжения, а шина питания управляющего элемента подключена к источнику постоянного напряжения через второй ключ

Каждый из двоичных запоминающих алементов матрицы содержит два полевых транзистора с переменным порогом срабатывания и изолированными атворами, првЧем их истоки, стоки н затворы соеднн ны соответственно с первыми выходами, вторыми выходами и входами двоичного запоминающего элемента.

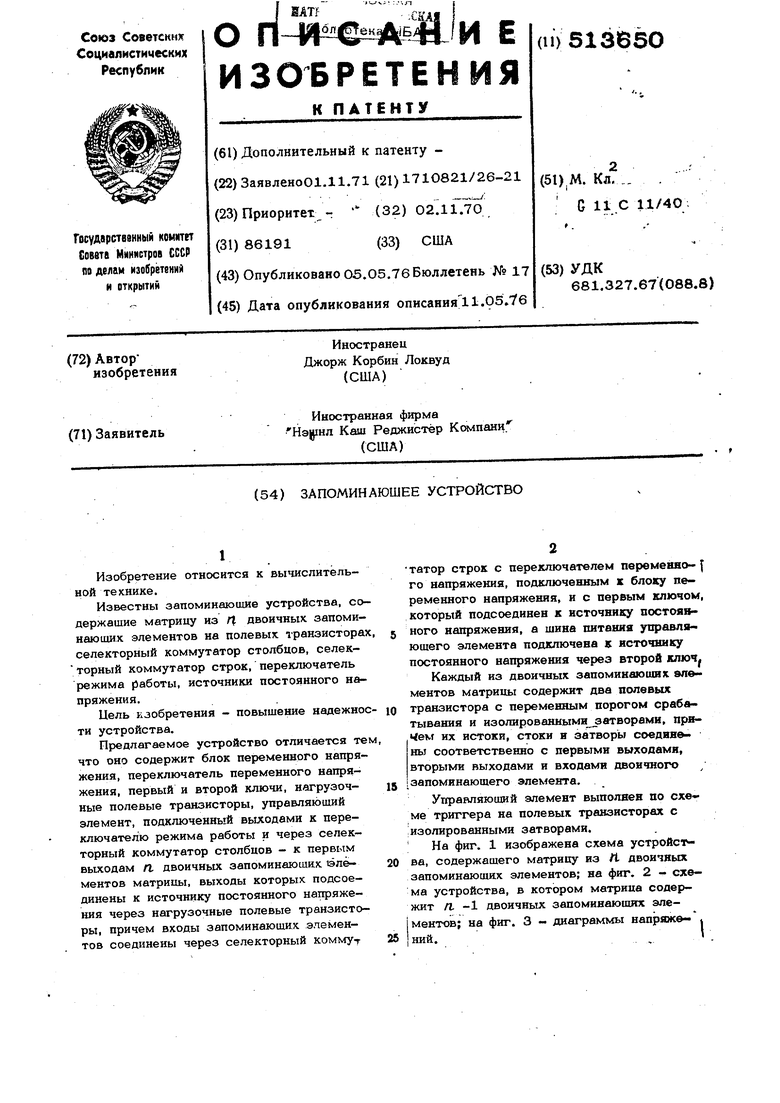

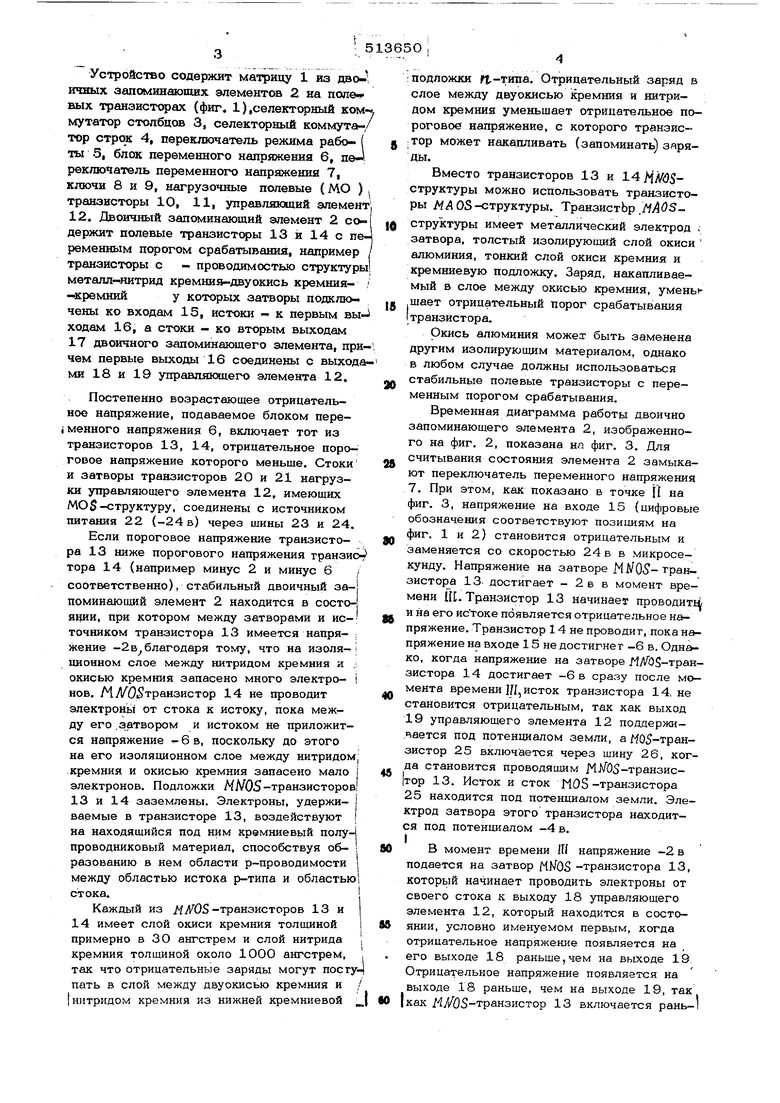

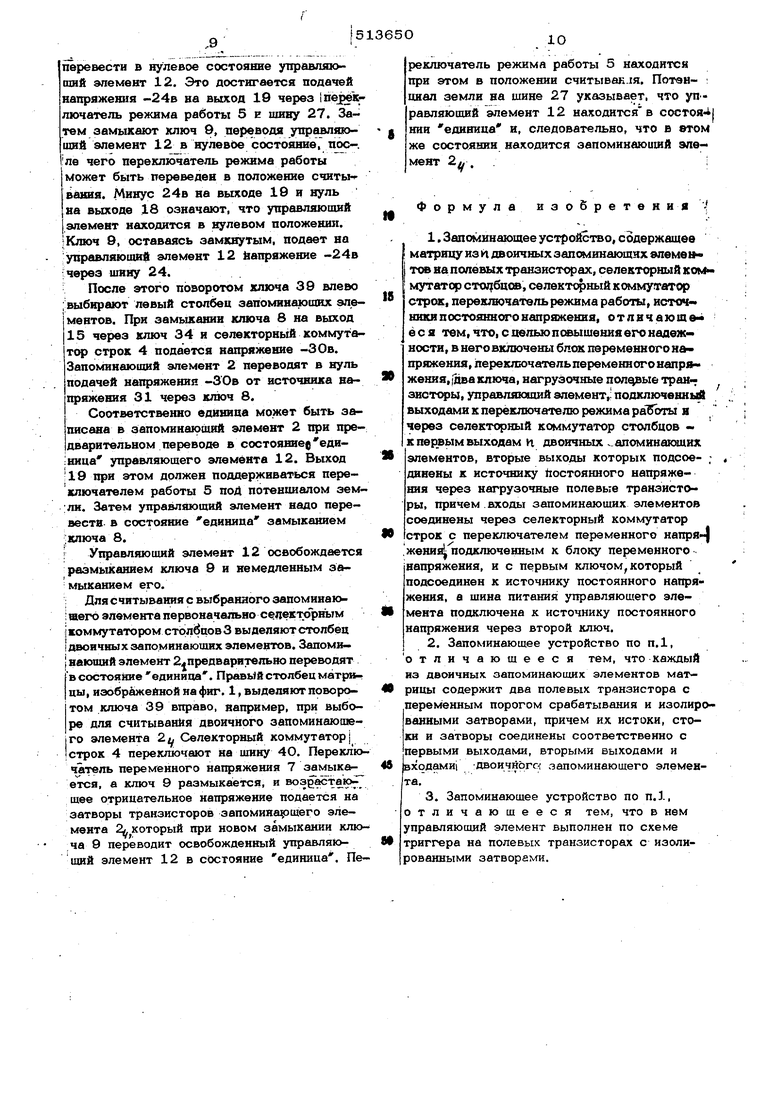

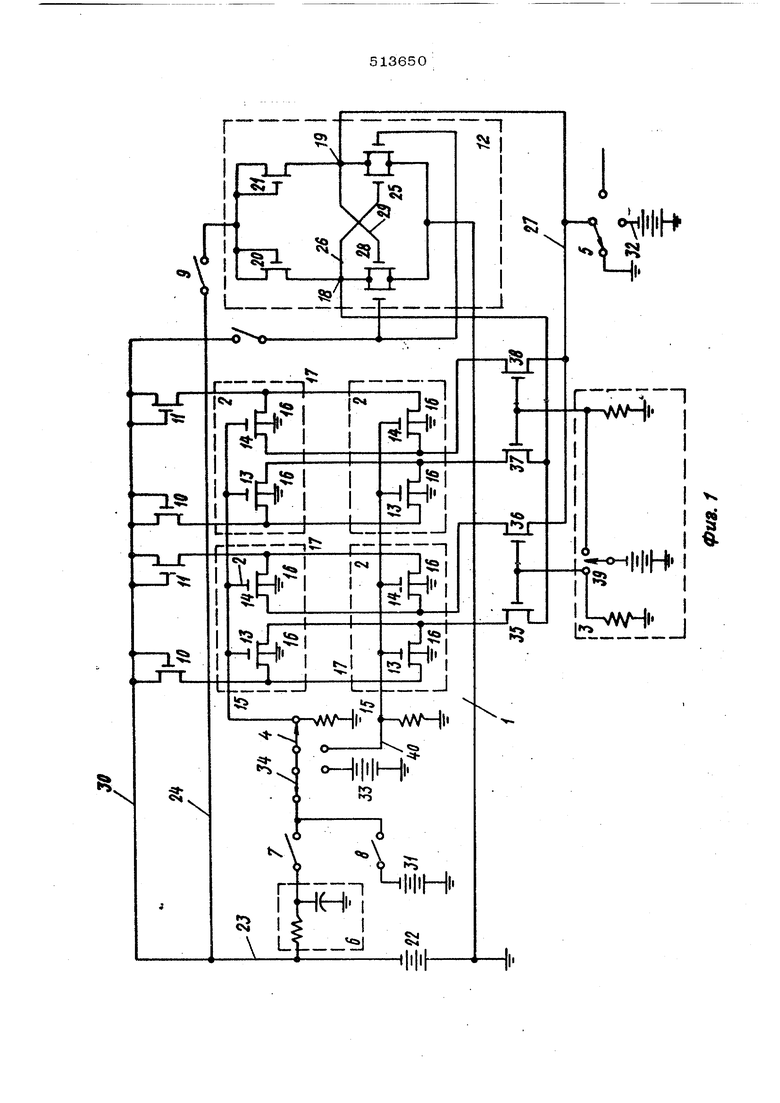

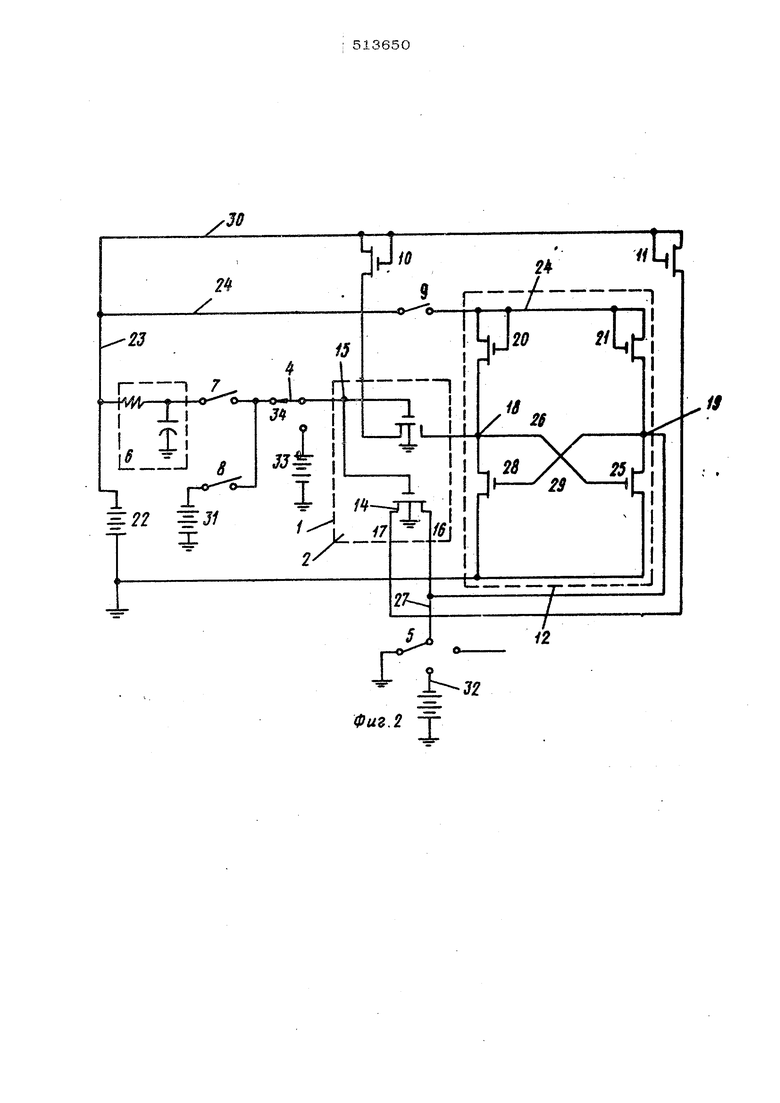

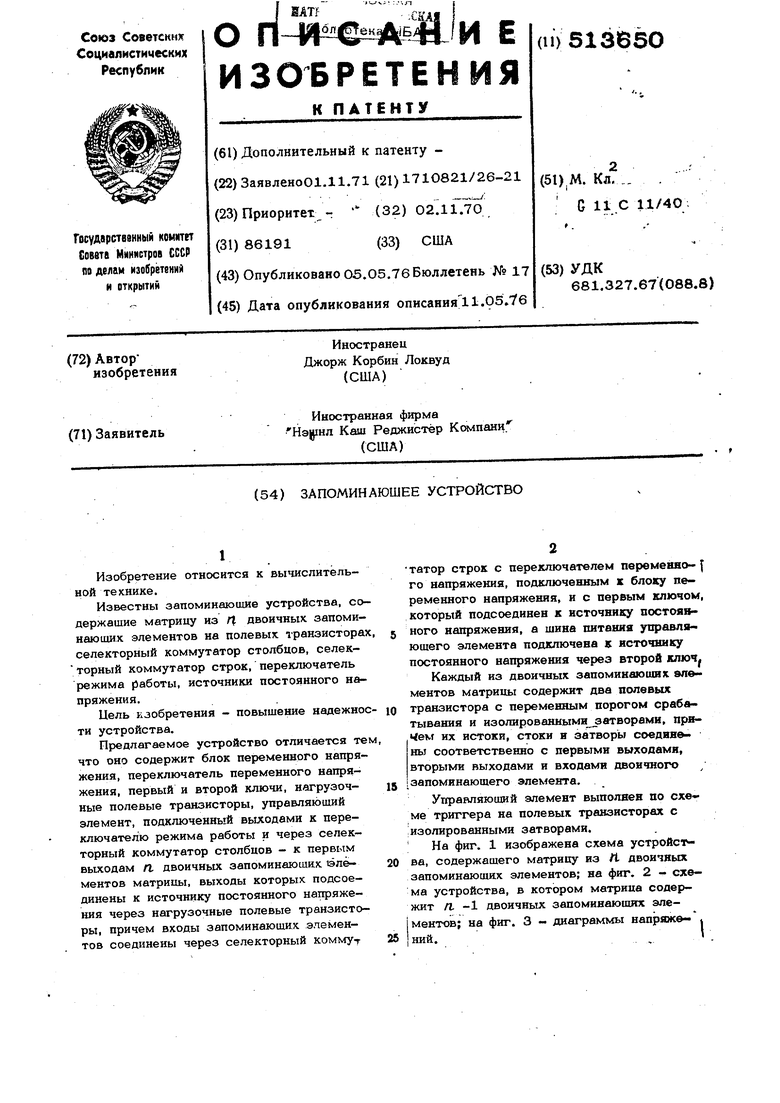

Управляющий элемент выполнен по схеме триггера на полевых транзисторах с : изолированными затворами. На фиг. 1 изображена схема устройства, содержащего матрицу из Л двоичных запоминающих элементов; на фиг. 2 - схема устройства, в котором матрица содержит п, -1 двоичных запоминающих элементов; на фиг. 3 - диаграммы напряже-

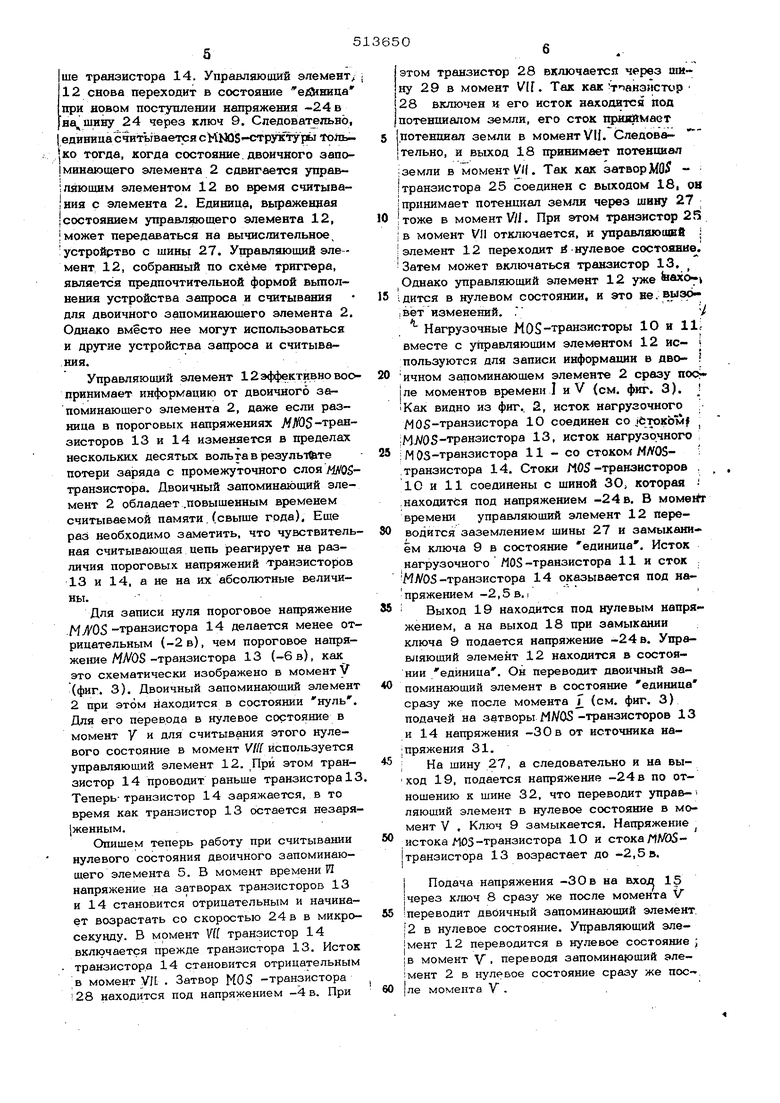

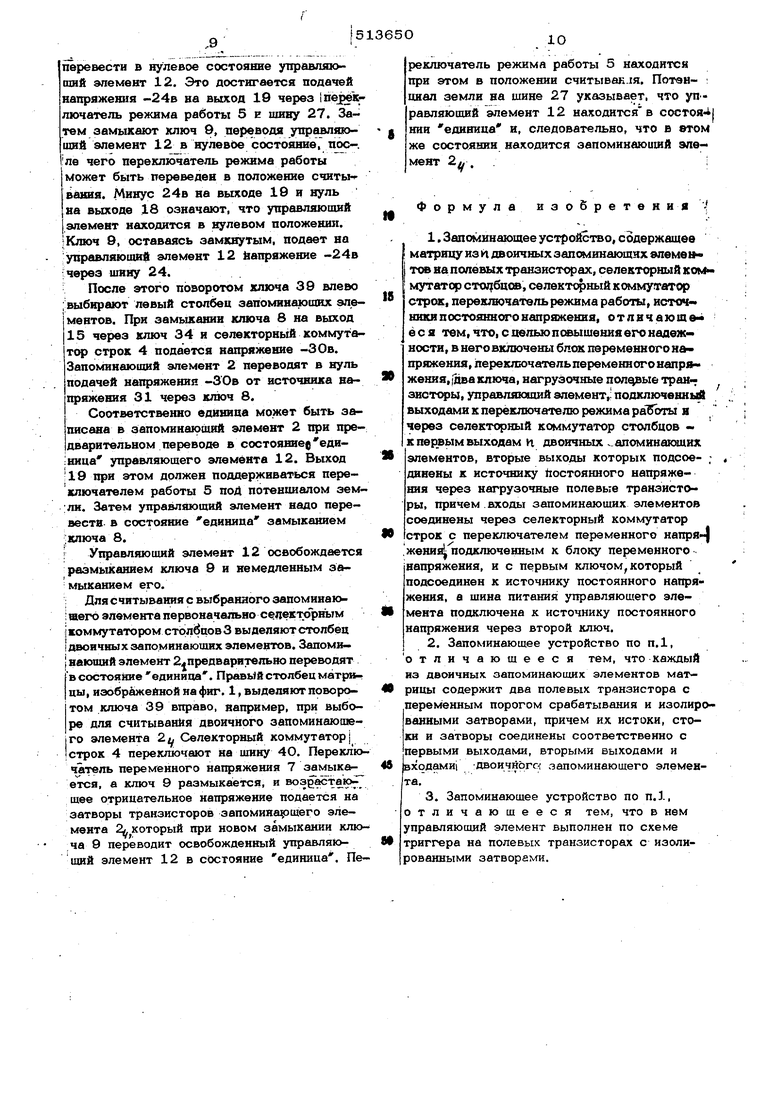

НИИ. Устройство содержит матрицу 1 из двоичных запоминаюашх элементов 2 на поле- вых транзисторах (фиг, 1) .селекторный ком мутатор столбцов 3, селекторный коммутатор строк 4, переключатель режима работы 5, блок переменного напряжения 6, neреключатель переменного напряжения 7, ключи 8 и 9, нагрузочные полевые {МО ) транзисторы 10, 11, управляющий элемен 12. Двоичный запоминающий элемент 2 со держит полевые транзисторы 13 и 14 с пе ременным порогом срабатывания, например транзисторы с - проводимостью структур металл-нитрид кремния-двуокись кремния-кремнийу которых затворы подклкь. чены ко входам 15, истоки - к первым вы ходам 16, а стоки - ко вторым выходам 17 двоичного запоминающего элемента, при чем первые выходы 16 соединены с выход ми 18 и 19 управлякхцего элемента 12. Постепенно возрастающее отрицательное напряжение, подаваемое блоком пере(менного напряжения 6, включает тот из транзисторов 13, 14, отрицательное пороговое напряжение которого меньше. Стоки и затворы транзисторов 2О и 21 нагрузки управляющего элемента 12, имеющих МОS-структуру, соединены с источником питания 22 (-24 в) через шины 23 и 24. Если пороговое напряжение транзистора 13 ниже порогового напряжения гранзио тора 14 (например минус 2 и минус 6 соответственно), стабильный двоичный запоминающий элемент 2 находится в состоянии, при котором между затворами и источником транзистора 13 имеется напряжение -2в благодаря тому, что на изоляциоыном слое между нитридом кремния и окисью кремния запасено много электронов. /ЧУ1/ 05транзистор 14 не проводит электроны от стока к истоку, пока между его .затвором и истоком не приложится напряжение - 6 в, поскольку до этого на его изоляхшонном слое между нитридом ,кремния и окисью кремния запасено мало электронов. Подложки А/Л 05-транзисторов 13и 14 заземлены. Электроны, удерживаемые в транзисторе 13, воздействуют на находящийся под ним кремниевый полупроводниковый материал, способствуя образованию в нем области р-проводимости между областью истока р-типа и областью стока. Каждый из / vVOS-транзисторов 13 и 14имеет слой окиси кремния толщиной примерно в 30 ангстрем и слой нитрида кремния толщиной около 1000 ангстрем, так что отрицательные заряды могут пост пать в слой между двуокисью кремния и нитридом кремния из нижней кремниевой подложки Jt-THna. Отрицательный заряд в слое между двуокисью кремния и нитридом кремния уменьшает отрицательное пороговое напряжение, с которого транзис- тор может накапливать (запоминать) заряды. Вместо транзисторов 13 и 1.4 t f/OSструктуры можно использовать транзисторы Af Л OS -структуры. ТранзистЬр .//j Sструктуры имеет металлический электрод . затвора, толстый изолирующий слой окиси алюминия, тонкий слой окиси кремния и кремниевую подложку. Заряд, накапливаемый в слое между окисью кремния, умень шает отрицательный порог срабатывания транзистора. Окись алюминия может быть заменена другим изолирующим материалом, однако в любом случае должны использоваться стабильные полевые транзисторы с переменным порогом срабатывания. Временная диаграмма работы двоично запоминающего элемента 2, изображенного на фиг. 2, показана на фиг. 3. Для считывания состояния элемента 2 замыкают переключатель переменного напряжения 7. При этом, как показано Б точке И на фиг. 3, напряжение на входе 15 (цифровые обозначения соответствуют позициям на фиг. 1 и 2) становится отрицательным и заменяется со скоростью 24 в в микросекунду. Напряжение на затворе Mi/0 -транзистора 13 достигает - 2Б в момент времени ГИ. Транзистор 13 начинает проводитв и на его истоке появляется отрицательное напряжение. Транзистор 14 не проводит, пока напряжение на входе 15 не достигнег -6 в. Однако, когда напряжение на затворе jyVbS-Tpanзистора 14 достигает -6 в сразу после момента времени Ш, исток транзистора 14, не становится отрицательным, так как выход 19 управляющего элемента 12 поддержи.вается под потенциалом земли, а Н05-транзистор 25 включается через шину 26, когда становится проводящим J4J r05-транзистор 13. Исток и сток MOS-транзистора 25 находится под потенциалом земли. ЭлектрОд затвора этого транзистора находится под потенциалом -4 в. В момент времени Ш напряжение -2 в подается на затвор КК05 -транзистора 13, который начинает проводить электроны от своего стока к выходу 18 управляющего элемента 12, который находится в состоянии, условно именуемом первым, когда отрицательное напряжение появляется на его выходе 18 раньще,чем на выходе 19, Отрицательное напряжение появляется на выходе 18 раньше, чем на выходе 19, так (как /1//05-транзистор 13 включается рань-1

ше транзистора 14. Управляюцшй элемент

12снова переходит в состояние e/UiHHua при новом поступлении напряжения -2 4 в 24 через ключ 9. Следоват впьно,

(единица считывается сМЫОЗ-структуры топь|ко тогда, когда состояние.двоичного запо1минающего элемента 2 сдвигается управ.ляющим элементом 12 во юмя считыва нин с элемента 2. Единица, вьфаженная состоянием управляющего элемента 12, I может передаваться на вычислительное устройртво с шины 27. Управляющий элемент 12, собранный по схеме триггера, является предпочтительной формой вьгаолнения устройства запроса и считывания для двоичного запоминающего элемента 2. Однако вместо нее могут использоваться и другие устройства запроса и считывания.

Управляющий элемент 12 эффективно воопринимает информацию от двоичного запоминающего элемента 2, даже если разница в пороговых напряжениях Ж)5-транзисторов 13 и 14 изменяется в пределах нескольких десятых во ль та в результате потери заряда с промежуточного слоя AWOSтранзистора. Двоичный запоминающий элемент 2 обладает .повышенным временем считываемой памяти. (свыше года). Еще раз необходимо заметить, что чувствительная считывающая цепь реагирует на различия пороговых напряжений транзисторов

13и 14, а не на их абсолютные величины.

Для записи нуля пороговое напряжение .MJVOS -транзистора 14 делается менее отрицательным (-2 в), чем пороговое напря- же1ше MM)S-транзистора 13 (-6 в), как это схематически изображено в момент у (фиг. 3). Двоичный запоминающий элемент 2 при этом находится в состоянии нуль. Для его перевода в нулевое состояние в момент У и для считывания этого нулевого состояние в момент Vlf используется управляющий элемент 12. При этом транзистор 14 проводит раньше транзистора 13 Теперь-транзистор 14 заряжается, в то время как транзистор 13 остается незаря1женным.

Опишем теперь работу при считывании нулевого состояния двоичного запоминающего элемента 5. В момент времени И напряжение на затворах транзисторов 13 и 14 становится отрицательным и начинает возрастать со скоростью 24 в в микросекунду. В момент Vff транзистор 14 включается прежде транзистора 13. Исток транзистора 14 становится отрицательным в момент ул . Затвор HOS -транзистора 28 находится под напряжением -4 в. При

этом транзистор 28 включается через шину 29 в момент . Так как тпанзистсф 28 включен и его исток находится под потенциалом земли, его сток пршсймаст потенциал земли в момент VII. Следовав тельно, и выход 18 принимает потенциал :земли в момент W(. Так как затворМО транзистора 25 соединен с выходом 18, он I принимает потенциал земля через шнну 27 ;тоже в момент W. При этом транзистор 25 i в момент Vn отключается, и управляющий j I элемент 12 переходит и нулевое состояние. Затем может включаться транзистор 13. Однако управляющий элемент 12 уже Ьахо- Удится в нулевом состоянии, и это не. выэр|Вёт изменений. .

Нагрузочные MOS-транзисторы 10 и 11;вместе с управляющим элементом 12 ис- i пользуются для записи информации в дво- I ичном запоминающем элементе 2 сразу пос ле моментов времени иУ (см. фиг. 3). Как видно из фиг.. 2, исток нагрузочного МOS-транзистора 10 соединен со juTOKOMf iMWOS-транзистора 13, исток нагрузочного i М OS-транзистора 11 - со стоком M/VOS- транзистора 14. Стоки MOS-транзисторов , 10 и 11 соединены с шиной 30, которая ; ,находится под напряжением -24 в. В момейт времени управляющий элемент 12 переводится заземлением шины 27 н замыканием ключа 9 в состояние единица. Исток нагрузочного MOS -транзистора 11 и сток : M S-транзистора 14 оказывается под на пряжением -2,5 в..

Выход 19 находится под нулевым напряжением, а на выход 18 при замыкании ключа 9 подается напряжение -24 в. Управляющий элемент 12 находится в состоянии единица. Он перюводит двоичный запоминающий элемент в состояние единица сразу же после момента Т (см. фиг. 3) подачей на затворы MWOS-транзисторов 13 и 14 напряжения -30 в от источника напряжения 31.

На шину 27, а следовательно и на выход 19, подается напряжение -24 в по отношению к шине 32, что переводит управ- ляющий элемент в нулевое состояние в момент V . Ключ 9 замыкается. Напряжение истока МОЗ-транзистора 10 и стока/1МЭ5j транзистора 13 возрастает до -2,5 в.

Подача напряжения -30 в на вход 15 через ключ 8 сразу же после момента V переводит двоичный запоминающий элемент. 2 в нулевое состояние. Управляющий элемент 12 переводится в нулевое состояние ; в момент Г , переводя запомина|оший элемент 2 в нулевое состояние сразу же пос- ле момента V . ; Состояние единица, в котором находится запоминающий элемент 2, изображе ный на фиг. 2, в момент времени Jl . жет быть стерто в момент |У подачей нап(1яжеш1я. 30 в от источника н 1фяжения 33 на затворы ЛЛ/ОЗ-транзисторов 13 и , 14 через ключ 34. Подложки обоих тран-; .зисторов заземлены. Эл троны в кремниевой подложке под слоем нитрида кремния в транзисторе 14 перемещаются в момент : и/ X. слою между нитридом кремния и окись кремния. Пороговое напряжение транзистора 14 изменяется в момент IV от -6в до -2в; Пороговое напряжение транзистора 13 в мо мент/достается на уровне-2в, так как в нем в изолирующем слое между нитридом кремния и окисью кремния уже имелся значительный избыток электронов. Таким образом, изолирующие слои между нитридом кремния и окисью кремния в транзисторах 13 и 14 в момент времени IV оказываются заряженными отрицательно, что приводит к стиранию информации в запоминающем элементе 2. Внутреннее сопротивление /JOS- ров 10 и 11 порядка 100 000 ом, в ,1° время как внутреннее сопротивление/J USТранзисторов 13 и 14 около 5 000 ом. Следовательно, когда транзистор 13 или 14 проводит, потенциал его стока очень бл зок к потешшалу земли, а его исток находится под потенциалом земли. Тем самым между затвором и истоком и стоком транзистора 14 сразу же после момента t обес пёчивается разность потенциалов почти в 30 в. Пороговое напряжение транзистора 14 становится более отрицательным сразу же после момента f так как на его исток в этот момент поступает потенциал земли. Когда исток транзистора 13 поддержи- вается в момент под нулевым напряжением а на затвор сразу же после момента подается напряжение -ЗОв, ток от транзисто ра 13 течет через транзистор 10. На CTOK транзистора 13 подается в это время напряжение -2,5в тогда как сток транзистор 10 поддерживается под напряжением -24в Электроны отводятся от слоя между нитридом кремния и окисью кремния транзистора 13 сразу же после момента У изменяя его пороговое напряжение с -2в/до -6в. Таким образом, при считывании, в момеит соединенные затворы транзисторов ГЗ и 14 со входа, 15 подается возрастаю шее отрицательное запирающее напряжение и транзистор 14 включается при -2в, а транзистор 13 не включается,, пока напряжение на электроде его затвора не достигнет -6в относительно электрода истока. На фиг. 1 изображена матрица 1 на чеырех лвричгных апоминающих элементов f атворы трайэнсторов 13 и 14 соединены о входом 15, который через селекторный оммутатор строк 4 подключен к блоку пееменного нгифяжения 6. Истоки траизнсто-) ров через выход 16 соедян ены со столбцом | селекторных Н0$ -транзясторов 35 н 36 или 37 и 38,.ynpu8Mett4ibix ключом 39, селект(фного коммутатора столбцов 3, выходы которого подключевы к выходам 18 и 19 управляющего элемента 12. Таким образом обеспечивается считывание нли запись на любом запоминающем элементе. Стоки тран3исторов 13 и 14 запомиКаюшкх элеменов 2 соеданены через 17 с нагрузочными транзисторами Юн 11. которые ; в свою очередь, сое0днены с источником напряжения 22. Столбец матрицы выделякуг транзисторы 35 -38. Управдаюший элемент 12 используется для считывания информации с лкбого запомннаюоюго элемента матрицы, а также для записи новой информации в любой запоминающий элемент. i Затворы селекторных, транзисторов 3538 соединены с ключом 39. который обеспечивает выбор л1Ьбо1Ч элемента мат|жаы.Т|.. КИМ образом, зшшсь Нли считывание могут быть получены на лкубрм запомНнающем элементе с помощью средств селекции столбluoB и строк. Последовательность запоминающих элементов обргазует стабильную запоминающую матрицу. При считывании, управляемом электрически, только в запоминающую матрицу, изображенную иа фиг. 1. могут быть стабильно записаны четыре двоичных единицы информации. Одна единица может быть записана в каждый зшюмииающиЙ элемент. Информация, записанная в любой вь1бранный запоминающий элемент 2. изображенный на фиг. 1, считывается так же. как это было описано для считывания информ ции с элемента 2, изображеннога на фНг. 2. |3апись, считывание и стирание в выбранном запоминающем элементе происходит так же, как это объяснялось при рассмотрении временной диаграммы, изображенной на фиг. 3. Матрица 1 может использоваться в качест ве стабильной запоминающей матрицы с электрическим управлеиием для записи хаотически поступающей ииформации. Как показано на фиг. 1 для считывания информации с любого. запоминающего элемента через управляющий элемент 12 или для записи новой информации в любой запоминающий I элемент через управляющий элемент 12 используется переключатель режима работы 5. Чтобы записать значение нуль в выбран|ный запоминающий элемент, надо сначала

перевести в нулевое состояние управляющий элемент 12. Это достигается подачей напряжения -24в на выход 19 через пе ёключатель режима работы 5 Е шину 27. Затем замыкают ключ 9, переводя управляющий элемент 12 в нулевое состояние, пос-. ле чего переключатель режима работы может быть переведен в положение считы вания. Минус 24в на выходе 19 и нуль на выходе 18 означают, что управляющий элемент находится в нулевом положении. Ключ 9, оставаясь , подает на управляющий элемент 12 Напряжение -24в (через шину 24.

После этого поворотом ключа 39 влево ; выбирают левый столбец запоминающих элементов. При замыкании ключа в на выход 15 через ключ 34 и селекторный коммутатор строк 4 подается напряжение -ЗОв. Запоминающий элемент 2 переводят в нуль подачей напряжения -ЗОв от источника напряжения 31 через ключ 8.

Соответственно единица может быть записана в запоминающий элемент 2 при предварительном переводе в состояние еди ница управляющего элемента 12. Выход 19 при этом должен поддержнваться переключателем работы 5 поД потенциалом зем;лн. Затем управляющий элемент надо перевести в состояние единица замыканием ;ключа 8.

1 Управляющий элемент 12 освобождается размыканием ключа 9 и немедленным за мыканием его.

Для с читывания с выбранного запомииаюиего элемента первоначально c jjeKTopiftjM j коммутатором стрлЙцов 3 выделяют столбец {двоичныхзапоминающих элементов. Заломи- I наюший элемент 2 предварительно переводят всостоя1ше единица. Правь1йстолбецматр цы, изображейной на фиг. 1, выделяют поворотом ключа 39 вправо, например, при выборе для считывания двоичного запоминающего элемента 2 Селекторный коммутатор I строк 4 переключают Иа ишну 40. Переключатель переменного напряжения 7 замыкается, а ключ 9 размыкается, и возраста ю-Г шее отрицательное напряжение подается на затворы транзисторов запоМина9)шего элемента который при новом замыкании ключа 9 переводит освобожденный управляющий элемент 12 в состояние единица. Переключатель режима работы 5 находится при этом в положении считывакля. Потен- : циал земли на шине 27 указывает, что уП равляющий элемент 12 находится в состоя« | НИИ единица и, следовательно, что в этом же состоянии находится запоминаюишй элемент 2/, .;

и 3 о б

Формула

р е т е н и я

1.Запоминающее ус1 ойсгоо, содержащее матрицу из п двоичных запсминающнх элеме тов на полевых транзисторах, селекторный коммутатор CTOJ76uQB, селект фный коммутатор строк, перекшочатель режима работы, источннкн постоянного напряжения, oтлнчaюшei ее я тем, что, с цельюпсшышення его надежности, в него включены блок переменного на« пряження,перекяючательперемеш1огонапрв ження, {два ключа, нагрузочные полные тран-; знсторы, управляющий элемент,; подключенньА выходами к переключателю режима работы я через селективный коммутатор столбцов к первым выходам к двоичных ..апомннакшнх элементов, вторые выходы которых подсоедннены к источнику постоянного напряжения через нагрузочные полевые транзисторы, причем входы запоминающих элементов соедннены через селекторный коммутатор строк с переключателем переменного напря ,жени подключенным к блоку переменного напряжения, и с первым ключом, который подсоединен к источнику постоянного напряжения, а щина питания управляющего элемента подключена к источнику постоянного напряжения через второй ключ.

2.Запоминающее устройство по п.1, отличающееся тем, что каждый из двсжчных запоминающих элементов матрицы содержит два полевых транзистора с переменным порогом срабатывания и изолированными затворами, причем их истоки, стоки и затворы соединены соответственно с первыми выходами, вторыми выходами и входами ДВОИЧНОГС1 запоминающего элемента,

3.Запоминающее устройство по п.1, отличающееся тем, что в нем управляющий элемент выполнен по схеме триггера на полевых транзисторах с изолированными затворами. -vwHi Hi|i|Hi 1 -H|i|iH Hч .- L

.1

Фив.2 т

.1

&|5

%

/

„yl

| название | год | авторы | номер документа |

|---|---|---|---|

| Способ управления -канальным накопительным полевым транзистором | 1976 |

|

SU791272A3 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 1991 |

|

RU2060578C1 |

| СЧИТЫВАЮЩАЯ СХЕМА ДЛЯ ФЛЭШ-ПАМЯТИ С МНОГОУРОВНЕВЫМИ ЯЧЕЙКАМИ | 1995 |

|

RU2190260C2 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО, МНОЖЕСТВО ЗАПОМИНАЮЩИХ УСТРОЙСТВ И СПОСОБ ИЗГОТОВЛЕНИЯ ЗАПОМИНАЮЩЕГО УСТРОЙСТВА | 1997 |

|

RU2216821C2 |

| Полупроводниковый преобразователь | 1979 |

|

SU766471A1 |

| Накопитель информации для оптоэлектронного запоминающего устройства | 1981 |

|

SU995125A1 |

| Оперативное запоминающее устройство | 1985 |

|

SU1283854A1 |

| Запоминающее устройство | 1980 |

|

SU903981A1 |

| Динамический элемент памяти | 1978 |

|

SU763966A1 |

| ОБНАРУЖЕНИЕ ЗАРЯДА ИЛИ ЧАСТИЦЫ | 2003 |

|

RU2339973C2 |

la

fei-4

.-..-y

-

ksi

±

J

Авторы

Даты

1976-05-05—Публикация

1971-11-01—Подача