I

Изобретение относится к вычиспитепь ной технике и предназначено ддя создания полупроводниковых постоянных запоминакн ших устройств с электрическим перепрограммированием информации на основе МНОП (металл-нитрид кремния - окисел кремния - полупроводник) запоминающих стуктур.

Известно постоянное запоминакщее устройство с электрической сменой информации, содержащее- матрицу МНОП . ячеек памяти, каждая из которых состоит из запоминающего и разделительного транзисторов, позволяющих использовать одну столбцовую щину общей для двух соседних ячеек, подключая каждую пару ячеек к усилителю считывания таким образом, что одна ячейка является запоминающей, а другая- опорной 1 .

Однако указанное запоминающее устройство вследствие несимметричности схемы имеет пониженную помехоустойчивость и недостаточное время хранения информации.

Наиболее близким по технической сущности к предлагаемому является постоянное запоминающее устройство, в котором каждая столбцовая щина, являющаяся общей для кажоых двух соседних ячеек, содержащих разделительный и запоминающий транзисторы, подключает к ячейкам через соответстсвующие дещифруемые ключевые транзисторы разряды сдвигового регистра С 2 .

to

Недостатком такого устройства является необходимость коммутации при записи и стирании ттформации выссжоволыных сигналов передающими ключевыми транзисторами, что требует соответст

IS венно высоковольтных схем адресных усилителей, регистра, что снижает надежность схемы. Кроме того, недостатком такого запоминакнцего устройства является то, что направление протекания

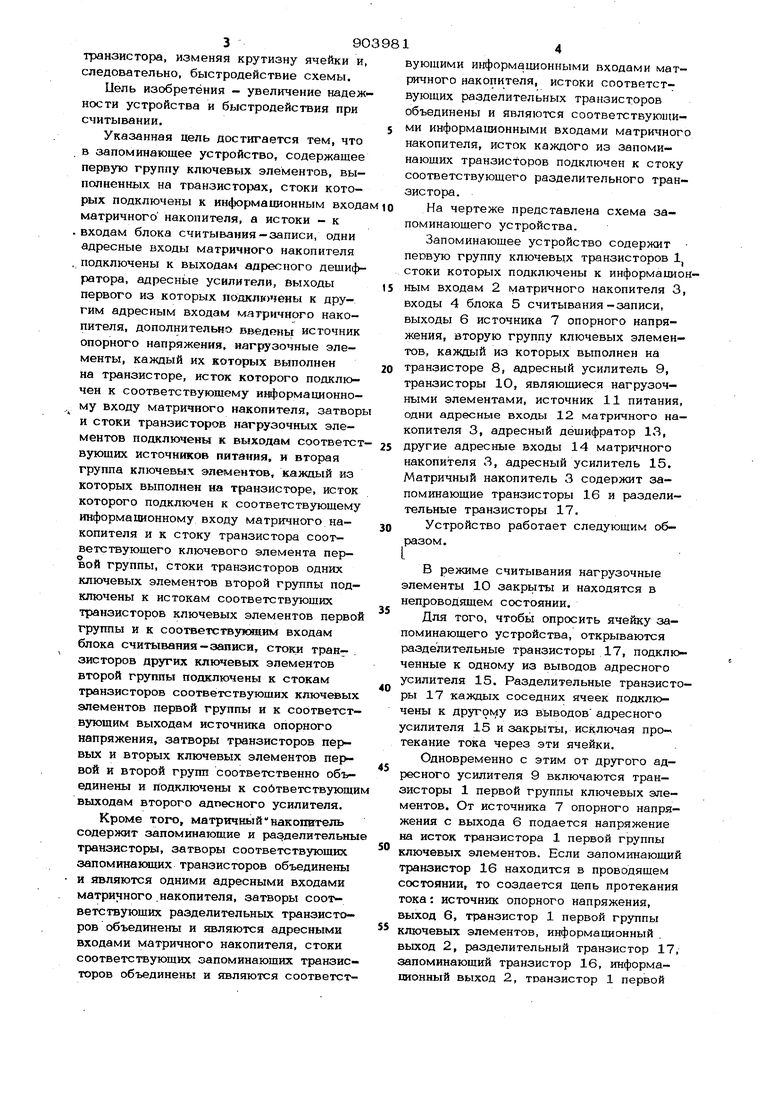

20 тока в двух соседних ячейках противоположное. Это требует включения раздели- тельно1 о транзистора ячейки либо в цепь стока, либо в цепь истока запоминающеготранзистора, изменяя крутизну ячейки и, следовательно, быстродействие схемы. Цель изобретения - увеличение надеж ности устройства и быстродействия при считывании. Указанная цель достигается тем, что в запоминающее устройство, содержащее первую группу ключевых элементов, выполненных на транзисторах, стоки которых подключены к информационным входа матричного накопителя, а истоки - к .входам блока считывания-записи, одни адресные входы матричного накопителя подключены к выходам адресного дешифратора, адресные усилители, выходы первого из которых подключены к другим адресным входам матричного накопителя, дополнительно введены источник опорного напряжения, нагрузочные элементы, каждый их которых выполнен на транзисторе, исток которого подключен к соответствующему информационному входу матричного накопителя, затвор и стоки транзисторов нагрузочных элементов подключены к выходам соответст вуюших источников питания, и вторая группа ключевых элементов, каждый из которых выполнен на транзисторе, исток которого подключен к соответствующему информационному входу матричного накопителя и к стоку транзистора соответствующего ключевого элемента первой группы, стоки транзисторов одних ключевых элементов второй группы подключены к истокам соответствующих транзисторов ключевых элементов перво группы и к соответствуницим входам блока считывания-записи, стоки транзисторов других ключевых элементов второй группы подключены к стокам транзисторов соответствующих ключевых элементов первой группы и к соответствующим выходам источника опорного напряжения, затворы транзисторов первых и вторых ключевых элементов и второй групп соответственно объединены и подключены к собтветствующ выходам второго адпесного усилителя. Кроме того, матричный накопитель содержит запоминающие и разделительны транзисторы, затворы соответствующих запоминающих транзисторов объединены и являются одними адресными входами матричного накопителя, затворы соответствующих разделительных транзисторов объединены и являются адресными входами матричного накопителя, стоки соответствующих запоминающих транзис торов объединены и япвляются соответст вующими информационными входами матричного накопителя, истоки соответствующих разделительных транзисторов объединены и являются соответствуюи1ими информационными входами матричного накопителя, исток каждого из запоминающих транзисторов подключен к стоку соответствующего разделительного транзистора. На чертеже представлена схема запоминающего устройства. Запоминающее устройство содержит первую группу ключевых транзисторов 1 стоки которых подключены к информационным входам 2 матричного накопителя 3, входы 4 блока 5 считывания-записи, выходы 6 источника 7 опорного напряжения, вторую группу ключевых элементов, каждый из которых выполнен на транзисторе 8, адресный усилитель 9, транзисторы 1О, являющиеся нагрузочными элементами, источник 11 питания, одни адресные входы 12 матричного накопителя 3, адресный дёщифратор 13, другие адресные входы 14 матричного накопителя 3, адресный усилитель 15. Матричный накопитель 3 содержит запоминающие транзисторы 16 и разделительные транзисторы 17. Устройство работает следующим образом. в режиме считывания нагрузочные элементы Ю закрыты и находятся в непроводящем состоянии. Для того, чтобь опросить ячейку запоминающего устройства, открываются разделительные транзисторы 17, подклк ченные к одному из выводов адресного усилителя 15. Разделительные транзисторы 17 каждых соседних ячеек подключены к другому из выводов адресного усилителя 15 и закрыты, исключая протекание тока через эти ячейки. Одновременно с этим от другого адресного усилителя 9 включаются транзисторы 1 первой группы ключевых элементов. От источника 7 опорного напряжения с выхода 6 подается напряжение на исток транзистора 1 первой группы ключевых элементов. Если запоминающий транзистор 16 находится в проводящем состоянии, то создается цепь протекания тока: источник опорного напряжения, выход 6, транзистор 1 первой группы ключевых элементов, информационный . выход 2, разделительный транзистор 17, запоминающий транзистор 16, информационный выход 2, транзистор 1 первой группы ключевых элементов, вход 4, блок 5 считывания-записи. Соседняя ячейка опрашивается, когда потенциалы на одном из выводов адресных усилителей 9 и 15 изменяются на противоположные. В этом случае открываются разделительные транзисторы. 17 и транзисторы 8 второй группы ключевы элементов. Опрос ячейки происходит так, как и в первом случае, только в цепи протекания тока вместо транзисторов 1 перв группы ключевых элементов участвуют транзисторы 8 второй группы ключевых элементов, г в режиме записи закрыты все разделительные транзисторы 17 запоминаю щего устройства. Через нагрузочные элементы 10, затворы и стоки кото|эых подключены к высоковольтному источнику 11 питания (порядка 30-35 В), на информационные шины 2 матрицы 3 подается напряжение блокировки записи. Информационные шины 2 и соответственно стоки запоминающих транзисторов 16 подключаются через транзисторы первой или второй группы ключевых элементов к соответствующему входу 4 блока 5 считывания-записи. Если на входе 4 схемы считывания-записи имее ся низкий потенциал, ПРОИСХОДИТ запись информации в ячейку матричного накопителя. Если вход 4 схемы считываниязаписи является плавающим, то информационная шина 2 имеет потенциал блокировки записи, и записи информации в ячейку не произойдет. В предлагаемом устройстве исключаются высоковольтные цепи адресного усилителя и блока считывания-записи, что повышает надежность и быстродействие устройства. Кроме того, устройство имеет однонаправленное протекание тока считывани через ячейку памяти от нечетной разряд НОЙ шины к четной, что также повышает надежность его работы. Формула изобретения Запоминающее устройство, содержащее первую группу ключевых элементов, выполненных на транзисторах, стоки которых подключены к информационным входам матричного накопителя, а истоНИ - к входам блока считывания-записи, одни адресные входы матричного накопителя подключены к выходам адресного дешифратора, адресные усилители, выходы первого из которых подключены к другим адресным входам матричного накопителя, отличающееся тем, что, с целью повьпиения надежности и быстродействия устройства, оно содержит источник опорного напряжения, нагрузочные элементы, каждый из которых выполнен на транзисторе, исток которого подклк чен к соответствующему информационному входу матричного накопителя, затворы и стоки транзисторов нагрузочных элементов подключены к выходам cooTBeTCiw вующих источников питания, и вторую группу ключевых элементов, каждый из которых выполнен на транзисторе, исток которого подключен к соответствующему информационному входу матричного накопителя и к стоку транзистора соответствуюшего ключевого элемента первой группы, стоки транзисторов одних ключевых элементов второй группы подключены к истокам транзисторов соответствующих ключевых элементов первой группы и к соответствующим входам блока считывания-записи, стоки транзисторов других ключевых элементов второй группы подключены к стокам транзисторов соответствующих ключевых элементов первой группы и к соответствующим выходам источника опорного напряжения, затворы транзисторов первых и вторых ключевых элементов первой и второй групп соответственно объединены и подключены к соответствующим выходам второго адресного усилителя., 2. Запоминающее устройство по п. 1, тличающееся тем, что, атричный накопитель содержит запомиающие и разделительные транзисторы, атворы соответствующих запоминающих ранзисторов объединены и являются дними адресными входами матричного акопителя, затворы соответствующих азделительных транзисторов объединены «шляются адресными входами матричого накопителя, стоки соответствующих апоминающих транзисторов объединены являются соответствующими информаионными входами матричного накопителя, стоки соответствующих разделительных ранзисторов объединены и являются оответствующими информационными ходами матричного накопителя, исток а ждого из запоминающих транзисторов

79039818

подключен к стоку соответствующего1. Патент США № 4090257,

разделительного транзистора,кп. G 11 С 11/40, 1978.

Источники информаПИИ,2. Патент США № 4 103344,

принятые во внимание при экспертизекл. G 11 С 11/40, 1978 (прототип),

| название | год | авторы | номер документа |

|---|---|---|---|

| Усилитель считывания на моп-транзисторах /его варианты/ | 1980 |

|

SU883968A1 |

| Адресный дешифратор для полупроводникового постоянного запоминающего устройства | 1980 |

|

SU960949A1 |

| УСИЛИТЕЛЬ ЗАПИСИ-СЧИТЫВАНИЯ ДЛЯ ЗАПОМИНАЮЩИХ УСТРОЙСТВ | 1987 |

|

SU1612801A1 |

| Оперативное запоминающее устройство | 1985 |

|

SU1283854A1 |

| Ячейка фоточувствительного матричного запоминающего устройства | 1989 |

|

SU1709392A1 |

| Ассоциативное запоминающее устройство | 1990 |

|

SU1795521A1 |

| Матричный накопитель для постоянного запоминающего устройства | 1990 |

|

SU1756939A1 |

| Постоянное запоминающее устройство | 1986 |

|

SU1388950A1 |

| Оперативное запоминающее устройство | 1987 |

|

SU1429167A1 |

| Авторегулируемый формирователь напряжения записи для электрически программируемых постоянных запоминающих устройств на КМОП-транзисторах | 1988 |

|

SU1631606A1 |

Ж

И

1

f6f7r

Ш1Ъ

11

i

wnj

1бПг

1617г

13

№t7i

гт

Авторы

Даты

1982-02-07—Публикация

1980-03-07—Подача