11283854

Изобретение относится к вычисли- ельной технике, в частности к устойствам памяти.

Целью изобретения является повыение быстродействия запоминающего стройства.

ра

ря ди но ра че бы По фо ва пи са к пр за ва со па пр на че и ла ра 4. и ди во ва 3 Да тр ты вх

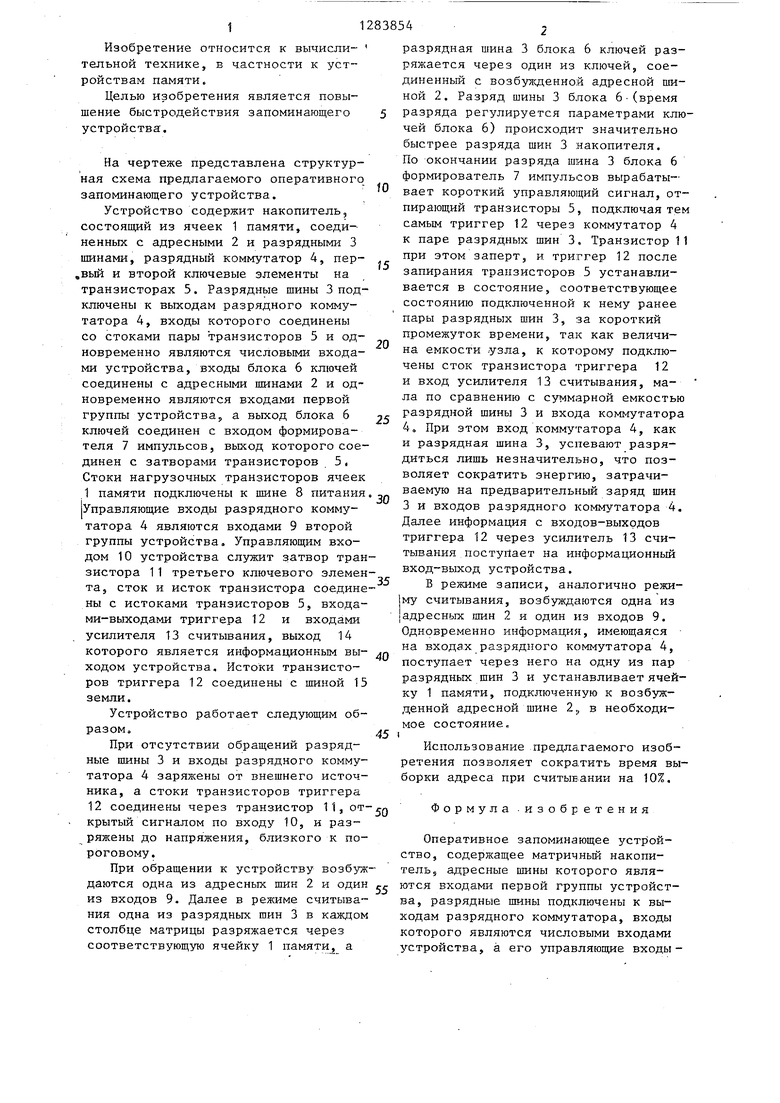

На чертеже представлена структурная схема предлагаемого оперативного запоминающего устройства.

Устройство содержит накопитель, состоящий из ячеек 1 памяти, соединенных с адресными 2 и разрядными 3 шинами, разрядный коммутатор 4, перf5

20

25

30

ьш и второй ключевые элементы на ранзисторах 5. Разрядные шины 3 подключены к выходам разрядного коммутатора 4, входы которого соединены со стоками пары транзисторов 5 и одновременно являются числовыми входами устройства, входы блока 6 ключей соединены с адресными шинами 2 и одновременно являются входами первой группы устройства, а выход блока 6 ключей соединен с входом формирователя 7 импульсов, выход которого соединен с затворами транзисторов 5. Стоки нагрузочных транзисторов ячеек 1 памяти подключены к шине 8 питания. Управляющие входы разрядного коммутатора 4 являются входами 9 второй группы устройства. Управляющим входом 10 устройства служит затвор транзистора 11 третьего ключевого элемента, сток и исток транзистора соединены с истоками транзисторов 5, входами-выходами триггера 12 и входами усилителя 13 считывания, выход 14 которого является информационным выходом устройства. Истоки транзисторов триггера 12 соединены с шиной 15 земли.

Устройство работает следующим образом.

При отсутствии обращений разрядные шины 3 и входы разрядного коммутатора 4 заряжены от внешнего источника, а стоки транзисторов триггера 12 соединены через транзистор 11, OT-.JQ крытый сигналом по входу 10, и разряжены до напряжения, близкого к пороговому.

При обращении к устройству возбуждаются одна из адресных шин 2 и один из входов 9. Далее в режиме считывания одна из разрядных шин 3 в каждом столбце матрицы разряжается через соответствующую ячейку 1

35

40

45

55

54

разрядная шина 3

2 блока

ключей раз

5

0

5

0

Q

5

0

5 I

5

ряжается через один из ключей, соединенный с возбужденной адресной шиной 2. Разряд шины 3 блока 6(время разряда регулируется параметрами ключей блока 6) происходит значительно быстрее разряда шин 3 накопителя. По окончании разряда шина 3 блока 6 формирователь 7 импульсов вырабатывает короткий управляющий сигнал, отпирающий транзисторы 5, подключая тем самым триггер 12 через коммутатор 4 к паре разрядных 3, Транзистор 11 при этом заперт, и триггер 12 после запирания транзисторов 5 устанавливается в состояние, соответствующее состоянию подключенной к нему ранее пары разрядных шин 3, за короткий промежуток времени, так как величина емкости .узла, к которому подключены сток транзистора триггера 12 и вход усилителя 13 считывания, ма- ла по сравнению с суммарной емкостью разрядной шины 3 и входа коммутатора 4. При этом вход коммутатора 4, как и разрядная шина 3, успевают разрядиться лишь незначительно, что позволяет сократить энергию, затрачиваемую на предварительный заряд шин 3 и входов разрядного коммутатора 4. Далее информация с входов-выходов триггера 12 через усилитель 13 считывания поступает на информационный вход-выход устройства.

В режиме записи, ангшогично режиму считывания, возбуждаются одна из адресных глин 2 и один из входов 9. Одновременно информация, имеющаяся на входах разрядного коммутатора 4, поступает через него на одну из пар разрядных шин 3 и устанавливает ячейку 1 памяти, подключенную к возбужденной адресной шине 2,, в необходимое состояние.

Использование предлагаемого изобретения позволяет сократить время выборки адреса при считынании на 10%.

Формула -изобретения

Оперативное запоминающее устройство, содержащее матричный накопитель, адресные шины которого являются входами первой группы устройства, разрядные шины подключены к выходам разрядного коммутатора, входы которого являются числовыми входами устройства, а его управляющие входывходами второй группы устройства, триггер, формирователь импульсов, вход которого соединен с выходом блока ключей, а входы блока ключей соединены с адресными шинами накопителя, отличающееся тем, что, с целью повышения быстродействия устройства, в него введены ключевые элементы на транзисторах, причем стоки транзисторов первого и второго ключевых элементов подключены к входам

разрядного коммутатора, затворы - к выходу формирователя импульсов, а истоки транзисторов первого и вто рого ключевых элементов соединены с входами-выходами триггера, затвор транзистора третьего ключевого элемента является управляющим входом устройства, а сток и исток соединены с истоками транзисторов первого и второго ключевых элементов соответственно.

rTj. -i.

м

М- 75 t/4t

Составитель С.Королев Редактор Ю.Середа Техред А.Кравчук Корректор М. Максимишинец

Зайаз 450/52 Тираж 589Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

.Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4.

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство | 1985 |

|

SU1269209A1 |

| Оперативное запоминающее устройство | 1987 |

|

SU1429167A1 |

| Постоянное запоминающее устройство | 1986 |

|

SU1388950A1 |

| Матрица постоянного запоминающего устройства | 1983 |

|

SU1348908A1 |

| Полупроводниковое запоминающее устройство | 1981 |

|

SU987679A1 |

| Оперативное запоминающее устройство на мдп-транзисторах | 1974 |

|

SU744726A1 |

| Полупроводниковое запоминающее устройство | 1984 |

|

SU1238157A1 |

| Ассоциативное запоминающее устройство | 1990 |

|

SU1795521A1 |

| Постоянное запоминающее устройство | 1988 |

|

SU1594603A1 |

| Запоминающее устройство | 1985 |

|

SU1317481A1 |

Изобретение относится к вычислительной технике. Целью изобретения является повьшение быстродействия запоминающего устройства. Устройство содержит накопитель информации на МДП-транзисторах, разрядный коммутатор, блок ключей, формирователь импульсов, ключевые элементы на транзисторах, триггер и усилитель считывания. Повышение быстродействия достигается за счет того, что при появлении информации на входах- выходах триггера ключевые транзисторы отключают его от разрядных шин. В результате триггер переключаясь в необходимое состояние, перезаряжает лишь небольшие емкости стоков ключевых транзисторов. 1 ил. tc 00 со 00 ел 4

Авторы

Даты

1987-01-15—Публикация

1985-06-05—Подача