Изобретение относится к цифровым вычислительным системам.

Известен мультиплексный канал с косвенной адресацией памяти, содержащий блок сопряжения с центральным процессором, первый вход которого подключен к перво.му входу канала, а первый выход соединен с первым выходом канала, блок сопряжения с центральной оперативной памятью, первый вход которого подключен ко второму входу канала, а первые два выхода соединены соответственно со вторым и третьим выходами канала, блок сопряжения с внешними устройствами, первые вход и выход которого соединены соответственно с третьим .входом и четвертым выходом канала, блок основной памяти, блок адресной памяти, первый выход которого соединен с первым входом блока основной памяти, регистр подканала, два входа которого подключены соответственно ко второму выходу блока сопряжения с центральным процессором и второму выходу блока сопряжения с внеш.ними устройствами, а выход соединен со вторыми входами блоков сопряжения с центральным процеосорОМ и внешними устройствами и с первым входом блока адресной памяти, регистр управления, два входа которого подключены соответственно к выходу блока основной памяти и третьему выходу блока сопряжения с центральной оперативной памятью, регистр

2

информации, три входа которого подключены соответственно к выходу блока основной памяти, второму выходу блока сопряжения с виешними устройствами и третьему выходу

блока сопряжения с центральной оперативной памятью, первьп выход соединен со входом блока сопряжения с внешним устройствами, а второй выход сое.динеп со вторы.ми входами блока основной памяти и блока сопряжения с центральной оперативной памятью, блок модификации, вход Которого подключен к выходу регистра управления, а выход соединен с третьим входом блока сопряжения с нейтральной оперативной памятью и

вторым входом блока основной памяти, преобразователь кода адреса, выход которого соединен со вторым входом блока адресной памяти, первый регистр адреса, первый выход которого соединен со вторым и третьим входами блока адресной памяти и входом преобразователя кода адреса, а второй выход соединен с первым входом блока основной иамяти. блок определения адреса, выход которого соединен со входом первого регистра адреса, а

первые два входа подключены соответственно к первому и второму выходам блока адреспой памяти.

Целью изобретения является повышепие надежности работы мультиплексного канала. В

описываемом канале это достигается тем, что

в нем дополнительно применены второй регистр адреса, генератор чисел и блок контроля ячеек золы основной памяти мультиплексного канала. Вход второго регистра адреса подключен ко второму выходу первого регистра адреса, а выход соединен с первым входом блока основной памяти. Два входа блока контроля подключены соответственно к выходам генератора чисел и блока основной намяти, а два выхода соединены соответственно с третьим входом блока определения адреса и вторым входом блока основной памяти.

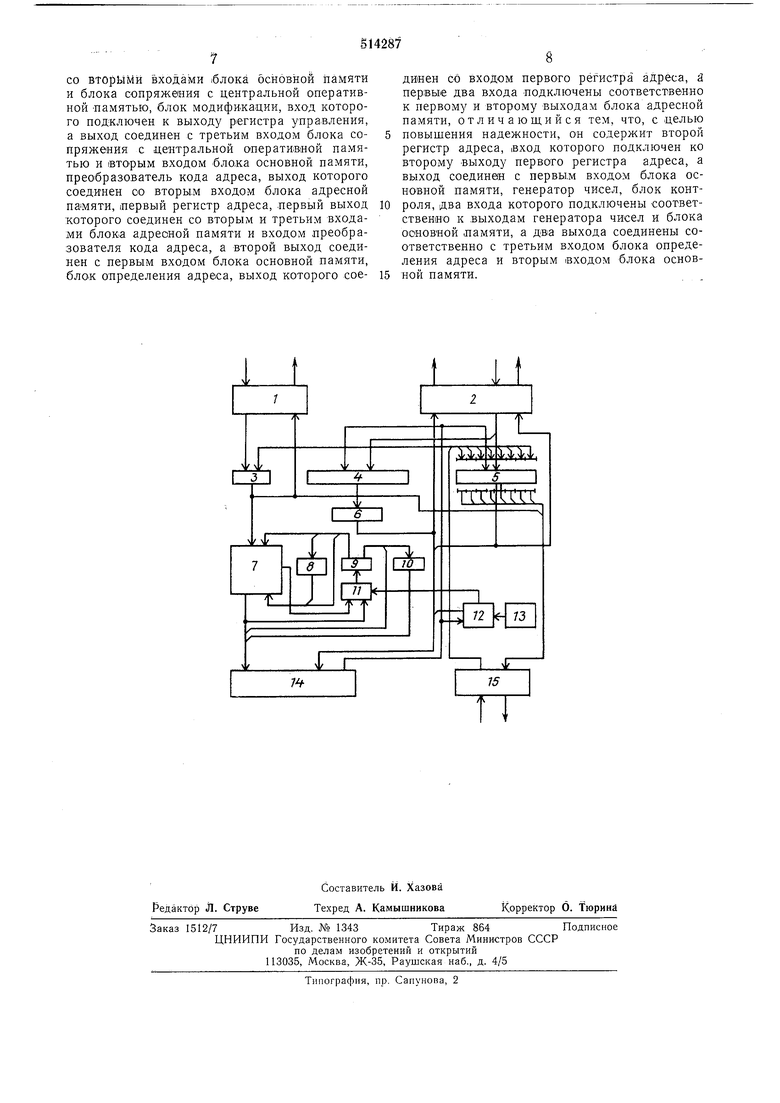

На чертеже приведена структурная схема описываемого мультиплексного канала.

Схема содержит: 1 - блок сопряжения с центральным процессором; 2 -блок сопряжения с центральной оперативной памятью; 3 - регистр подканала; 4 - регистр управления (регистр ключа защиты, регистр адреса команды (данных), регистр флажков, регистр кода операции, регистр счета данных); 5 - регистр информации; 6 - блок модификации адресов и счета данных; 7 - блок адресной памяти; 8 - преобразователь кода адреса; 9 - первый регистр адреса, фиксирующий адрес свободной (исправной) зоны основной памяти; 10 - второй регистр адреса; 11 -блок определения адреса свободной зоны основной памяти; 12 - блок контроля исправности ячеек зоны основной памяти; 13 - генератор чисел; 14 - блок основной памяти мультиплексного канала, предназначенный для хранения управляющей информации (программы) подканала (внешнего устройства); 15 - блок сопряжения с внешними устройствами.

Блок 7 предназначен для хранения таблицы адресов зон основной памяти мультиплексного канала и таблицы занятости (неисправности) этих зон. Таблица адресов зон основной памяти состоит из п, т-разрядных слов, где п - количество внеш-них устройств, подключенных к мультиплексному каналу; т - количество разрядов, достаточных для адресации всех зон основной памяти мультиплексного канала. Объем таблицы занятости (неиснравности) зон основной памяти (в битах) равен количеству зон основной па1мяти. В таблице позиЦИО.ННО запоминается состояние зон основной памяти.

Инструкция состоит из 32 разрядов О-31 (разряды О-7 - инструкция, разряды 16- 18 - адрес канала, разряды 24-31 - адрес внешнего устройства). Адресное слово канала содержит 32 разряда О-31 (разряды О-3 - ключ защиты, разряды 8-31 - адрес управляющего слова капала). Управляющее слово канала состоит из 64 разрядов О-63 (разряды О-7 - код операции, разряды 8-31- адрес данных, разряды 32-36 - флажки, разряды 48-63 - разряды счета данных).

В исходном состоянии адрес свободной (исправной) рабочей зоны блока основной памяти 14 хранится на первом регистре 9 адреса свободной зоны основной памяти мультиплексного канала. Определение исправности свободной зоны основной намяти проводится сразу, после общего сброса канала, как это описано ниже.

При поступлении инструкции «Начать 5 ввод - вывод от процессора в канал блок 1 сопряжения с центральным процессором выдает потенциал инструкции и код номера внешнего устройства для фиксации на регистре подканала 3. Через блок 2 сопряжения с 10 центральной оперативной памятью производится прием в канал адресного слова канала и по нему - управляющего слова канала с фиксацией управляющей информации нодканала на регистре управления 4. Модификация 15 адресов ячеек центральной оперативной памяти осуществляется блоком модификации 6, обмен данными с внешними устройствами - через регистр информации 5. После пересылки кода операции внешнему устройству и окон0 чания обмена между каналом и внешним уст-, ройством служебной информацией подканалу предоставляется свободная (исправная) рабочая зона блока основной памяти 14 для записи управляющей информации. Для этого со5 держимое первого регистра 9 переписывается на второй регистр 10 адреса основной памяти и используется в качестве адреса зоны основной памяти для хранения управляющей информации данного подканала. Одновременно Э с записью управляющей информации в основной памяти производится фиксация номера предоставленной внешнему устройству рабочей зоны в соответствующей ячейке таблицы адресов зон основной памяти муль5 ТИПЛ6КСНОГО канала, а признака занятости этой зоны - в таблице занятости (неисправности) основной памяти .мультиплексного канала. Таблицы хранятся в блоке адресной памяти 7. Фиксация этой информации в блоке 0 памяти 7 производится за два цикла обращения к ней. Для этого номер внешнего устройства с регистра подканала 3 переписывается на регистр адреса адресной памяти, а содержимое регистра 9 - на регистр слова адрес5 ной памяти. В первом цикле обращения к блоку памяти 7 происходит запись номера рабочей зоны основной памяти, выделенной в данный момент внешнему устройству, в ячейку таблицы адресов зон основной памяти, за0 крепленную за этим внешним устройством. После записи в таблицу адресов зон основной памяти содержимое младших разрядов регистра 9 переписывается через преобразователь кода адреса 8 на регистр слова блока памяти 7, а 5 содержимое старших разрядов регистра 9 - на место младших разрядов регистра адреса блока памяти 7, формируя адрес в таблице занятости (неиправности) зон основной памяти. Преобразование содержимого младших разрядов регистра 9 состоит в переводе параллельного двоичного кода в позиционный код адреса так, что каждой комбинации младших разрядОВ регистра 9 соответствует один разряд регистра слова адресной памяти. В старшем разряде регистра адреса адресной памяти

формируется признак обращения в таблицу занятости (неисправности) зон блока памяти 14 на регистр слова адресной памяти без предварительного сброса последнего, и в цикле восстановления информации производится запись признака занятости вместе со всеми уже имеющимися призлаками.

Далее .начинается поиск адреса новой свободной и исправпой зоны основной памяти. В режиме поиска адреса свободной (исправной) зоны последовательно опрашиваются в блоке адресной памяти 7 все ячейки таблицы занятости (Неисправности) зон блока памяти 14, а читаемая из адресной памяти информация анализируется в блоке 11 определения адреса свО)бодной зоны основной памяти. При обнаружении «нуля в прочитанном из адресной памяти слове содержимое регистра адреса адресной памяти переписывается в старшие разряды регистра 9 через блок И без преобразования, а содержимое регистра слова адресной памяти преобразуется блоком 11 в номер позиции «левого нуля в слове, представленный после преобразования в параллельном коде и фиксируемый в младших разрядах регистра 9. Сформированный на регистре 9 адрес свободной зоны переписывается на регистр адреса блока оовновной памяти 14, а генератор чисел 13 вырабатывает проверочную комбиницию, которая через блок контроля 12 ислравности ячеек зоны основной памяти помещается на регистр слова блока основной памяти 14. Проверочная комбинация записывается в первую ячейку выбра ниой новой свободной зоны осповной памяти и читается из нее. Если комбинация прочитана верио (это определяет блок 12), записывается и прочитывается следующая комбинация, проверяется следующая ячейка зоны и т. д. После проверки всех ячеек зо«ы процесс отыскания свободной зоны заверщается. Если результат проверки отрицательный, то в блоке памяти 7 в таблице занятости (неисправности) зон основной памяти для данной зоны фиксируется признак занятости (неисправности) и начинается процедура поиска адреса иовой свободной зоны и ее проверки, как описано выше.

Для проверки исправности ячеек зоны основной памяти используются интервалы времени («паузы) между Обращениями к основной памяти во время работы канала с внешними устройства ми. При этом инструкция «Начать ввод - вывод, приходящая от центрального процессора, не .начинает использоваться до окончания формирования адреса свободной и обязательно исправной зоны основной памяти, если такая ситуация возникает.

При появлении запроса абонента (внешнего устройства) на обслуживание номер внешнего устройства, полученный из интерфейса ввода - вывода через блок 15 сопряжения с внешними устройствами, фиксируется на регистре подканала 3 и переписывается на регистр адреса адресной памяти с признаком обращения в таблицу адресов зон основной памяти. Пз адресной памяти читается содержимое ячейки таблицы адресов зон основной памяти, закрепленных за выставившим запрос внешним устройством. Прочитанное слово используется в качестве адреса зоны, где хранится управляющая информация данного подканала. При возникновении ошибок в процессе чтения и записи управляющей информации из какой-либо зоны основной памяти корректируется таблица занятости (неисправности) зон основной памяти в блоке адресной памяти 7, и в дальнейшем эта зона основной памяти до восстановления не используется.

Программа работы этого внешнего устройства может быть повторена без остановки мультиплексного канала для ремонта памяти.

После нормального завершения работы внешнего устройства (кроме случаев возникновения ошибок) в таблице занятости (неисправности) зон основной памяти, хранящейся в блоке адресной памяти 7, стирается признак занятости зоны и освободившаяся зона основной памяти пригодна для использования другим внешним устройством.

Форм у л а и 3 о б р е т е н ия

Мультиплексный канал с косвенной адресацией памяти, содержащий блок сопряжения с центральным процессором, первый вход которого подключен к первому входу канала, а первый выход соединен с первым выходом канала, блок сопряжения с центральной оперативной памятью, первый вход которого подключен ко второму входу канала, а первые два выхода соединены соответственно со вторым и третьим выходами канала, блок сопряжения с внещними устройствами, первые вход и выход которого соединены соответственно с третьим входом и четвертым выходом канала, блок основной памяти, блок адресной памяти, первый выход которого соединен с первым входом блока основной памяти, регистр подканала, два входа которого подключены соответственно ко второму выходу блока сопряжения с центральным процессором и второму выходу блока сопряжения с внепгними зстройствами, а выход соединен со вторыми входами блоков сопрял ;ения с центральным процессором и внешними устройствами и с первым входом .блока адресной памяти, регистр управления, два входа которого подключены соответственно к выходу блока основной памяти и третьему выходу блока сопряжения с центральной оперативной памятью, регистр информации, три входа которого подключены соответственно к выходу блока основной памяти, второму выходу блока сопряжения с внешними устройствами и третьему выходу блока сопряЛСения с центральной оперативной памятью, первый выход соединен со вторым входОМ блока сопряжения с внешними устройствами, а второй выход соединен

со вторыми входами |блока основной памяти и блока сопряжения с центральной оперативной Памятью, блок модификации, вход которого подключен к выходу регистра управления, а выход соединен с третьим входом блока сопряжения с центральной оперативной памятью и вторым входом бло.ка основной памяти, преобразователь кода адреса, выход которого соединен со вторым входом блока адресной памяти, лервый регистр адреса, .первый выход которого соединен со вторым и третьим входами блока адресной памяти и входом цреобразователя кода адреса, а второй выход соединен с первым входом блока основной памяти, блок определения адреса, выход которого соедииен об входом первого регистра адреса, а первые два входа подключены соответственно к первому и второму выходам блока адресной памяти, отличающийся тем, что, с целью повышения надежности, он содержит второй регистр адреса, вход которого подключен ко второму выходу первого регистра адреса, а выход соединен с первым входОМ блока основной памяти, генератор чисел, блок контроля, два входа которого подключены соответственно к выходам генератора чисел и блока ооновной .памяти, а дв1а выхода соединены соответственно с третьим входом блока определения адреса и вторым входом блока основной памяти.

| название | год | авторы | номер документа |

|---|---|---|---|

| Мультиплексный канал | 1974 |

|

SU525941A1 |

| Мультиплексный канал | 1976 |

|

SU590725A2 |

| Мультиплексный канал с динамическим распределением памяти | 1977 |

|

SU674010A2 |

| Мультиплексный канал с динамическим распределением памяти | 1973 |

|

SU526877A1 |

| Мультиплексный канал многопроцессорной вычислительной системы | 1973 |

|

SU521559A1 |

| Мультиплексный канал с диагностикой неисправностей | 1974 |

|

SU516033A1 |

| Устройство обмена с косвенной адресацией | 1974 |

|

SU526878A1 |

| Мультиплексный канал | 1973 |

|

SU525079A1 |

| Мультиплексный канал | 1975 |

|

SU561955A1 |

| Мультиплексный канал | 1977 |

|

SU750469A1 |

Авторы

Даты

1976-05-15—Публикация

1973-12-20—Подача