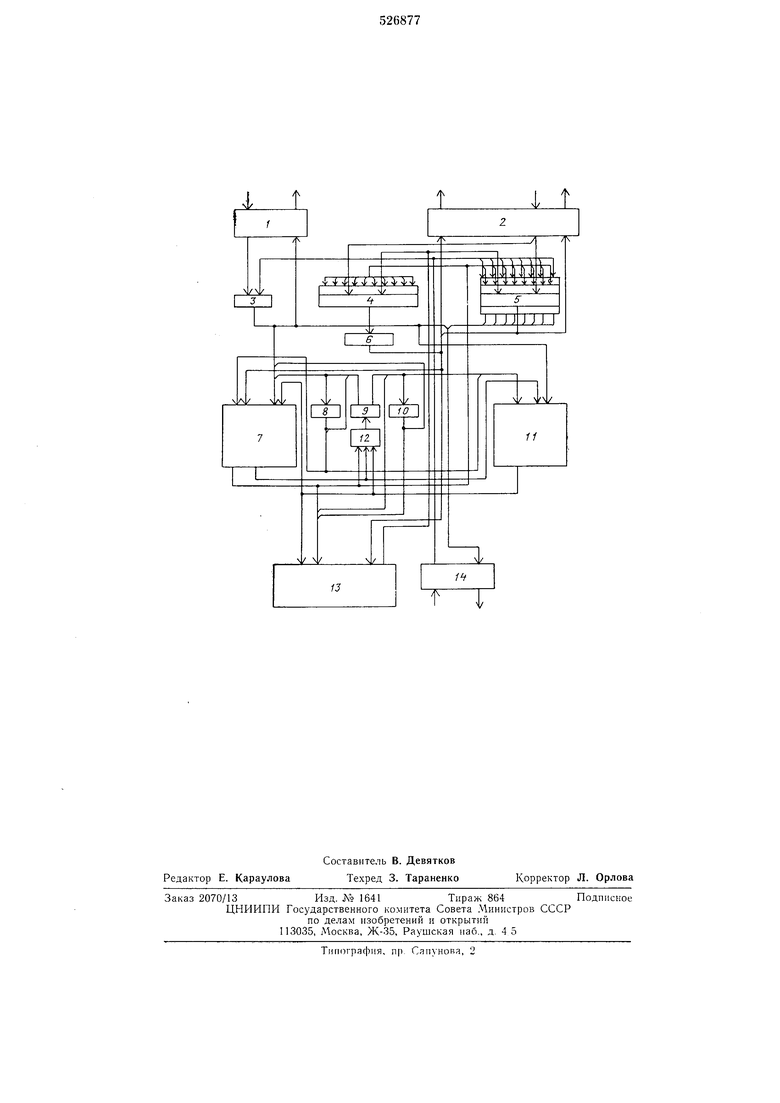

иыходу регистра управления, а выход соединен с третьим входом блока сопряжения с це1 тр 1льной оиеративной памятью и третьим входом блока осиовной намяти, выход иреобразоваиия кода адреса соединен с нерпым входом блока адресной памяти, первый per иcтpa адреса свободной зоны осиовной памяти соединен с первым и третьим входами блока адресной памяти и входом преобразователя кода адреса, а второй выход иодключен к второму входу блока основной намяти, выход блока определения адреса свободиой зоны основиой памяти сосдипеп с входом регистра адреса свободиой зоиы основной памяти, а иервые два входа подключены соответственно к первому и второму выходам блока адресной памяти, вход регистра адреса основиой памяти подключен к второму выходу регистра адреса свободной зоны основиой намяти, а выход соединен с вторым входом блока основной нам яти. Однако такой капал имеет низкую иадежиоеть. При общем отказе основиой или адресной памяти наступает полный отказ канала, а при отказе ячеек адресиой памяти нарушается работа внеиших устройств, связанных с этими ячейками. Цель изобретения - иовыишиие иадежностн мультиплексиого канала. Это достигается тем, что предлагаемый мультиилекспый канал дополнительно содержит блок резервной памяти, первый вход которого соедииен с вторым выходом регистра адреса свободной зоиы осиовной иамяти и с выходом иреобразователя кода адреса, второй вход подключен к второму выходу блока адресной намяти, третий вход соединен с выходом регистра подканала, выход подключен к третьему входу блока определения адреса свободной зоны основной иамяти, к первому входу блока основной памяти и к четвертому входу блока адресной памяти, выход блока модификации и второй выход регистра ииформации соединены с вторым входом блока адресной иамяти, первый выход блока адресной памяти подключен к третьему входу регистра уиравлеиия и четвертому входу регистра информации. На чертеже приведена схема предлагаемого канала с дииамическим распределением памяти. Канал содержит блок 1 сопряжения с центральным процессором, блок 2 соиряжеиия с центральной оперативной памятью, регистр 3 подканала, регистр 4 управления, регистр 5 информации, блок 6 модификации, блок 7 адресной памяти, преобразователь 8 кода адреса, регистр 9 адреса свободной зоны осиовной памяти, регистр 10 адреса осиовной иамяти, блок 11 резервной памяти, блок 12 оиределеиия адреса свободной зоны осиовной иамяти, блок 13 основной иамяти, блок 14 соиряжения с внешними устройствами. Канал работает следующим образом. о 10 15 20 25 30 35 40 45 50 55 60 65 В исходном состоянии адрес свободпой (исправной) рабочей зоиы блока 13 осиовной памяти мультиплексиого канала хранится на регистре 9 адреса свободной зоны основной намяти. Адрес свободиой (исправной) зоиы определяется сразу носле o6nierc) сброса канала с использоваиием блока 12 определения адреса свободной зоны основной па.мяти, иреобразователя 8 кода адреса и таблицы занятости (неисправности) зон блока 13, размеП1,еииой в блоке 7 адресной памяти. При этом осуществляется проверка зон осиовной иамяти иа исправность. При иостуилеиии от процессора в канал инструкции «Начать ввод - вывод блок 1 сопряжеиия с центральным процессором выдает призиак ииструкции и код номера внешнего устройства для фиксации на регистре 3 нодканала. Через блок 2 сонряжения с цеитральной оиеративиой иамятью ироизводи1ся прием в канал адресиого слова каиала и по пему - управляющего слова капала с фиксацией управляющей информации подкапала на регистре 4 управлеиия. Модификация адресов ячеек цеитральпой оперативной памяти осуществляется блоком .модификации 6. Обмеи даииыми с виептиими устройствами производится через регистр ииформации 5. После пересылки кода операции внешнему устройству и окончания обмена служебной информацией между каналом и внешним устройством иодканалу предоставляется свободная (исправиая) рабочая зона блока 13 для записи управляющей информации. Для этого с регистра 9 информация иереписывается на регистр 10 адреса основиой памяти и используется в качестве адреса зоны блока 13 для хранения управляющей ииформации данного подканала. Одновременно с записью управляющей информации в блок 13 производится фиксация адреса отведенной внешнему устройству зоны основиой иамяти в таблице адресов зои основиой памяти и через преобразователь 8 кода адреса в позиционном виде - признака занятости в таблице занятости (неисправности) зои основной памяти. После записи в этих таблицах какой-либо информации производится ее дублирующее считывание и определение исправности ячеек адресной иамяти. При неисправности ячейка адресной памяти заменяется ячейкой из блока 11 резервной иамяти. После фиксации информации в таблицах блока 7 адресиой памяти включается блок 12 определения адреса свободной зоны основиой иамяти для подготовки адреса свободной (исправной) зоны основной памяти к моменту поступления очередиой инструкции от центральиого процессора. При обнаружении неисправности ячейки адресной памяти адрес виещнего устройства с регистра 3 записывается в свободную ячейку ассоциативного (аргументного) поля, а адрес свободной исправной зоны основиой иамяти с регистра 9 - в соответствующую этому аргумситу ячейку информационно1Ч) (функционального) поля блока 11 резервной памяти.

При полном отказе блока 7 адресной памяти блок 1 I резервной памяти используется так же, как п при отказе отдельных ячеек адресной памяти. Замещение ячеек производится в пределах возможностей резервной памяти.

При полном отказе блока 13 основной памяти вся передаваемая и управляющая информация размещается в блоке 7, а функции адресной памяти полностью перекладываются па блок 11 резервной памяти. Адресная память разбивается на зоны с объемом, достаточным для .хранения передаваемой и управляющей информации подканала. Адресация зон адресной памяти осуществляется старщпми разрядами адреса ячеек. Поиск свободной (иснравной) зоны в адресной памяти происходит аналогично описанному выще основной памяти с использованием блока 12 и регистра 9. Таблица занятости (неисправности) зон адресной памяти формируется в ячейках резервной памяти аналогично тому, как это делается при функционировании основной памяти. При поступлении в канал инструкции «Начать ввод - вывод подготовленный па регистре 9 адрес рабочей зоны переписывается на регистр 10, а информация с занятости зоны - в соответствующую ячейку таблицы занятости в резервной памяти. Номер адресуемого инструкцией внещнего устройства и адрес предоставленной ему рабочей зоны запоминается в свободной ячейке блока 11. После этого начинается поиск очередной свободной (исправной) зоны адресной памяти.

При появлении запроса внещнего устройства на обслуживание адрес внешнего устройства, иолученный из интерфейса ввода - вывода через блок 14 сопряжения с внешними устройствами, фиксируется на регистре 3 подканала и служит для обращения в таблицу адресов зон основной памяти, размещенной в адресной памяти. Следует обращение к адресной памяти, и выбранное слово появляется на выходных щинах адресной памяти. Одновременно адрес внешнего устройства с выхода регистра 3 поступает на вход резервной памяти для поиска в ассоциативном поле. Если в процессе поиска этот адрес в ассоциативном поле блока 11 не обнаружен, то на адресный вход основной памяти коммутируется адрес рабочей зоны с выхода адрееной памяти. Если адрес внещнего устройства обнаружен в резервной памяти, соответствующий ему адрес зоны основной памяти появляется на выходе информационного поля блока 11. В этом случае прочитанный адрес коммутируется на адресный вход основной памяти. Информация, относящаяся к данному внешнему устройству, читается из блока 13 па регистры 4 п 5.

Процесс обслуживания запроса внешнего устройства при наличии сигнала неисиравности основной памяти начинается с поиска адреса рабочей зоны в резервной памяти. В качестг.е acconjiamnnoro признака используется

адрес оослуживаемого внешнего устройства. По сигналу неисправности основной памяти прочитанный из резервной памяти адрес зоны адресно памяти оммут руется па адреспьи

вход 7, а 1форМаЦ 1Я, рОЧПТа ая 13

адресной памят, фиксируется на 4 и 5. При записи информация подкана.та в случае полного отказа основной памят) оммутируется на информацнонный вход блока

7 адресной памяти.

Таким образом, предлагаемый мультиплексный канал позволяет обеспеч ть сохранение работоспособности по обслуж 1ваппю внешних устройств отказе одной или нескольких

ячеек зон основной памяти, прп отказе одной или неско,тьких ячеек адресно памят, npi полном отказе основной памяти, прп полном отказе адресной памяти.

При отказе ячеек зон осповной памяти неисправные зоны блокируются для использования. При отказе ячеек адресной памяти неисправная ячейка заменяется исправной резервной памяти. В ассоциативной (аргументной) части резервной памяти запоминается адрес внешнего устройства (пепсправной ячейки адрееной памяти), а в пнформац 1онной (функцпональной) части - адрес отведенной этому внешнему устройству зоны ос 1овной памяти. Сокращение колпчества одновременно

работающих устройств проходит лишь в случае, если количество отказавших ячеек адресной памяти больше возмож 1остей резервной памятп. Отказ ол чества ячеек адреспой памяти никакого влияния ta

работоспособность канала не оказывает. Прп полном отказе основной памяти адресная память используется для хранен я передаваемой и управляющей нформацнп. а резервная память - для хранения адресов зон, размещенных в адресной памятп. Комплект одновременно работающих устройств минимальный, но быть переменным по составу. При полном отказе адреспой памятп ее фу кции исполняет резервная память. Комплект

одновременно работа ощпх внешних устройств также минимальный, но может быть переменным по составу.

Формула 3 о б р е т е п я

А ультпплекспый капал с дпнамическ м распределением памяти, содержащий блок сопряжения с центральным процессором, блок сопряжепия с центральной оператпвпой памятью, блок сопряжения с внешними устройствами, блок основной памяти, блок адресной памяти, регистр подканала, регистр управления, регистр информации, блок МОДИф 1КаЦ,

преобразователь кода адреса, регистр адреса свободно зоны ocHOBHofi памяти, блок определения адреса свободной зоны основной памяти, регистр адреса основной памяти, вход блока сопряжен я с центральным процессором цодключе к .ому иходу

канала, а первый выход соединен с первым выходом канала, первглн вход блока сопряжения с центрально онеративной памятью иодключей к второму входу канала, а первые два 1 ыхода соединены соответственно с вторым и третьим выходами канала, первый вход и выход блока сопряжения с внешними устройствами соединены соответственно с третьим входом и четвертым выходом канала, первый выход блока адресной памяти соединен с вторым входом блока основной памяти, два входа регистра подканала подключены соответственно к второму выходу блока сопряжения с центральным процессором и второму выходу блока сопряжения с внешними устройствами, а выход соединен с вторыми входами блоков сопряжения с центральным процеесором и внешними устройствами и с третьим входом блока адресной памяти, первый и второй входы регистра управления соединены соответственно с третьим выходом блока сопряжения с центральной оперативной памятью и с выходом блока основной памяти, три входа регистра информации подключены соответственно к выходу блока основной памяти, второму выходу блока сопряжения с внешними устройствами и третьему выходу блока сопряжения с центральной оперативной памятью, первый выход регистра информации соединен с вторым входом блока сопрялсения с внешними устройствами, а второй выход соединен с третьим входом блока основной памяти, вторым входом блока сопряжения с центральной оперативной памятью, вход блока модификации подключен к выходу регистра управления, а выход соединен с третьим входом блока сопряжения с центральной онеративной памятью и третьим входом блока основной памяти, выход преобразователя кода адреса соединен с первым входом блока адресной памяти, первый выход регистра адреса свободнон :;о11ы основной плмяти соединен с нсрпым и третьим 1 ходами б.яока адресной памяти и г.ходом преобразователя кода адреса, а второй выход подключен к второму входу блока основной памяти, выход блока определения адреса свободной зоны основной памяти соединен с входом регистра адреса свободной зоны основной памяти, а первые два входа подключены соответственно к первому и второму выходам блока адресной памяти, вход регистра адреса основной памяти подключен к второму выходу регистра адреса свободной зоны основной памяти, а выход соединен с вторым входом блока основной памяти, о тличающийся тем, что, с целью повышения надежности, канал дополнительно содержит блок резервной памяти, первый вход которого соединен с вторым выходом регистра адреса свободной зоны основной памяти и с выходом

преобразователя кода адреса, второй вход подключен к второму выходу блока адресной памяти, третий вход соединен с выходом регистра подканала, выход подключен к третьему входу блока определения адреса свободной

зоны основной памяти, к первому входу блока основной памяти и к четвертому входу блока адресной памяти, выход блока модификации и второй выход регистра информации соединены с вторым входом блока адресной памяти, первый выход блока адресной памяти подключен к третьему входу регистра управления и к четвертому входу регистра информации.

Источники информации, принятые во внимание нри экспертизе:

1. Е. А. Дроздов, А. П. Пятибратов. Основы построения и функционирования вычислительных систем. М., «Энергия, 1973, стр. 152-162.

2. Авт. св. СССР Д 337777, кл. G 06F 3/04 от 13.08.69 (прототип).

it

tI

| название | год | авторы | номер документа |

|---|---|---|---|

| Мультиплексный канал с динамическим распределением памяти | 1977 |

|

SU674010A2 |

| Мультиплексный канал с косвенной адресацией памяти | 1973 |

|

SU514287A1 |

| Устройство обмена с косвенной адресацией | 1974 |

|

SU526878A1 |

| Мультиплексный канал | 1974 |

|

SU525941A1 |

| Мультиплексный канал | 1976 |

|

SU590725A2 |

| Мультиплексный канал многопроцессорной вычислительной системы | 1973 |

|

SU521559A1 |

| Мультиплексный канал | 1975 |

|

SU561955A1 |

| Мультиплексный канал с диагностикой неисправностей | 1974 |

|

SU516033A1 |

| Запоминающее устройство с самоконтролем | 1976 |

|

SU595795A1 |

| Мультиплексный канал | 1973 |

|

SU525079A1 |

Авторы

Даты

1976-08-30—Публикация

1973-10-29—Подача