первый вход которого связан ic выходом регистра подканала, и блок адресации, первый ВХОД которого соединеи с выходом блока памяти адресов, а выход - с вторым входом блока .памяти адресов и с первым входом блока основной памяти.

НедостатоК этого устройства - необходимость больплих затрат оборудования.

Цель изобретения - сокращение оборудования.

Это достигается тем, что устройство содержит первый и второй сдвигатели, .причем первый вход первого сдвигателя соединен с выходом блока основной памяти, а выход-с третьим входом регистра информации и вторым входом регистра управлеиия, Выход блока МодифИхации - с первым входом второго сдвигателя, Второй вход которого связан с вторым выходом регистра информации, а выход - со вторым ВХОДОЛ1 блока основной памяти. Второй и третий входы первого, третий и четвертый .входы второго сдвигателей .подключены соответственно к второ.му выходу регистра упр.авления и выходу блока адресации, вторым входом связанного с третьим выходом регистра управления, третий вход которого соединен с выходом блока адресации, а четвертый .выход регистра управления - с первым входом блока основной памяти.

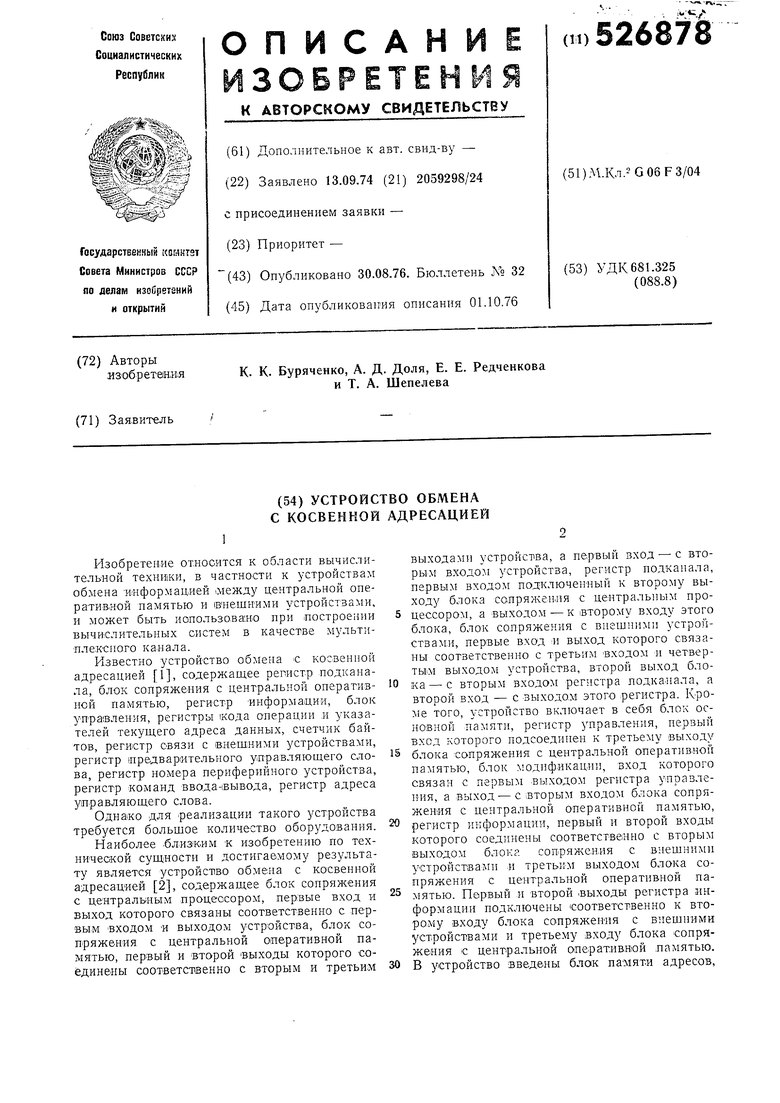

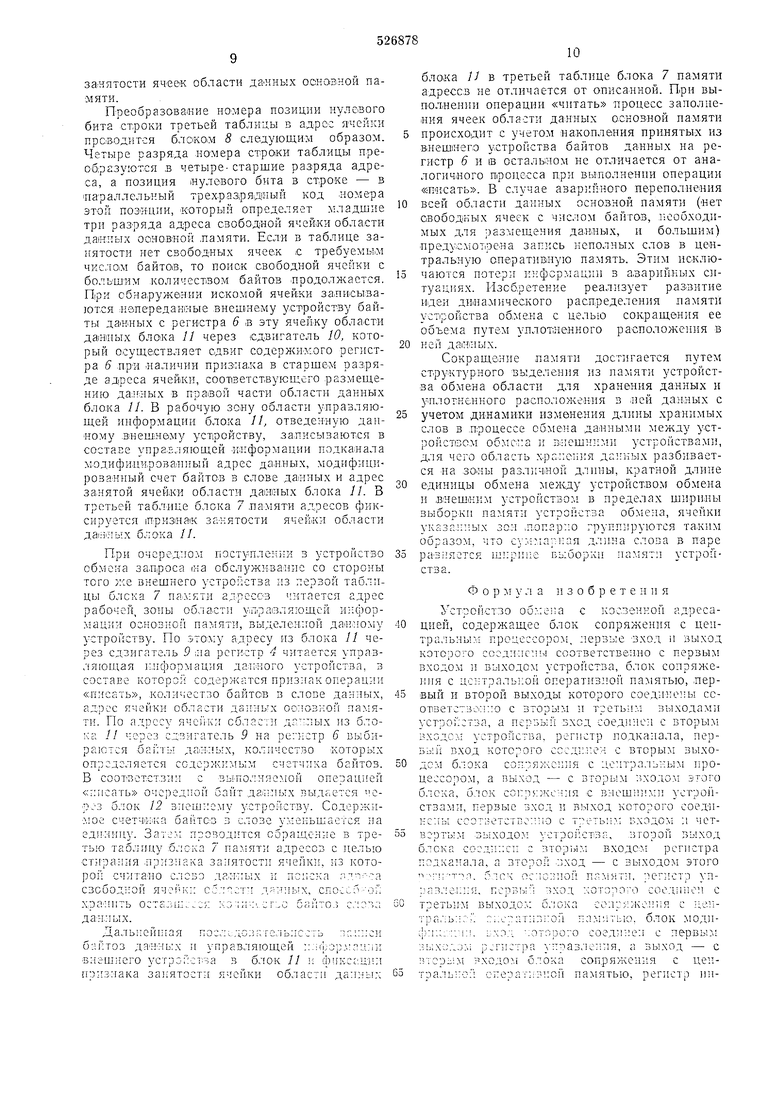

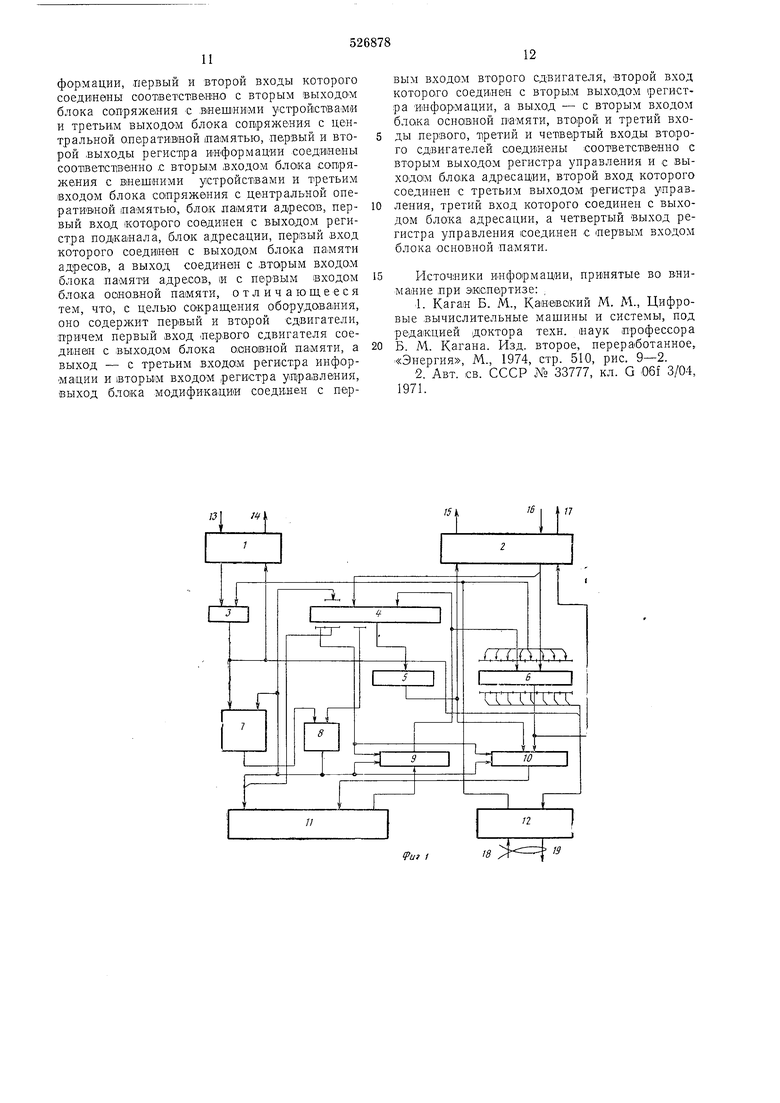

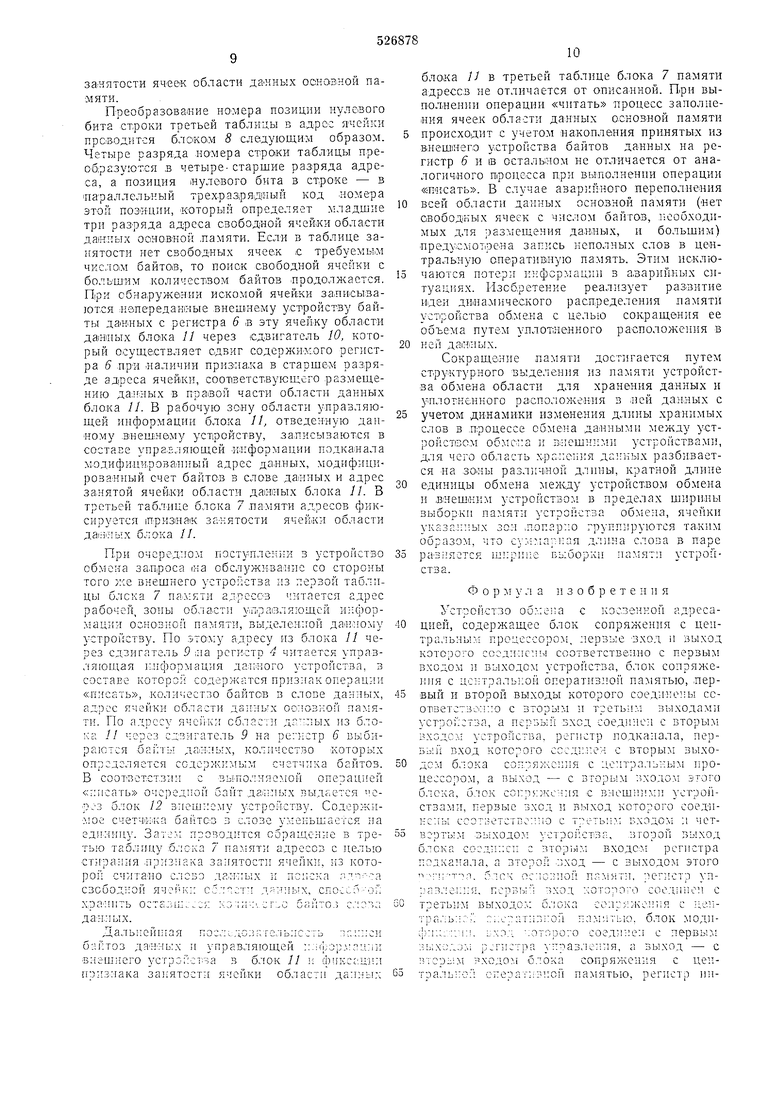

На фиг. 1 представлена блок-схема устройства об)мена; на фиг. 2 - раЗМещение информаци.и в блоке основной .памяти.

Устройство обмена с косвенной адресацией содержит (фиг. 1): блок / сопряжения с центральным процессором, блок 2 сопряжения с центральной оперативной памятью, регистр 3 подканала, регистр 4 управления, блок 5 модификации, регистр 6 ниформации, блок 7 памяти адресов, блок 8 адресации, первый 9 и второй 10 сдвигатели, блок // основной памяти, блок 12 сопряжения с внешиими устрой-ствами.

На фиг. 1 обоз.начены: 13-1первый вход устройства; 14-первый его выход; 15 - второй выход устройства; 16 - второй его вход; 17 - третий выход; 18 - третий вход; 19 - четвертый выход устройства.

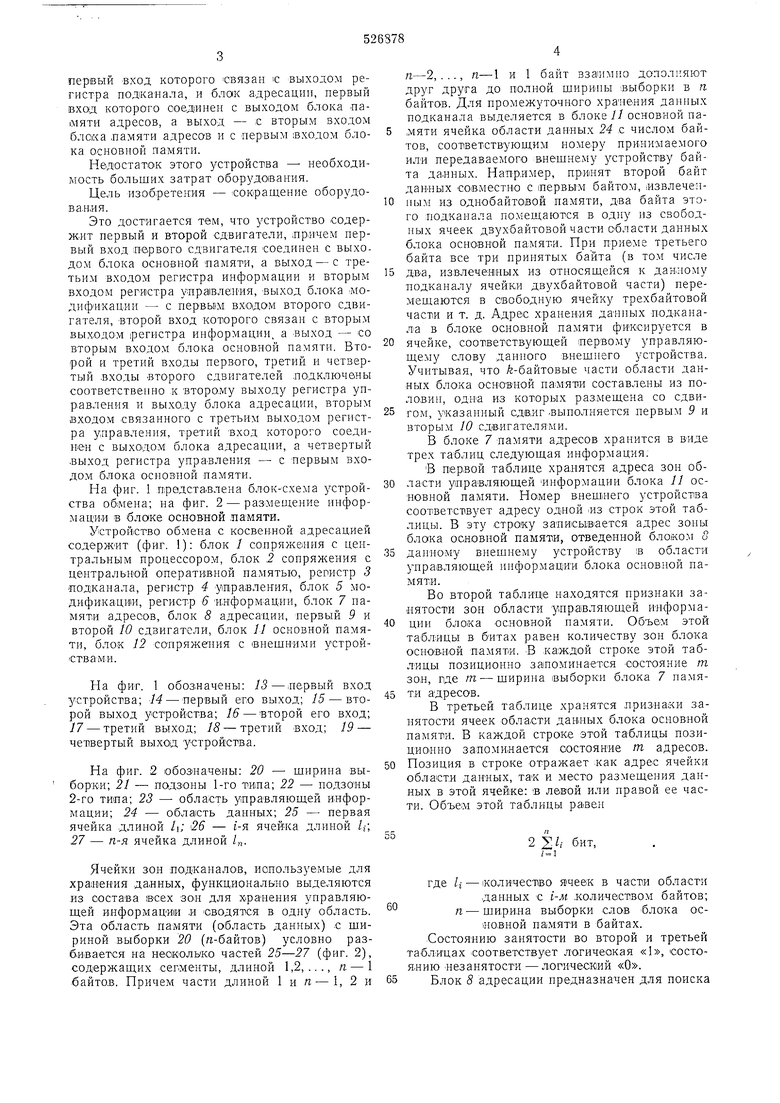

На фиг. 2 обозначбны: 20 - ширина выборки; 21 - подзоны 1-го типа; 22 - подзоны 2-го типа; 23 - область управляющей информации; 24 - область данных; 25 - первая ячейка .длиной /i; 26 - i-я ячейка длиной /,-; 27 - п-я ячейка длиной /„.

Ячейки зон лоДКаналов, используемые для храпения далных, функционально выделяются из состава )всех зон для хранения управляющей информации .и сводятся в одну область. Эта область памяти (область данных) с щириной выборки 20 (г-байтов) условно разбивается на несколько ча1стей 25-27 (фиг. 2), содержащих сегменты, длиной 1,2,..., п - 1 байтов. Причем части длиной 1 и «-1, 2 и

п-2,..., п-1 и 1 байт взаимно дополняют друг друга до полной щирины .выборки в п байтов. Для промежуточного храпения данных подканала выделяется в блоке // основной па.мяти ячейка области данных 24 с числом байтов, соответствующим номе.ру нриннмаемого илИ передаваемого внещнему устройству байта да.нных. Напр.имер, принят второй байт даННых совместно с первым байтом, извлеченпым из однобайтовой памяти, два байта этого подканала помещаются в одну из свободных ячеек двухбайтовой части Области данных блока основной памяти. При нриеме третьего байта все три принятых байта (в том числе

два, извлеченных из относящейся к данному подканалу ячейки двухбайтовой части) перемещаются в свободную ячейку трехбайтовой части и т. д. Адрес хранения данных нодканаЛа в блоке основной памяти фпксируется в

ячейке, соответствующей первому управляющему слову .данного внешнего устройства. Учитывая, что -байтовые части области данных блока основной памяти составлены из поло.вин, одна из которых раз.мещена со сдвигом, указаиный сдв.иг .выполняется первым 9 и вторым 10 сдв.игателями.

В блоке 7 памяти адресов хранится в виде трех таблиц следующая информация.

В первой таблице хра.нятся адреса зон области управляющей информации блока 11 основной памяти. HoiMep внеЩ|Него устройства соответствует адресу одной Из строк этой табЛ.ИНЫ. В эту стро.ку записывается адрес зоны блока основной памяти, отведенной блоко.м 8

данному внешнему устройству IB области управляющей информации блока основной памяти.

Во второй таблице находятся признаки занятости зон области управляющей ннформадин блока основной памяти. Объем этой таблицы в битах равен количеству зон блока ОСНОВ.НОЙ памяти. В каж.дой строке этой таблицы позиционно запоминается состояние т зон, где т-ширина выборки блока 7 памяти адресов.

В третьей таблице хранятся .признаки занятости ячеек области данных блока основпой памяти. В каждой строке этой таблицы позициОНно запоминается состояние т адресов.

Позиция в строке отражает как адрес ячейки области данных, так и место размещения данных в этой ячейке: В левой или правой ее части. Объеэд этой таблицы равен

2 2 ii бит,

( 1

где /г - количество ячеек в части облаСти данных С i-M .количеством байтов; п - щи.ри.на выборки Сло.в блока осНО.ВНОЙ памяти в байтах. Состоянию занятости во второй и третьей таблицах соответствует логическая «1, состоянию незанятости-дорический «О. Влок 8 адресации предназначен для поиска адреса свободной зоны в -блоке осноз1 ой памяти, служащей для хранения управляющей информации, и адреса ячейки области данных бло.ка основной памяти. Этот блок, использующийся в известном устройстве для определения адреса свободной зоны, может содержать, например, узел формирования адресов ячеек блока 7 памяти адресов, узел определения крайнего левого (или .правого) нуля в прочитанной из ячейки блока памяти адресов информации, узла кодирования .позиционного кода в параллельной для неревода номера позиции «уля в информации з .параллельный код адреса свободной зоиы, узел декодирования параллельного кода адреса в позиционный код и т. д. Дополнительно в устройстве блок 8 .проводит аналогичные действия с третьей таблицей занятости ячеек об.тасти данных блока основной памяти. Этот алгоритм цде нтичеи взаимодействую со второй таблицей и не .требует донолнительяого оборудования. Сдвигатели 9 и 10 предусмотрены для сдвига информации на целое число разрядов и могут быть выполнены ino любой известной схеме, например по матричной схеме на элементах 2И-2Р1ЛИ-НЕ. Блок 11 ОСНОВ.НОЙ памяти предназначен для хранения управляющей информации (программы) под1Ка.нала и данных. Основная память условно разделена иа две области: область управляющей .информации 23 и область данных 24. Область управляющей информации разбита 1на определенное количество зон, где хранится относящаяся к определенному внешнему устройству програ.мма: код выполняемой операции, счет байтов в слове, счет данных, адрес данных, адрес команды и некоторая другая информации, в то.м числе адрес ячей|ки области данных основной памяти, в (Которой хранятся данные, относящиеся к этому подканалу. При пекратности числа байтов зоны управляющей информации ширине выбор.ки из основной памяти область управляющей информации для удобства адресации может быть условно разделена на подзоны 21, имеющие слова, кратные ширине выборки, и подзоны 22, используемые для размещения неполных .слов управляющей информации. Каждая зона управляющ ей инфор(мации состоит из подзоны 21 и подзоны 22. Объем области управляющей информации основной памяти равен сумме.подзон 21 и 22. Объем области данных равен У /, ячеек с шириной выборки п байтов..В области данных группа ячеек 26 предназначена для хранения i байтов да«иых в левой части и п-i байтов в .правой. Последняя группа ячеек 27 предназначена для хранения п байтов каждая и используется при переполнении всех предыдущих групп области данных ооновной памяти. Устройство обмена управляется инструкциями и выполняет операции в соответствии с системой команд ЕС ЭВМ. Инструкция состоит из 32 разрядов О-31 (разряды О-7 -код инструкции, разряды 16-18-адрес капала, разряды 24-5/ - адрс: внешнего устройства). Адресное слово канала содерж.ит 32 разряда О-31} (разряды О-3 - ключ защиты, разряды 8-31 - адрес управляющего слова канала). Управляющее слово включает в себя 64 разряда р-63} (разряды О-7-код операции, разряды 8-31 - адрес данных, разряды 32-36 - флажки, разряды 48-63 - счет данных) . Работа устройства рассматривается на примере устройства со следующими характеристиками. Адресные возможности канала - 256 внешних устройств. Количество зон основной памяти - 128, объем управляющей информации (ключ защиты, признаки операции, счет байтов, счет данных, адрес данных, адрес команды и другая служебная информация) - 12 байтов, ширина выборки основной памяти - 8 байтов, длина слов обмана с центральной оперативной памятью - 8 байтов, Начальным сбросом устройство устанавливается в исходное состояние (сбрасываются все регистровые элементы и очищаются элементы па.мяти). После начального сброса блок 8 адресации проводит поиск адреса свободной зоны области управляющей информации блока 11 основной памяти во второй таблице занятости, (Находящейся в блоке 7 памяти адресов. В режиме пересчета строк этой таблицы блок 8 анализнрует содержимое каждой строки. При обнаружении нулевого бита в строке дальнейший нересчет строк блокируется, а номер Н031ЩИИ «крайнего левого (или «правого) нулевого бпта преобразуется блоком 8 в адрес свободной зоны области управляющей информации основной памяти. Адрес свободной зоиы фикс руется на выходе блока 8. При поступле-нип инструкции «начать вводвывод на вход 13 устройства блок / сопряжения с центральным процессором выдает признак инструкции и код номера внешнего устройства для фиксацИ|И на регистре 3 подканала. По входам 16 и 15 блок 2 сопрял епия с центральной операти:вной памятью проводит прием в устройство адресного слова канала и по нему управляющего слова канала с фиксацией управляющей ипформацПП подканала на регистре управления. Модификация адресов ячеек цептральпой оперативной памяти осуществляется блоком 5, обмен данными с внешними устройствами- через регистр 5 информации. После пересылки через блок 12 сопряжения с внешними устройствами по выходу 19 кода операции внешнему устройству и окончания обмена между устройством обмена и внеш.нлм устройством служебной информацией подканалу предоставляется подготовленный блоком 8 адрес

ОвобОДной зоны -области управляющей )нформадии основной памяти. Для плотного заполнения основной памятп каждая зона области управляющей информации разделяется на ПОДЗОНЫ 21 « 22. ПодзоБЫ 21 образуют область оСНавной памяти, .предназначенную для хранения восьми байтовых слов, а подзоны 22 - четырех байтовых слов управляющей п:кформации. Управляющая информация одного Подканала залол.няет одну лОДзону 21 и одну подзо-ну 22, всего 12 байтов. Адрес лолзоны 21 формируется блоком 8 из призна ка типа подзоны (нулевой разряд адреса), адреса золы (разряды 1-7), адреса первого байта в зоце (разряды 8-10) и легко трансформируется в адрес подзоны 22 нутем в::траво :на од;:;1 разряд и изменения признака типа под3OHL. Например, для упомяпуплх исходных ОСНОВНОЙ па.мяТи и адреса свободной зоны ОООС011 в блоке 8 бу,т,ет сформ-прооан 1;од адреса подзоны 21 (см. таблицу), трансформк.руемьи в код адреса потзоны 22 10€СОООИОО.

Разряд

9 i 0

Код

Управляющая инсрормация записывается в подзолу ос,новпой памяти через сдв;:гатель 10 со сдвигом, если адрес подзоны кратен четырем (нули в двух младщих разрядах), и без сдвига, если адрес кратеи воеьми (нул;и в трех младших разрядах). Адрес предоставлсьчюй BHCiJiieMv устройству рабочей зоны области управляющей иифор.чацш основиой памят:т запоминается в соответствующей номеру Енещнего уетройства строке первой таблицы блока 7 памятп адресов, предназначенной для храиения адресов ЗОН области упрапляюшсй информации осиозной намят. Во згорой таб,и;це занятости зои o6:iacTi: ::рапля О Ц::й инсЬормации осиовной памяти фи1 с; р ется приз-пак заиято::тн рабочей зоиь;, и;)едоставленной В:нен 1ел1у устройству.

Для описываемого примера иергая таблица бло::а 7 памяти адресов содержит 256 еелп;разрядиых строк. Разрядность етро ; опред,еляе ся необходимостью адресации 123 рабочих ЗОИ области управляюзлей информации основной памяти. Вторая таблица солержит 16 восьмнразрядиых строк. O6iuee ко.; ;чоство битов в таблице () дос.;точно для ф;кеации признаков занятост;; 123 рабочих ЗОИ. Адрес рабочей зоны (цанримор, 0000011), предоста;вленлой вуюшнему устройству, иреобразуется в блоке 8 в но.мер позиции бита для зпигси во вторую таблиц б.ло:;а ;;ал;яти адресов следующ.им образом. Старшие четыре разряда адреса (0000) определяет ) строки таблицы, а младшие три разряда Oil) --номер бита в этой строке.

При цоступлении в устройство обмана запроса ца Обслуживание со сторо:иы в-нешнего устройства из соответствующей данному В1нещ нему устройству CTipoiKH первой таблицы блока 7 Памяти адресов читается адрес рабочей 30iHbi области управляЮЩей инфорМации оонозной ламяти. Адрес рабочей зоны фиксируетея ,в блоке 8 п используется для фор|Мир01за1Н - я адресо.в подзон при обрЕщеии { в ооис,31ную память для чтения упра вляющей кмфор|Мацци дагнцого В|НещНего устройства. Упра вляющая Инфо-рмация считывается па регистр 4 через сдвигатель 9 из подзо гы основной па.мяти со сдвигом, если адрес подзоны кратен четыре м, и без едвига, если адрес подзо:иы кратен .восьми.

В составе управляющей икфорсутацицвнещнего устройства чцтаются npnaiia.K выпол.няемой операции и содержимое счетчика байтов Б слове да1Н.ных. .При вьгпол.неиии операции «ппсать устройство об.меиа читает на регистр 6 Информации из центральной оператн1В:иой иамяти через блс:к 2 сло.во даинных. Затем через блс.к 12 в:нец пему устройству выдается байт данных, содержимое ечетчика байтов iB слове уме-ньшаетея .па еди.иицу и проводится пои.ок ячейки области данных основной ламяти для записи .непереданных устройству байтов слова.

Б.ток 8 обеспечивает обр лцен;:е в блок 7 памяти адресов в третью таблицу заггятости ячеек области данных ос.нсвиой памяти и анализирует содержание той строки таб., .которой соответствует модифицированному счету байтов в слО|Ве даиньх. Номер позиции «самого левого нулевого бита нреобразуется блоком 8 в адрес свободной ячейки области да1Н|Ных оонот-ггой памяти. Область да.ниых делится па лс1вую и правую части. Паиример, память с шириной выборки восемь б;1Йтов содержит в .тевой части области дан.Щзх восемь групИ яче(м. Первая группа ячеек используется для хранения .осьми од ;обайтсвых слов, вторая -- для храненргя двухбайтовых слов и так дялее. Пра. часть облаети данных содержит груниы ячеек, котср};:е наед : значе -ь; для х:1анс П1Я елов с кол тчеством байтов, доиолжчющи.х слова из 5 4i;eK правой части областн данных дэ по;;lioii iH ipH:ibi выборкн вссс:,ь байтов. Первая г. ячеек кпавой части х.раиит восс.:ь гов1)1х с:;С|В, вто:1ая группа - восемь щести.байтозых слов и т. д. В рассматриваемом случае ячейка адресуется сс11ИразрядГ

адреса оняд КС

т г.р Н1 и и .р а

ны.; ;одо ;. 4..cvj. рсделяет признак левой или правой части области далиых, младшие три разряда - ячей.кн в группе ячеек одного типа. 1 ретья таблин.а блока на.мяти адресов в описывае 1ом примере аиалогнч:на второй таб.:нце ц содержит 16 восьмнразрядных етро.х. Общее за:нлто.сти ячСек области двойных оснавмой памяти. Преобразоваиие но-мера позиции нулевого бита строки третьей таблицы в адрес Ячейки преходится блс«0|М 8 следующим образом. Четыре разряда .номера строки та.блицы преоб;р2зу1от,ся В четыре- старшие разряда адреса, а позиция Нулевого бита в строке - в Параллельный трехразрядиый код номера этой ПОЗИЦИИ, который определяет младшие три разряда адреса свободной ячейки области дав-гных ооновкой ламяти. Если в таблице занятости нет свободных ячеек с требуемым ЧИСЛ01М байтов, то поиск свободной ячейки с больШИМ количеством байтов продолжается. При сбиаружейни искомой ячейки за.писываются напереданиые внешнему устройству байты данных с регистра 6 в эту ячейку области даииых // через сдвигатель 10, который осуществляет сдвиг содержимого регистра 6 лрИ маличии приз:иа,ка в старшем разряде адреса ячейки, соот1ветствуюн;его размещению да;Н:ных в нра1вой части области данных бло:ка и. В рабочую зону области управляющей информации блоха У/, отведен-ную данному В:неш-:нвму устройству, записываются в составе упра.Еляющей -информации подка«ала модифицирова нный адрес данных, модифицированный счет байтов в слове данных и адрес занятой ячейки области данных блока 11. В третьей таблице блока 7 памяти адресов фиксируется 1Приз1на К занятости ячейк} области дасиых блОКа //. При очередном поступленни в устройство обмена занроса 1на обслуживание со стороны того же внешнего устройства из первой таблнцы блока 7 па:л;яти адресов читается адрес рабочей, зоны облает) управляющей И;1формации основной памяти, выделенной данному устройству. По адресу из блока // через сдзигатель 9 i;ia реги-стр 4 читается управ; яюи 1,ая ннформац гя данного устройства, в составе которо: содержатся приз; ак операции «писать, количество байтов в слове данных, адрес ячейки области данных ооло-вной памяти. По адресу яченкн облас; данных из блока // через сдвигатель .9 на регистр 6 выбираются байты да1нных, количеетво которых оиределяетея содержимым счетчттка байтов. В еоответствин с выполняемой онерацией «:г:псать очередной байт данных выдаетея еpj3 блок 12 внешнему устройству. СодержиМое ечетчНка 6aiiTO:B в слове уменьшается на . Затем нровод 1тея обраш,ен;1е в третью таблицу 6;ici;a 7 па:-.яти адресов с целью стирания .признака занятости ячейки, из которой считано ел ОБО данных свободной ячс1м :: ; хранить осталп:.:.;;: к:;-1;гг.; данных. байтов данных внешнего устро признака занятости ячей.ки области данны:-; блока и ъ третьей таблице блока 7 памяти адресов не отличается от описанной. При выполнении операции «чптать процесс заполнения ячеек области данных о.сновной памяти происходит с учетом наколления принятых из внешнего устройства байтов да.нных на регистр & и IB остальном не отличается от аналогичного процесса при выполнении операции «писать. В случае авар :йного переполнения всей области даиных осно.вной памяти («ет свободных ячеек с числом байтов, г.еобходимых для размепления данных, и большим) предусмотрена запись неполных слов в центральную оперативную память. Зтим исключаются иотер; и};фсрмацни в аварийных ситуациях. Изобретение реализует развитие идеи дина.миче.ского распределения памяти устройства обмена с целью сокращения ее объема путе.м уплотненного расположения в ней даж1ых. Сокрашение памяти достигается путем структурного выделения из памяти устройства обмена области для хранения данных и уплотненного расположення в ней данных с учетол динамики изменения длины хранимых слов в .процессе обмена данными между устройством обмена и внешними устройствам, для чего область х.ранения данных разбивается на зоны различной длины, кратной длине единицы обмена между устройством обмена и внешним устройством в нределах ширины выбор.ки памяти устройства обме:та, ячейки указанных зо.н л.онарно группируются та.кнм образом, что суммарная д.П.на слова в паре ujiipHiie выборки устройФ о р у ;i а н з о б р е т е н н я Устройство обмена с косвенной адресацией, содержащее блок сопряжения с центральным процессором, нервые вход н выход которого соедннсны соответственно с первым входом н выходом устройства, блок сонряження с центральной оперативной памятью, первый и второй выходы которого соедине};ь соOTBeTCTBOiHHO с вторым н третьи},; выходами устройства, а иервый вход соединен е вторым входом устройства, регистр подканала, перВ1;:й вход которого С вторым выходом блока сонряження с центральным процессором, а выход - с вторым входом этого блока, С01:р5:жсния с внешн мн устройствамн, первые вход и выход которого соединены соответственно с т;:еть }л входом н четверть; выходом стройства, второй выход блока соединен с вторым входол регистра подканала, а второй .вход - с выходом этого ,,;-|;-.т-1л, бтсл основной . регистр унрявле.ннп, псрвьг; вход хоторо; о соединен е третьим выходом блока сопряжения с дентраль::/ ;:сг;ггнв :ой нл:л;1тью. блок модн.зого соедн;:ен с первым Н:1азлення, а выход - с формации, первый и второй входы которого соединены ооответстве-нио с вторым выходо-м блока сопряжбния с .внешними устройст вами и третьим выходОМ блока сопряжения с центральной олеративной памятью, первый и второй выходы регистра ийформацяи соединены соот1вет1СТ1венно ,с вторым входом блока сопряжения с внешйимн устройствами и третьим входом блока сооряжения с центральной оперативной памятью, блок памяти адресов, первый вход которого соедияен с выходом регистра подканала, блок адресации, первый вход которого соединен с выходом блока памяти адресов, а выход соединен с вторым входом блока памяти адресов, и с первым входом блока основной памяти, отличающееся тем, что, с целью сокращения оборудования, оно содержит пер1вый и второй сдвпгатели, причем первый вход первого сдвигателя соед ше1н с выходом блока основной памяти, а выход - с третьим входом регистра информации и вторым входом регистра управления, выход блока модификации соединен с первым входом второго сдвигателя, второй вход которого соединен с вторым выходом регистра информации, а выход - с вторым входом блока основной памяти, второй и третий входы первого, Т|ретпй и четвертый входы второго сдвигателей соединены соответственно с вторым выходом регистра управления и с выходом блока адресации, второй вход которого соединен с третьим выходом регистра управления, третий вход которого соединен с выходом блока адресации, а четвертый выход регистра управления соединен с первым входом блока основной памяти. Источники информации, принятые во внимание при экспертизе: , 1.Каган Б. М., Каневский М. М., Цифровые вычислительные мащины и системы, под редакцией доктора техн. наук профессора Б. М. Кагана. Изд. второе, переработанное, «Энергия, М., 1974, стр. 510, рис. 9-2. 2.Авт. св. СССР № 33777, кл. G 06f 3/04, 1971.

| название | год | авторы | номер документа |

|---|---|---|---|

| Мультиплексный канал с динамическим распределением памяти | 1977 |

|

SU674010A2 |

| Мультиплексный канал с косвенной адресацией памяти | 1973 |

|

SU514287A1 |

| Устройство для назначения подканалов | 1984 |

|

SU1264189A1 |

| Мультиплексный канал | 1974 |

|

SU525941A1 |

| Мультиплексный канал с динамическим распределением памяти | 1973 |

|

SU526877A1 |

| Устройство для обмена данными между оперативной памятью и периферийными устройствами | 1990 |

|

SU1837305A1 |

| Микропрограммный мультиплексный канал | 1985 |

|

SU1305693A2 |

| Мультиплексный канал | 1976 |

|

SU590725A2 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1280642A2 |

| Мультиплексный канал | 1975 |

|

SU561955A1 |

1

13

В 1/7

5i

8

tptji I

7

-J-

Авторы

Даты

1976-08-30—Публикация

1974-09-13—Подача