1

Изобретение относится к дискретной технике и может быть применена в качестве электронной схемы общего назначения, выполненной в виде интегральной схемы.

РЬвестен делитель частоты, содержащий /ьразрядкып двоичный счетчик, выполненный, нанример, на триггерах, и логические элементы И.

Однако в известном делителе частоты с ростом коэффициента деления растет число разрядов двоичного счетчика и количество дополнительных логических элементов, ирн номощн которых реализуется соответствующий коэффициент деления.

С целью повышения коэффициента деления в предлагаемый делитель введены два дополнительных триггера и логические элементы «Запрет, запрещающие входы которых соединены с входной щиной, при этом входы триг геров /г-разрядного двоичного счетчика через логические элементы И подключены к входной щине, а выход - к счетному входу первого дополнительного триггера, выходы которого через логические элементы «Запрет соединены с раздельными входами второго дополнительного триггера, выходы которого подключены к вторым входам логических элементов И.

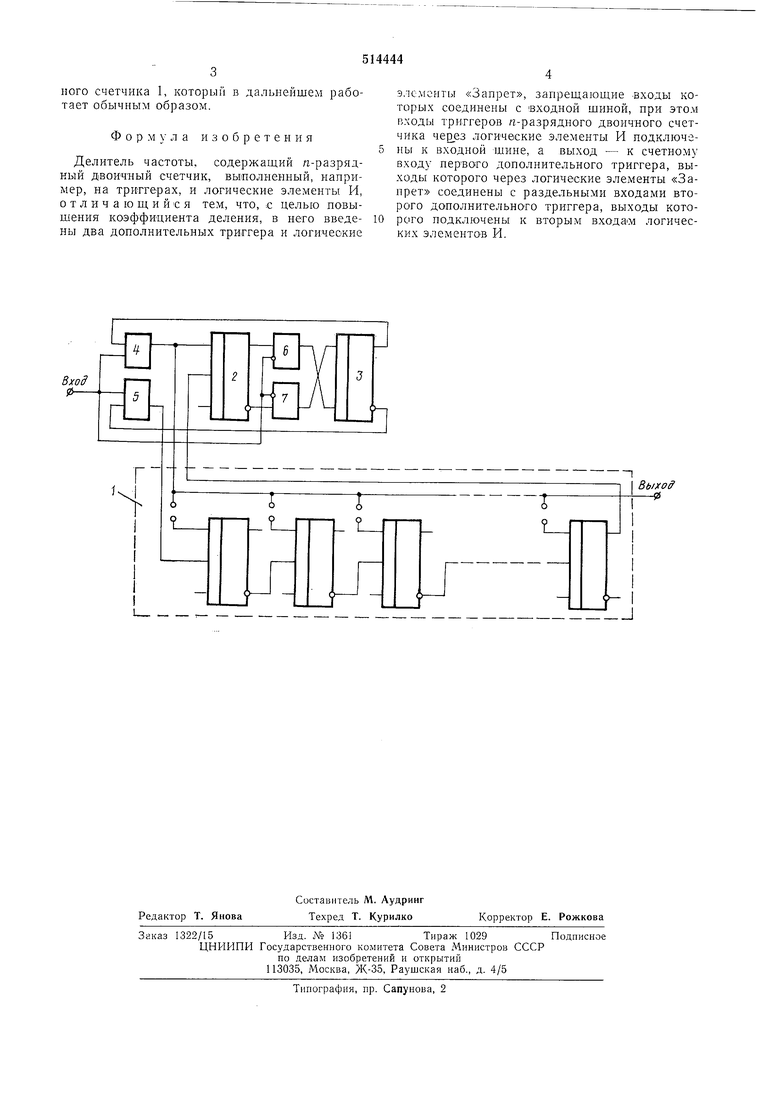

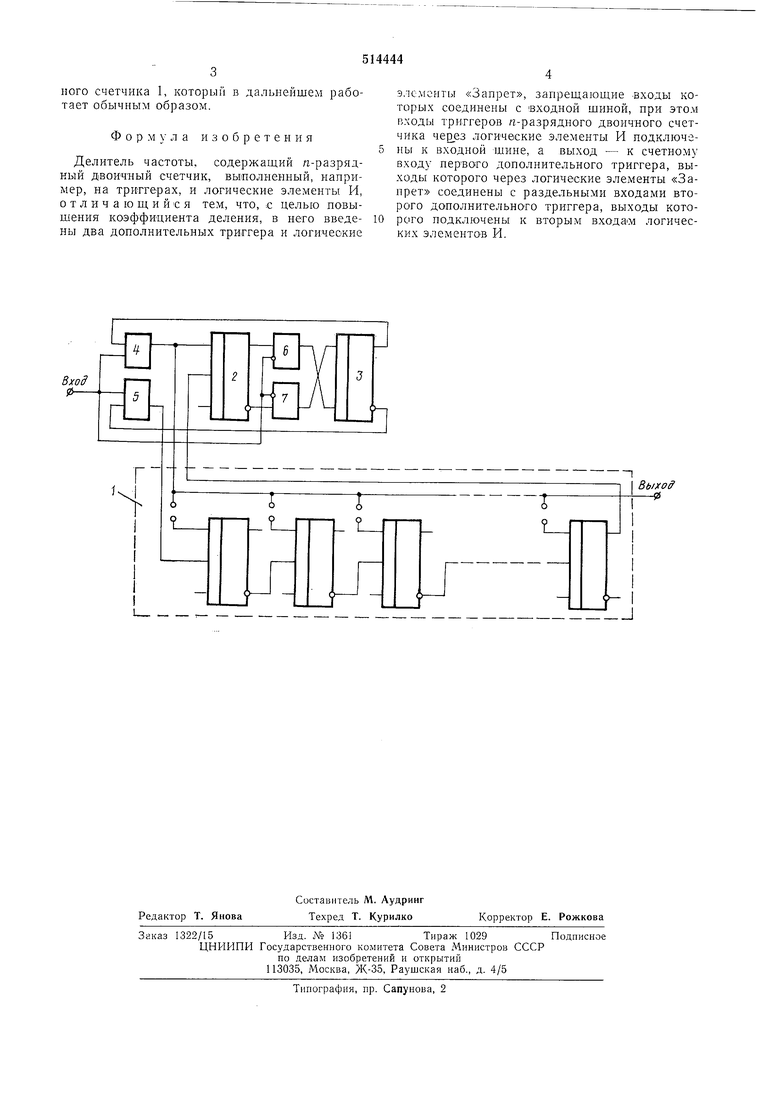

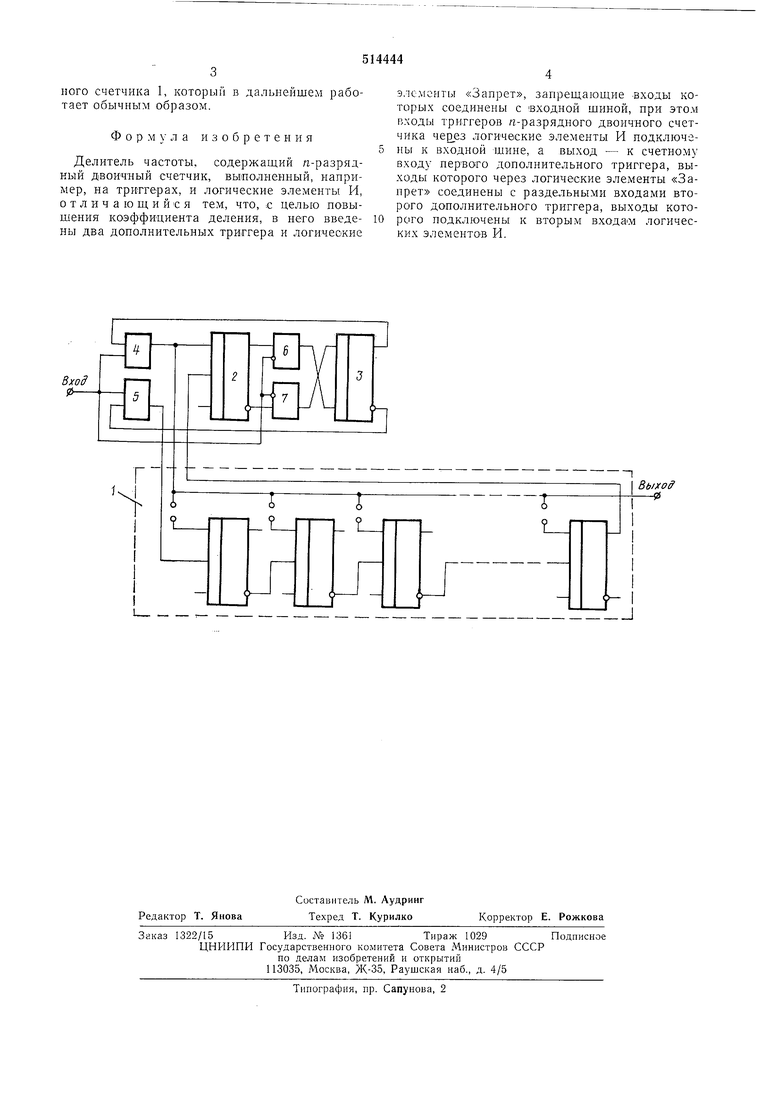

На чертеже представлена функциональная схема делителя частоты.

Делитель частоты состоит из /г-разрядного двончного счетчика 1, двух дополпительных триггеров 2 и 3, логических элСМептов И 4 и 5 и «Запрет 6 и 7.

В исходном состоянии все триггеры счетч; ка 1 и нервый дополнительный триггер 2 находятся в состоянии «О, а второй дополнительный триггер - в состоянии «1, при этом lia второй вход первого логического элемепта

И 4 от единичного плеча :второго дополнительного триггера 3 поступает разрещающий нотенцнал, а на второй вход второго логического элемента Н 5 ностунает запрещающий потенциал от нулевого плеча этого трнггера.

Работает делитель частоты следующим образом.

Первый входной импульс через первый логический элемент И 4 поступает на единичные входы ;г-разрядного двоичного счетчика 1.

Этот же имнульс устанавливает в состояние «1 первый дополп1ггольный трпь.ер 2, при этом на входы логических элементов «Занрет 6 и 7 поступает запреп1,аюпип 1 спгна;1, а второй дополннтельный триггер 3 изменяот свое состояние только после снятия этого сигнала, т. е. по его заднему фронту.

Последующие входные импульсы через второй логический элемент И 5, на втором входе которого паходнтся разрешаюп;нй потенциал, поступают на вход «-разрядного двоичного счетчика 1, который в дальнейшем работает обычным образом.

Формула изобретения

Делитель частоты, содержащий л-разрядный двоИЧный счетчик, вьюполиенный, например, на триггерах, и логические элементы И, отличающийся тем, что, с целью повышения коэффициента деления, в него введены два дополнительных триггера и логические

элементы «Запрет, запрещающие входы которых соединены с входной шиной, при этом входы триггеров «-разрядного двоичного счетчика через логические элементы И подключены к входной шине, а выход - к счетному входу иерваго дополнительного триггера, выходы которого через логические элементы «Запрет соединены с раздельными входами второго дополнительного триггера, выходы которого подключены к вторым входа м логических элементов И.

| название | год | авторы | номер документа |

|---|---|---|---|

| Делитель частоты следования импульсов с переменным коэффициентом деления | 1980 |

|

SU900460A1 |

| Счетчик с коэффициентом счета 2 +1 | 1978 |

|

SU766021A1 |

| Делитель частоты с переменным коэффициентом деления | 1983 |

|

SU1119174A1 |

| Счетчик с коэффициентом счета 2,1 | 1974 |

|

SU530468A1 |

| Делитель частоты импульсов | 1983 |

|

SU1162037A1 |

| Перестраиваемый делитель частоты следования импульсов | 1978 |

|

SU777824A1 |

| Устройство для умножения частоты следования импульсов | 1982 |

|

SU1040598A1 |

| Делитель частоты с любым целочис-лЕННыМ КОэффициЕНТОМ дЕлЕНия | 1979 |

|

SU839067A1 |

| Счетчик импульсов | 1977 |

|

SU680176A1 |

| Расширитель импульсов | 1980 |

|

SU902233A1 |

Авторы

Даты

1976-05-15—Публикация

1974-06-21—Подача