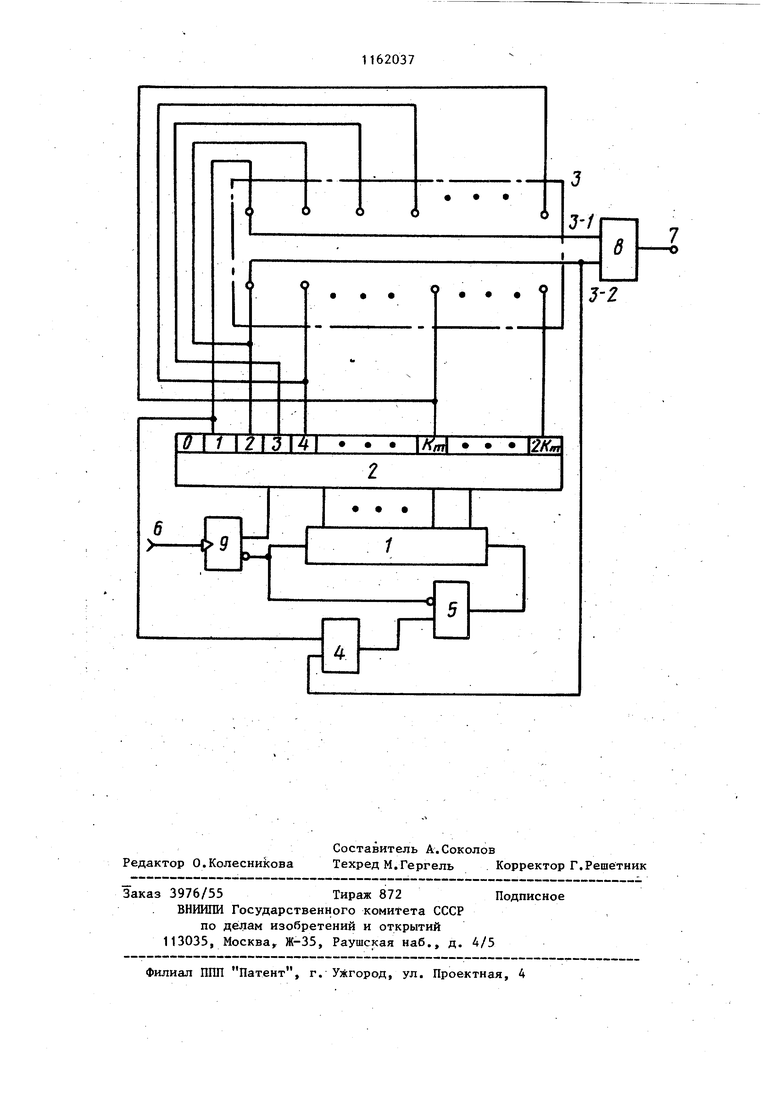

Изобретение относится к импульсной технике и может быть использовано в цифровой измерительной аппаратуре, а также в устройствах автоматики и телемеханики. Известен делитель частоты импульсов, содержащий два счетчика импульсов кольцевого типа, дешифратор, коммутатор, устанав1ливаю1ций коэффициент деления устройства, элемент И и блок сброса первого счетчика импульсов- lj . Недостаток устройства - ограниченное быстродействие, определяемое типом используемых счетчиков, Наиболее близким по теа нической сущности к данному является устройст во, содержащее счетчик импульсов, де шифратор, входы которого соединены с разрядньми выходами счетчика импульсов, коммутатор с двумя выходами соответствующими выбранному и удвоен ному коэффициентам деления, входы которого соединены с соответствующими выходами дешифратора, первый элемент ЗАПРЕТ, выход которого соединен с входом сброса счетчика импульсов, первый триггер, первый вход которого соединен с шиной установки, выход - с первым входом первого элемента И, второй вход которого соединен с входной шиной, счетным входом счетчика импульсов и первым входом первого элемента ЗАПРЕТ, второй вход которого соединен с выходом коммутатора, соответствующим выбранному коэффици енту деления, с первым входом второго триггера и с первым входом второго элемента И, выход которого соединен с вторым входом первого трйггера, а второй вход - с выходом младщего разряда счетчика импульсов выход коммутатора, соответствующий удвоенному значению коэффициента: деления, соединен с первым входом второго элемента ЗАПРЕТ, .второй вход которого соединен с выходом пер вого элемента И, а выход - с вторым входом второго триггера,первый и второй выходы которого соединены соответственно с первой и второй выходными шинами z. Недостаток устройства состоит в том, что его верхняя граничная частота значительно ниже максимальной частоты переключения триггеров счетчика импульсов. Это обусловлено тем что приведение устройства в исходное состояние перед очередным циклом деления происходит в паузе между К-м и К+1-М входными импульсами, в результате чего длительность переходных процессов при приведении устройства в исходное состояние определяет минимально возможную величину паузы между входными импульсами и, следовательно, ограничивает максимальную рабочую частоту делителя частоты импульсов. Цель изобретения - повышение быстродействия устройства. Поставленная цель достигается тем, что в делитель частоты импульсов содержащий счетчик импульсов, дешифратор, входы которого соединены с разрядными выходами счетчика импульсов, коммутатор с двумя выходами, соответствующими выбранному и удвоенному коэффициентам деления, входы которого соединены с соответствующими выходами дешифратора, R6 -триггер, элемент ЗАПРЕТ, выход которого соединен с входом сброса счетчика импульсов, и входную и выходную шины, введены элемент ИЖ и счетный триггер, счетный вход которого соединен с входной шиной, прямой выходс одним из входов дешифратора, а инверсный - со счетным входом счетчика импульсов и запрещающим входом элемента ЗАПРЕТ, управляющий вход которого соединен с выходом первого триггера, первый вход которого соединен с выходом Единица дешифратора, а второй - с выходом удвоенного коэффициента деления коммутатора и с первым входом элемента ИЛИ, второй вход которого соединен с выходом коэффициента деления коммутатора, а выход - с вькодной шиной. На чертеже прийедена электрическая структурная схема устройства. Делитель частоты импульсов содержит счетчик 1 импульсов, дешифратор 2, входы которого соединены с разрядными выходами счетчика 1 импульсов, коммутатор 3 с двумя выходами 3-1, 3-2, соответствующими выбранному и удвоенному коэффициентам деления, входы которого соединены с соответствующими выходами дешифратора 2, Я5-триггер 4, элемент 5 ЗАПРЕТ, выход которого, соединен с входом сброса счетчика 1 импульсов, входную шину 6, выходную шину 7, элемент 8 ИЛИ, счетный триггер 9, счетный вход кото3рого Соединен с входной шиной 6, пр мой выход - с одним из входов дешиф ратора 2, а инверсный - со счетным входом счетчика 1 импульсов и запре щающим входом элемента 5 ЗАПРЕТ, управляющий вход которого соединен выходом первого триггера 4, первый вход которого соединен с выходом Единица дешифратора 2, а второй с выходом удвоенного коэффициента деления коммутатора и с первым входом элемента 8 ИЛИ, второй вход которого соединен с выходом коэффи циента деления коммутатора 3, а выход - с выходной шиной 7. Устройство работает следующим об разом. Предположим, что исходное состоя ние устройства соответствует нулевым состояниям триггера 4, счетчика 1 и .триггера 9, выход 3-1 -коммутато ра 3 соединен с К-м выходом дешифра тора 2, при этом обеспечивается заданный коэффициент К деления, а выход 3-2 коммутатора 3 оказьшается соединенным с 2К-м выходом дешифратора 2. Входные импульсы на шине 6 считы ваются триггером 4 и счетчиком 1, на соответствующих выходах дешифратора 2, соединенных с неподвижными контактами коммутатора 3, поочередно появляются импульсы единичного уровня.. С приходом К-го входного импульса сигнал единичного уровня появляется на выходе 3-1 коммутатора 3 и через элемент 8 поступает на шину 7 С приходом (К+1)-го входного импульса сигнал на вькоде коммутатора становится равным нулю и, следовательно,, заканчивается вькодной импульс делителя частоты импульсов. С приходом 2К-ГО входного импульса сигнал единичного уровня появляется на выходе 3-2 коммутатора 3 и поступает через элемент 8 на шину 7,а также на второй вход триггера 4 Тригцер 4 переходит в единичное состояние, в результате чего на управляющий вход элемента 5 поступает сигнал единичного уровня. На запрещающем входе элемента 5, соединен ном с инверсным выходом триггера 9, в это время присутствует сигнал еди ничного уровня, так как триггер 9 каждым четным входным импульсом уста навливается в нулевое состояние. 374 С приходом (2К+1)-го входного импульса триггер 9 переходит в единичное состояние. При этом сигнал на выходе 3-2 коммутатора 3 становится равным нулю и, следовательно, заканчивается выходной импульс устройства. Сигнал нулевого уровня с инверсного выхода триггера 9 поступает на запрещающий вход элемента 5, в результате чего на выходе этого элемента появляется сигнал единичного уровня, по которому счетчик 1 устанавливается в нулевое состояние. Поскольку приведение счетчика импульсов в нулевое состояние происходит в интервале времени, когда триггер 9 находится в единичном состоянии, то после установки всех триг геров счетчика 1 в нулевое состояние на выходе Единица дешифратора 2 появляется сигнал единичного уровня. Этот сигнал поступает на первый вход триггера 4 и переводит его в нулевое состояние. При переходе триггера 4 в нулевое состояние сигнал на управляющем входе элемента 5 становится равным нулю, в результате чего сигнал на выходе этого элемента также становится равным нулю, прекращается обнуление счетчика импульсов. Таким образом, приведение счетчика 1 в нулевое состояние происходит в начале очередного цикла деления после подсчета первого в этом цикле входного импульса. В дальнейшем работа делителя частоты импульсов повторяется. Таким образом, введение в делитель частоты импульсов счетного триггера, работающего в режиме непрерывного двоичного счета, включенного между входной шиной и счетным входом счетчика импульсов, а также использоват ние элемента ЗАПРЕТ для управления сбросом в нуль счетчика импульсов в зависимости от состояния этого триггера позволило расширить интервал времени, в течение которого может производиться сброс счетчика импульсов в нуль до величины, равной периоду следования входных импульсов. при этом верхняя граничная частота работы устройства стала определяться практически быстродействием счетного триггера, включенного между входной шиной и счетным входом двоичного счетчика. Кроме того, в устройстве предусмотрен схемный контроль сброса счетчика импульсов в нуль,что позвояет исключить работу в цепях сброса .

J-/

| название | год | авторы | номер документа |

|---|---|---|---|

| Делитель частоты следования импульсов | 1980 |

|

SU949822A2 |

| Делитель частоты с изменяемым коэффициентом деления | 1980 |

|

SU900459A2 |

| Делитель частоты с переменным коэффициентом деления | 1988 |

|

SU1547057A2 |

| Устройство для преобразования частоты следования импульсов | 1978 |

|

SU764114A1 |

| Цифровой интегратор с контролем | 1975 |

|

SU540269A1 |

| Делитель частоты следования импульсов | 1984 |

|

SU1181134A1 |

| Устройство для вычисления временных интервалов микропроцессорных систем | 1980 |

|

SU960781A1 |

| Делитель частоты с переменным коэффициентом деления | 1985 |

|

SU1307587A1 |

| Делитель частоты следования импульсов с переменным коэффициентом деления | 1980 |

|

SU900460A1 |

| Делитель частоты с изменяемым коэффициентом деления | 1979 |

|

SU783996A1 |

ДЕЛИТЕЛЬ ЧАСТОТЫ ИМПУЛЬСОВ, содержащий счетчик импульсов, дешифратор, входы которого соединены с разрядными выходачи счетчика импульсов, коммутатор с двумя выходами, соответствующими выбранному и удвоенному коэффициентам деления, входы которого соединены с соответствующими выходами дешифратора, R5триггер, элемент ЗАПРЕТ, выход которого соединен с входом сброса счетчика импульсов, и входную и выходную шины, отличающийся тем, что, с целью повышения быстродействия, в него введены элемент ИПИ и счетный триггер, счетный вход которого соединен с входной щиной, прямой выход - с одним из входов дешифратора, а инверсный - со счетным входом счетчика импульсов и запрещающим входом элемента ЗАПРЕТ, управляющий вход которого соединен с выходом первого триггера, первый вход которого соединен с выходом Единида дешифратора, а второй - с выходом удвоенного коэффициента деления коммутатора и с первым входом элемента ИЛИ, второй вход которого соединен с выходом коэф4в1циента деления коммутатора, а выход - с выходной шиной.

. . . 9 . . .

-г

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| ДЕЛИТЕЛЬ ЧАСТОТЫ | 0 |

|

SU278761A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Авторское свидетельство СССР № 913602, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1985-06-15—Публикация

1983-12-07—Подача