Изобретение относится к цифровым делителям частоты следования импульсов и может быть использовано в ЦИ|фровых синтезаторах частоты и устройствах .синхронизации цифровых систем.

Известно устройство для деления частоты импульсов, содержащее счетчик, триггеры, вентили, инвертор и генератор эталонного сигнала 1.

Недостатком данного устройства является не.достаточио высокая скорость измерения .коэффициента .деления.

Известно также устройство, со..держащее двои-чный счетчик импульсов, включающий в себя буферный и информационный регистры и сумматор, формирователь синхроимпульсов, еыходы которого соединены со входами Синхронизации счетчика импульсов, первый - неп-осредственло, а гвторой - через элемент И, инверторы, элементы И - ИЛИ, триггер, элемент ИЛИ и два элемента еравнения, .первые входы первого из которых соединены с разрядными выходами счетчика импульсов, первые входы второго - с выходами элементов И - ИЛИ, а вторые входы обоих элементов сравнения - с шиной управления 2.

Недостатком данного устройства является сложность.

Целью изобретения является упрощение устройства.

Поставленная цель .достигается тем, что :в перестраиваемый делитель частоты следования импульсов, содержащий двоичный счетчиж импульсо в, формирователь си«хроИ1млульсо1в, первый выход которого соедине.н с первым входом синхронизацией двоичного счетчика импульсов, а второй выход - не10посредственно с Первым .ВХО.ДОМ первого элемента И, второй вход которого подключен ко входу инвертора и выходу элемента сравнения, а через второй элемент И, .второй вход которого подключен к выходу инвертора,- со вторым Входом синхролизации двоичного счетчика импульсов, разрядные выходы которого сое.динены с первыми входами элемента сраВнения, вторые вхо.ды которо.го подключены к кодовой шине, элемент ИЛИ .и триггер, введены дополнительный элемент И и дополнительные триггеры, первый вхо.д .первого из которых соединен с шиной управления, второй вход - с ВЫХО.ДОМ первого элемента И, пер25 вый выхо.д - с первым установочным входом двоичного счетчи1ка импульсов и первым ВХО.ДОМ триггера и второй выход - со вторым установочным входом счетчика имлульсов и первым входом элемента ИЛИ,

30 второй вход которого соединен с выхо.дом

дополнительного элемента И, первый вход которого соединен с первым выходом формирователя синхроимпульсов, второй .вход- с выходом триггера, второй вход которого соединен со вторым .входом синхронизации двоичного счетчика импульсов, а выход элемента ИЛИ подключен ,ко входу второго дополнительного триггера.

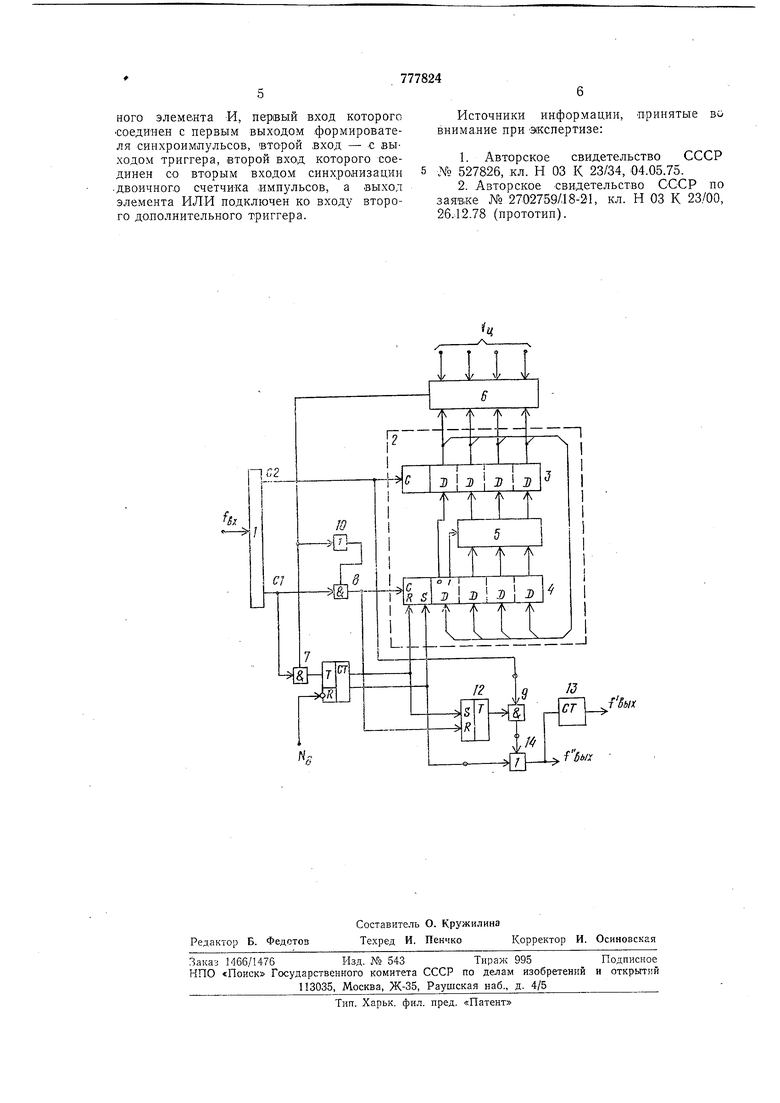

На чертеже представлена структурная электрическая схема устройства.

Оно содержит формирователь 1 синхроимпульсо;Б, Счетчик 2 двоичных импульсов; регистр 3 информационный двоичного счетчика импульсов, регистр 4 буферный двоичного счетчика импульсов, сумматор 5 двоичного счетчика импзльсов, элемент 6 сравнения, элементы И 7-9, инвертор 10. триггеры -11-.13, элемент ИЛИ 14. Триггеры 11, 13 .выполнены со счетным входом.

Перестраиваемый делитель частоты следования импульсов работает следующим образом.

Частота /ох поступает на формирователь 1, на первом выходе .которого фор ируется импульсная последовательность (С) с частотой и фазой, равными частоте и фазе .входного сигнала /вх а на втором выходе- импульсная последовательность (С2) с частотой /сх отстающая по фазе на Г80° (сдвинутая на величину Т-х/З). В зависимости от формы входн|ого сигнала, конкретная реализация формирователя 1 может быть различной.

В исходном состоянии на выходе элемента 6 присутствует «пулевой Потенциал, запрещающий прохождение синхроимпульсов С1 через элемент 7 и через инверто,р W разрещающий прохо кдение С/ через э.лемент 8 на синхровход (С) регистра 4.

С поступлением .каждого импульса С1 содержимое регистра 3 переписывается з регистр 4, при этом па вы.ходе сумматора 5 формируется число, равное сумме содержимого (п-1)-го старщих разрядов регистра 4 и значения первого разряда регистра 4 (все разряды - ).

Таким образом, с приходом каждого импульса серии С2 содержимое регистра 3 увеличивается на единицу по -сравнению с предыдущим значением.

При достижении содержимым регистра 3 величины ./Уц {целая часть .коэффициента деления относительно или старщие (п-1) разряды коэффициента деления, относительно /вых), срабатывает элемент 6, и «единичный сигнал с его выхода запрещает прохождение С1 па С-вход регистра 4 и разрещает прохождение С1 на счетный вход триггера //. Реакция триггера /7 на воздействие сигнала С1 зависит от значения Л/л (дробная часть - 0,5 - коэффициента деления, относительно или пер.вый разряд коэффициента деления относительно /вых.). Если Лд 0, то триггер 11 заблокирован по входу R, и на его первом выходе формируется импульс, поступающий на R-вход, регистра 4 и обнуляющий его. Если Nji, то триггер JJ разблокирован, и при каждом срабатывании элемента 6 .импульс С.1, поступая на счетный вход триггера 11, переключает его в противоположное состояние и формирует на его вы.ходах импульсы переноса. При этом пмЛульс переноса с первого выхода, поступая на вход R регистра 4, обнуляет его и ставит в .«единичное состояние триггер 12, разрещая при этом прохождение импульса С2 через элемент 9, элемент 14 на выход (Гвы.х) и выход триггера 13, формирующего

выходной сигнал / „ых-Импульс со второго выхода триггера // устанавливает «I в пэрвом разряде регистра 4 и через элемент 14 формирует сигнал , а поступая на триггер ,13, формирует на его выхо.де симматричный сигнал /выл-- Таким образо л, перестраиваемый делитель частоты формирует сигнал / /BxWynp, являющийся симметричным 1«меапдр.ом при лю-бом целом

Nyu,,H импульсный сигнал / / вх Л упрЗ.

Таким образом, предлагаемая реализация перестраиваемого делителя частоты позволяет исключить элемент сравнения и элементы И- ИЛИ, объем которых прямо

пропорционален числу разрядов счетчикаделителя импульсов, -что, в свою очередь, сокращает объем оборудования устройства в целом и .ведет к упрощению устройства.

Фор (М у л а и 3 о б .р е т е II и я

Перестраиваемый делитель частоты следования импульсов, содержащий двоичный счетчик импульсов, фор.мирователь

синхроимпульсов, парвый ВЫХОД которого соединен с первым входом синхронизации двоичного счетчика импульсов, а второй выход - непосредственпо с первым входом .первого элемента П, второй вход которого

подключен ко входу инвертора и выходу элемента сравнения, а через второй элемент И, второй вход которого подключен к выходу ипвертора,- со вторым входом синхронизации двоичного счетчика импульсов,

разрядные выхо.ды которого соединены с первыми входами элемента сравнения, вто-рые входы .которого подключены к кодовой щине, элемент ИЛИ и триггер, отличающийся тем, что, с целью упрощения устройства, в него введены дополнительный, элемент И и дополнительные триггеры, первый вход первого из которых соединен с щиной управления, -второй вход - с выходом -первого элемента П, .первый выход - с

пе.рвым установочным входом .двоичного счетчика импульсов и первым входом триггера и второй выход, - со вторым установочным входом счетчика импульсов и первым входом элемента ИЛИ, второй вход

которого соединен с выходом дополнительного элемента И, первый вход которого соеди-нен с первым выходом формирователя синхроимпульсов, второй вход - .с выходом триггера, второй вход которого соединен со вторым входом синхронизации двоичного счетчика импульсов, а выход элемента ИЛИ подключен ко входу второго дололнительного триггера.

Источники информации,

принятые во внима.ние при экспертизе:

1.Авторское свидетельство СССР № 527826, кл. Н 03 К 23/34, 04.05.75.

2.Авторское -свидетельство СССР по заявке № 2702759/18-21, кл. Н 03 К 23/00, 26.12.78 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Перестраивающий делитель частоты | 1977 |

|

SU661813A1 |

| Способ маркирования информационных комбинаций в системах последовательной записи с двухчастотным кодированием и устройства записи и воспроизведения для его осуществления | 1987 |

|

SU1543445A1 |

| Устройство для распознавания контуров изображений | 1983 |

|

SU1156103A1 |

| АДАПТИВНЫЙ ЦИФРОВОЙ ЧАСТОТНЫЙ ДИСКРИМИНАТОР | 2000 |

|

RU2166773C1 |

| Цифровой квазикогерентный фазовый демодулятор | 1980 |

|

SU902301A1 |

| Устройство для числового программного управления | 1985 |

|

SU1352459A1 |

| Устройство поэлементной синхронизации | 1985 |

|

SU1319301A1 |

| Синхрогенератор | 1989 |

|

SU1672586A1 |

| Устройство синхронизации | 1988 |

|

SU1644398A1 |

| Устройство для воспроизведения изображения | 1980 |

|

SU1085014A1 |

/

i i/ t

Пых

Пш

Авторы

Даты

1980-11-07—Публикация

1978-12-26—Подача