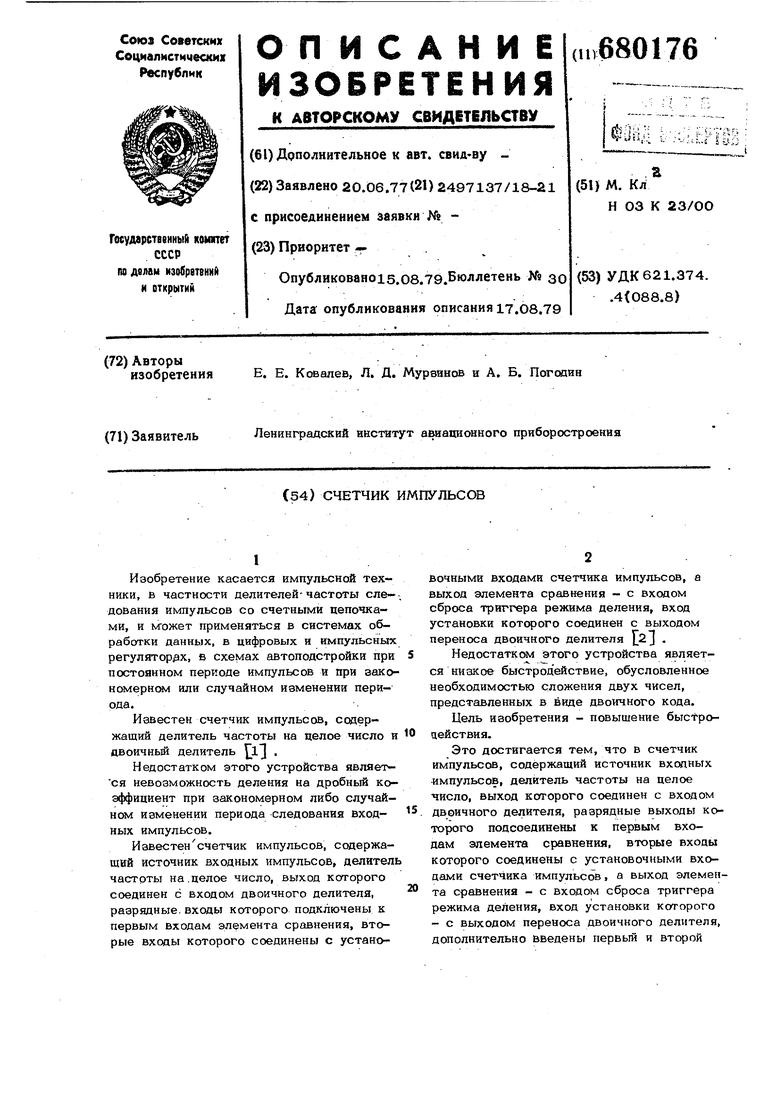

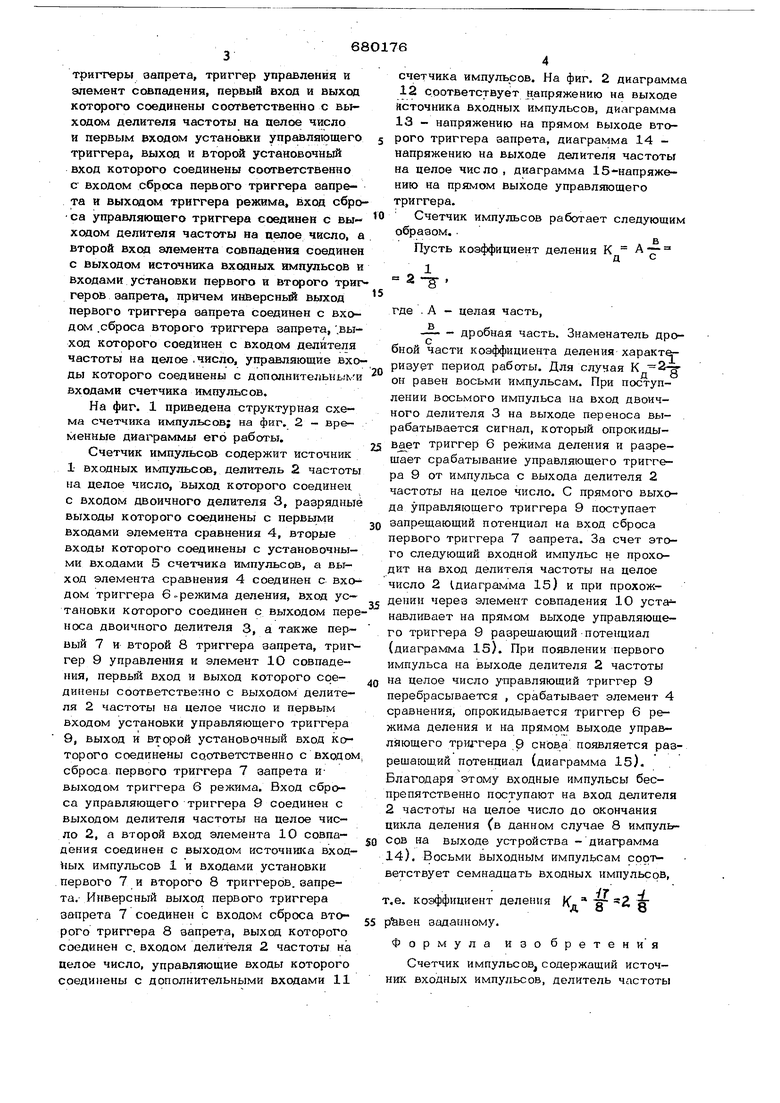

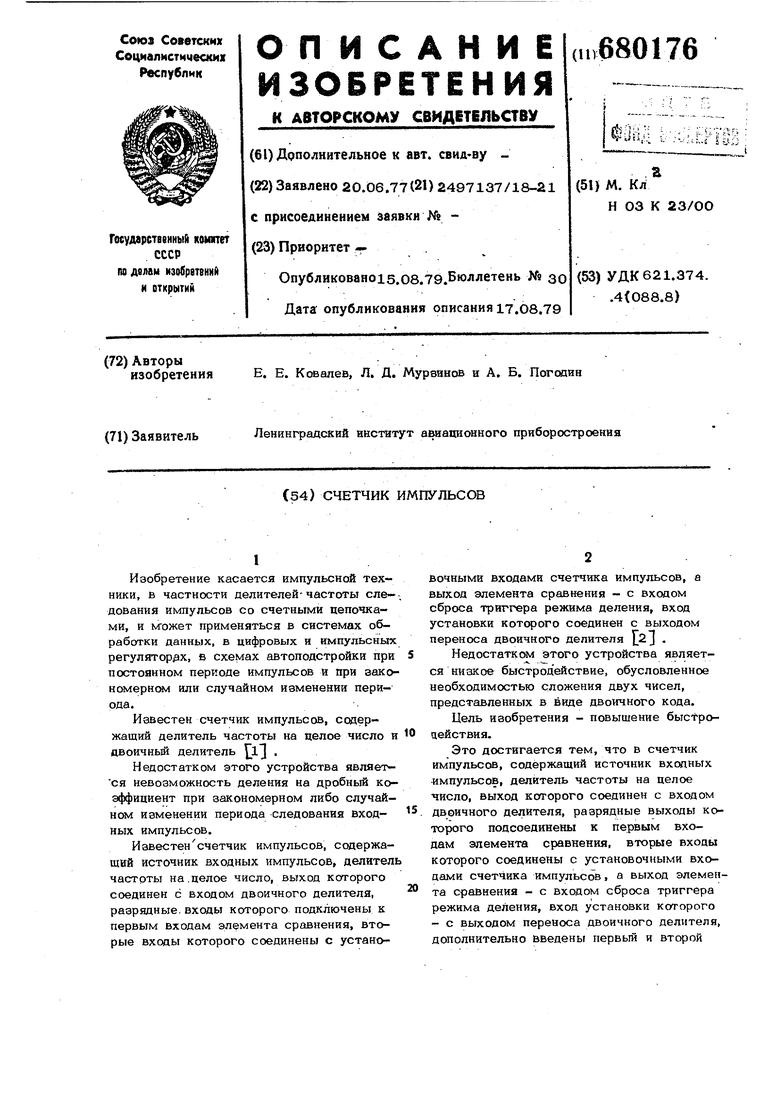

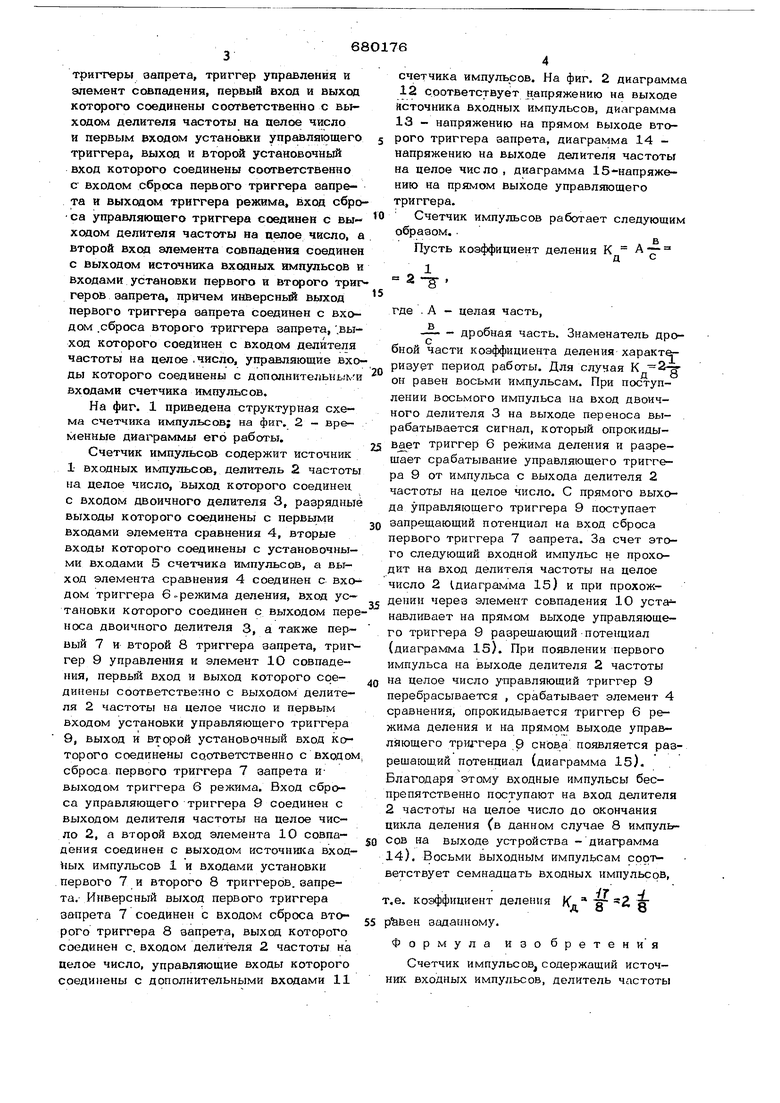

Изобретение касается импульсной техники, в частности делителей-частоты еле- дования импульсов со счетными цепочками, и м-ожет применяться в системах обработки данных, в цифровых и импульсных регулятордх, в схемах автоподстройки при постоянном периоде импульсов и при зако номернся или случайном изменении периода.. Известен счетчик импульсов, содержащий делитель частоты на целое число и двоичный делитель 1 Недостатком этого устройства является невозможность деления на дробньй коэффициент при закономерном либо случайном изменении периода следования входных импульсов. Известенсчетчик импульсов, содержащий источник входных импульсов, делител частоты на,целое число, выход которого соединен с входом двоичного делителя, разр5шные. входы которого подключены к первым входам элемента сравнения, вторые входы которого соединены с установочными входами счетчика импульсов, а выход элемента сравнения с входом сброса триггера режима деления, вход установки которого соединен с выходом переноса двоичного делителя 2 . Недостатком этого устройства является низкое быстродействие, обусловленное необходимостью сложения двух чисел, представленных в виде двоичного кода. Цель изобретения - повышение быстродействия. Это достигается тем, что в счетчик импульсов, содержащий источник входных импульсов, делитель частоты на целое число, выход которого соединен с входом двоичного делителя, разрядные выходы которого подсоединены к первым входам элемента сравнения, вторые входы которого соединены с установочными входами счетчика импульсеэв, а выход элемента сравнения - с входом сброса триггера режима деления, вход установки которого - с выходом переноса двоичного делителя, дополнительно введены первый и второй 3 триггеры запрета, триггер управления и элемент совпадения, первый вход и выход которого соединены соответственно с вььходом делителя частоты на целое число и первым рходом установки управляющего5 триггера, выход и второй установочный вход которого соединены соответственно с Входом сброса первого триггера аапре- та и выходом триггера режима, вход сброса управляющего триггера соединен с выходом делителя частоты на целое число, а второй вход элемента совпадения соединен с выходом источника входных импульсов H входами установки первого и второго триггеров запрета, причем инверсный выход первого триггера запрета соединен с вкодом .сброса второго триггера запрета,.выход которого соединен с входом делителя частоты на целое .число, управляющие входы которого соединены с дополнительнык/и входами счетчика импульсов. На фиг. 1 приведена структурная схема счетчика импульсов; на фиг. 2 - временные диаграммы его работы. Счетчик импульсов содержит источник 1 входных импульсов, делитель 2 частоты на целое число, выход которого соединен с входом двоичного делителя 3, разрядные выходы которого соединены с первыми входами элемента сравнения 4, вторые входы которого соединены с установочными Входами 5 счетчика импульсов, а вы- ход элемента сравнения 4 соединен с входом триггера 6 режима деления, вход установки которого соединен с выходом переноса двоичного делителя 3, а также вый 7 и второй 8 триггера запрета, триггер 9 управления и элемент 10 совпадения, первьй вход и выход которого соединены соответственно с выходом делителя 2 частоты на целое число и первым входом установки управляющего триггера 9, выход и второй установочный вход которого соединены соответственно с входом сброса первого триггера 7 запрета ивыходом триггера 6 режима. Вход сброса управляющего триггера 9 соединен с выходом делителя частоты на целое число 2, а второй вход элемента 10 совпадения соединен с выходом источнш а вход 1ых импульсов 1 и входами установки первого 7 и второго 8 триггеров, запрета. Инверсный выход первого триггера запрета 7 соединен с входом сброса ВТО-gs рого триггера 8 запрета, выход которого соединен с. входом делителя 2 частоты на целое число, управляющие входы которого соединены с дополнительными входами 11 68О1 76 4 счетчика импульсов. На фиг. 2 диаграмма 12 соответствует напряжению на выходе источника входных импульсов, диаграмма 13 - напряжению на прямом выходе второго триггера запрета, диаграмма 14 напряжению на выходе делителя частоты на целое число, диаграмма 15-напряжению на прямом выходе управляющего триггера. Счетчик импульсов работает следующим образом. Пусть коэффициент деления K I S ® - Целая часть, дробная часть. Знаменатель дробной части коэффициента деления характ&р зу т период работы. Для случая К - 24он равен восьми импульсам. При поступлении восьмого импульса на вход двоич го делителя 3 на выходе переноса вырабатывается сигнал, который опрокиды триггер б режима деления и разрещ срабатывание управляющего триггерд 9 от импульса с выхода делителя 2 частоты на целое число. С прямого выхода управляющего триггера 9 поступает запрещающий потенциал на вход сброса первого триггера 7 запрета. За счет эторд следующий входной импульс не проходит на вход делителя частоты на целое число 2 диаграмма 15) и при прохождед„„ .jgpes элемент совпадения 10 уста навливает на прямом выходе управляюще-ро триггера 9 разрещающий потенциал (диаграмма 15). При появлении первого импульса на выходе делителя 2 частоты на целое число управляющий триггер 9 перебрасывается , срабатывает элемент 4 сравнения, опрокидывается триггер 6 режима деления и на прямом выходе управляющего Tpiirrepa 9 снова появляется разрещающийпотенциал (диаграмма 15). Благодаря этому входные импульсы беспрепятственно поступают на вход делителя g частоты на целое число до окончания деления (в данном случае 8 импуль ов на выходе устройства - диаграмма 14). Восьми выходным импульсам срот- ветствует семнадцать входных импульсов, .е. коэффициент деления К g заданному. Формула изобретения Счетчик импульсов, содержащий источник входных импульсов, делитель частоты на целое число,выход которого соединен с входом двоичного делителя, разрядные выходы которого соединены с первыми входами элемента сравнения, вторые входы которого - с установочными входами счетчика импульсов, а выход элемента сравнения - с входом сброса триггера ре-жима деления, вход установки которого соединен с выходом переноса двоичного делителя, отлич ающийся тем, что, с целью повышения быстродействия, в него дополнительно введены первый и Ьторой триггера запрета, триггер управлейия и элемент совпадения, первый вход и выход которого соединены соответственно с выходом делителя частоты на целое чис ло и первым входом установки управляющего триггера, выход и второй установочный вход котфого соединены соответс-гвенно с входом сброса первого триггера запрета и выходом триггера режима, вход сброса управляющего триггера соединен с выходом делителя частоты на пелое число, а второй вход элемента совпадения соединен с выходом источника входных импуль сов и входами установки первого и второго триггерЪв запрета, причем инверсный выход первого триггера запрета соединен с входом сброса второго триггера запрета, выход которого соединен с входом делителя частоты на целое число, управляющие входы которого соединены с дополнительными входами счетчика импульсов. Источники информации, принятые .во внимание при jэкспертизе 1.Патент США № 3614631, кл. 307.88.,5,1969, 2,Авторское свидетельство СССР № 512580, кл. Н 03 К 23/ОО, 1974.

| название | год | авторы | номер документа |

|---|---|---|---|

| Управляемый делитель частоты следования импульсов | 1989 |

|

SU1709515A1 |

| Преобразователь двоичного кода в унитарный код | 1982 |

|

SU1049897A1 |

| Делитель частоты с переменным коэффициентом деления | 1990 |

|

SU1812636A1 |

| Устройство для обмена информацией | 1986 |

|

SU1363228A1 |

| Цифровой синтезатор частот | 1991 |

|

SU1803977A1 |

| Устройство для задержки импульсов с программным управлением | 1979 |

|

SU866722A1 |

| Делитель частоты следованияиМпульСОВ | 1979 |

|

SU839066A1 |

| АДАПТИВНЫЙ ИЗМЕРИТЕЛЬ ВРЕМЕННЫХ ИНТЕРВАЛОВ | 1991 |

|

RU2043648C1 |

| Устройство для управления шаговым двигателем | 1977 |

|

SU663058A1 |

| Цифровой следящий частотомер | 1980 |

|

SU892335A1 |

Puz.j

Jtti

evj

-IS

oi

-:жз

Й

т

Авторы

Даты

1979-08-15—Публикация

1977-06-20—Подача