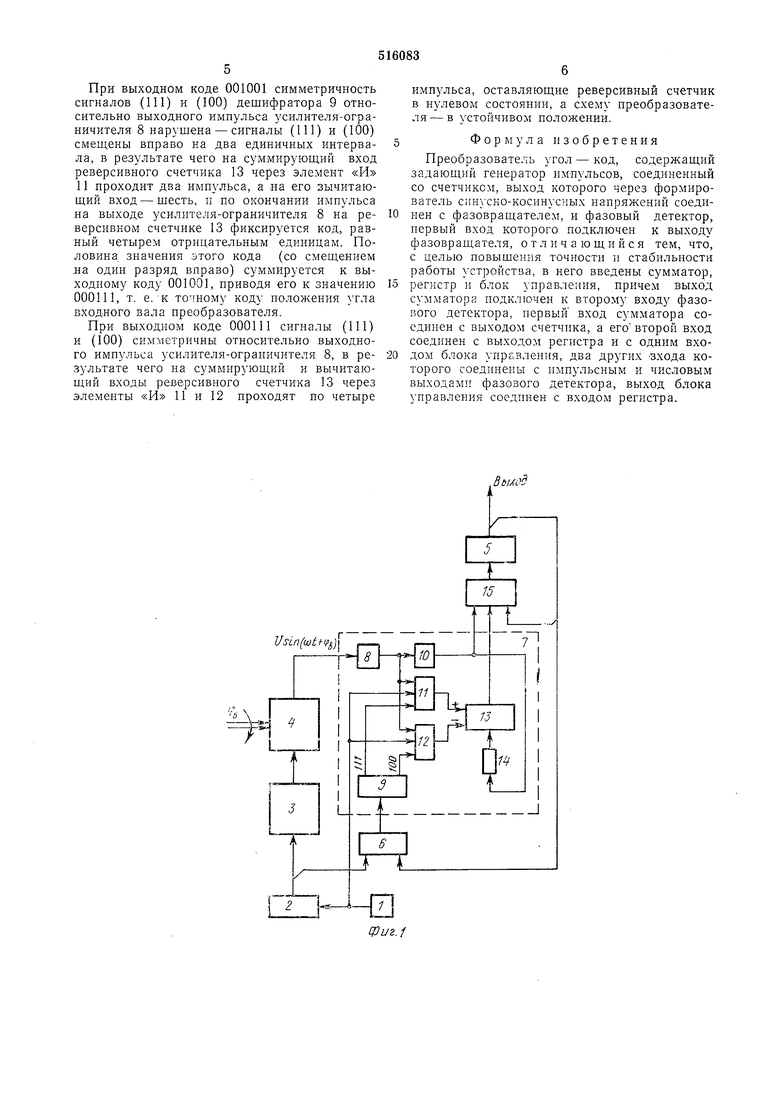

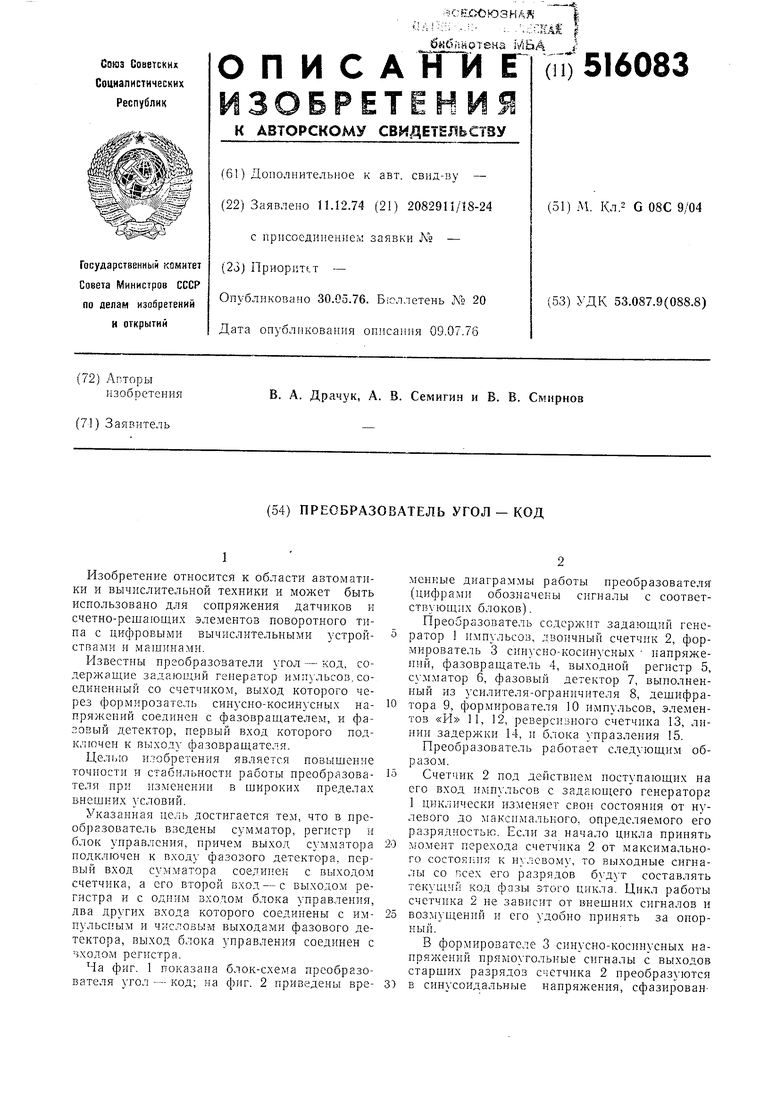

ные с циклом счетчика так, что текущий код фазы счетчика 2 является кодом текущей фазы этих напряжений. Эти напряжения используются для запитки фазовращателя 4 по статорным обмоткам..

С одной из роторных обмоток фазовращателя 4 снимается синусоидальное напряжение, смещенное по фазе относительно сигналов опорного цикла преобразователя, а следовательно и напряжений запптки фазовращателя 4 на величину фв текущего разворота вала фазовращателя 4, т. е. входного вала преобразователя.

Преобразование выходного кода, снимаемого с выходного регистра 5, з сдвиг фазы прямоугольиых сигналов осуществляется в комбинационном сумматоре 6 путем непрерывного суммирования к коду текущей фазы опорного цикла, формируемого счетчиком 2, для чего эти коды подаются на входы сумматора. При этом к монотонно и циклически изменяющимся кодам непрерывно суммируется некоторое постоянное число, результатирующие коды без учета самого старшего разряда имеют те же монотонность и цикличность, что и исходные коды, но их цикл смещен на величину суммируемого числа, цикл выходных кодов сумматора 6 при этом переменный.

Сравнение фазы переменного цикла с фазой выходного напрял ения фазовращателя 2 осуществляется в фазовом детекторе 7 дискретно-цифровым способом. Для этого синусоидальное напряжение с выхода фазовращателя 4 путем двухстороннего ограничения и усиления в усилителе-ограничителе 8 фазового детектора 7 преобразуется в прямоугольное, верхний и нижний уровни которого соответствуют единичному и нулевому уровням сигналов логических элементов, используемых в фазовом детекторе 7, при этом уровни ограничения входного напряжения выбраны так, что длительность выходных сигналов на единичном уровне несколько превышает половину периода пх следования.

Прямоугольные сигналы с выхода усилителя-ограничителя 8 подаются на первые входы элементов «И И, 12. На вторые их входы поступают импульсы с задающего генератора 1, а на их третьи входы - прямоугольные сигналы (111) и (100) переменного цикла, формируемые путем расшифровки дешифратором 9 определенных состояний трех старших разрядов сумматора 6.

На время совпадения сигналов с выхода усилителя-ограничителя 8 с сигналами (111) и (100) переменного цикла импульсы генератора 1 проходят соот ветствующие элементы «И И, 12 и поступают на суммирующий (с элементов «И 11) и вычитающий (с элементов «И 12) входы реверсивного счетчика 13.

Расшифрованные дешифратором 9 состояния старших разрядов сумматора 6 и начальная выставка положения входного вала преобразователя подобраны так, что при точном соответствии выходного кода преобразователя положению его входного зала 16 сигналы дешифратора (111) и (100) строго симметричны относительно импульсов с выхода усилителя-ограничителя 8, при этом число импульсов на суммирующем входе реверсивного счетчика 13 равно числу импульсов на его вычитающем входе, и после окончания выходного имнульса усилителя-ограничителя 8 реверсивный счетчик 13 будет находиться в нулевом состоянии.

Такое состояние преобразователя -стойчивое, а его выходной код является кодом положения его входного вала. Если теперь входной вал преобразователя сместить в ту или иную сторону на некоторый угол, то фаза выходного напряжения фазовращателя 4 изменится на эту же величину, выходные импульсы усилителя-ограпичитсля 8 так же смещаются в соответствующую сторону и нарушается их симметрия относительно сигналов (111) и (100) дешифратора 9. При этом в зависимости от величины угла смещения входного вала и его направления число импульсов на одном из входов реверсивного счетчика 13 увеличивается, а на другом - уменьшается, и после окончания выходного импульса усилителя-ограничителя на реверсивном счетчике 13 будет зафиксировано число, величина которого пропорциональна величине угла смещения входного вала, а знак будет совпадать с направлением этого смещения.

С окончанием выходного импульса усилителя-ограничителя в формирователе 10 импульсов вырабатывается импульс, по которому посредством блока управления 15 по состоянию реверсивного счетчика 13 осуществляется корректировка кода выходного регистра 5, т. е. выходного кода преобразователя, а через линию 14 задержки - сброс реверсивного счетчика 13.

Одним из вариантов построения блока управления 15 может служить сумматор, в котором к выходному коду преобразователя суммируется (с учетом знака) код состояния 1)еверсивного счетчика 13, пропорциональный углу смещения входного вала преобразователя. Очевидно, что после корректировки кода выходного регистра 5 преобразователь приходит к своему устойчивому новому состоянию, причем при использовании в качестве блока управления 15 сумматора этот переход осуществляется в наиболее короткое время.

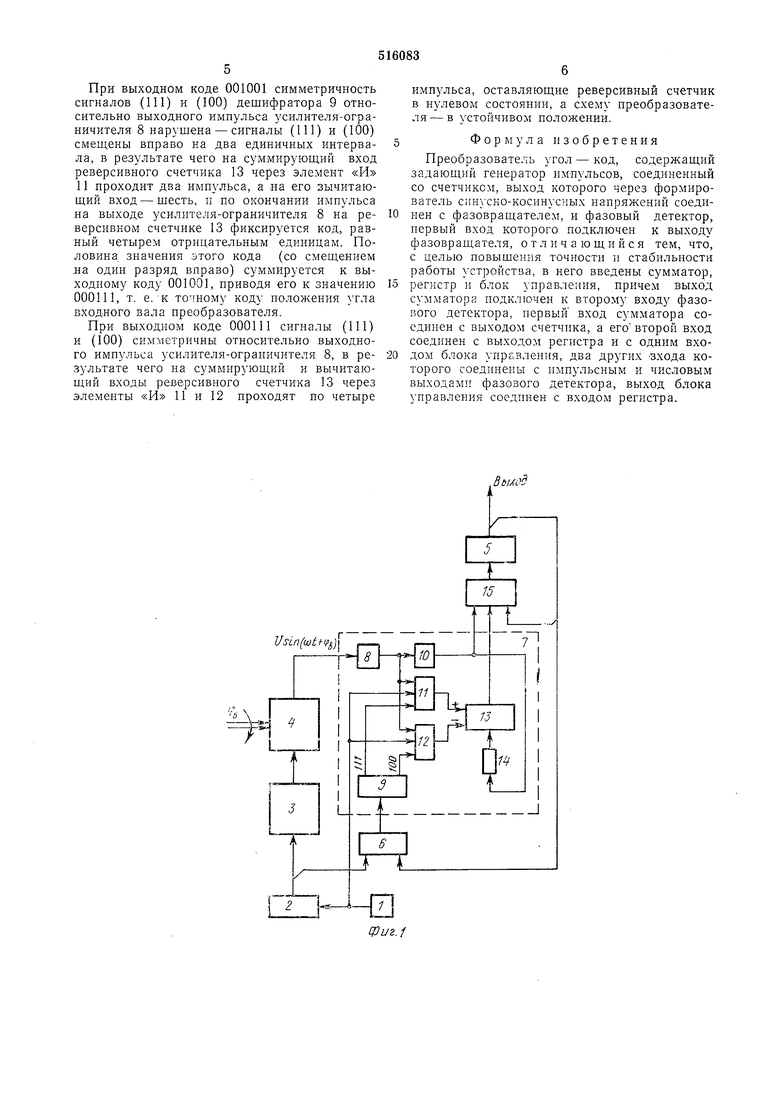

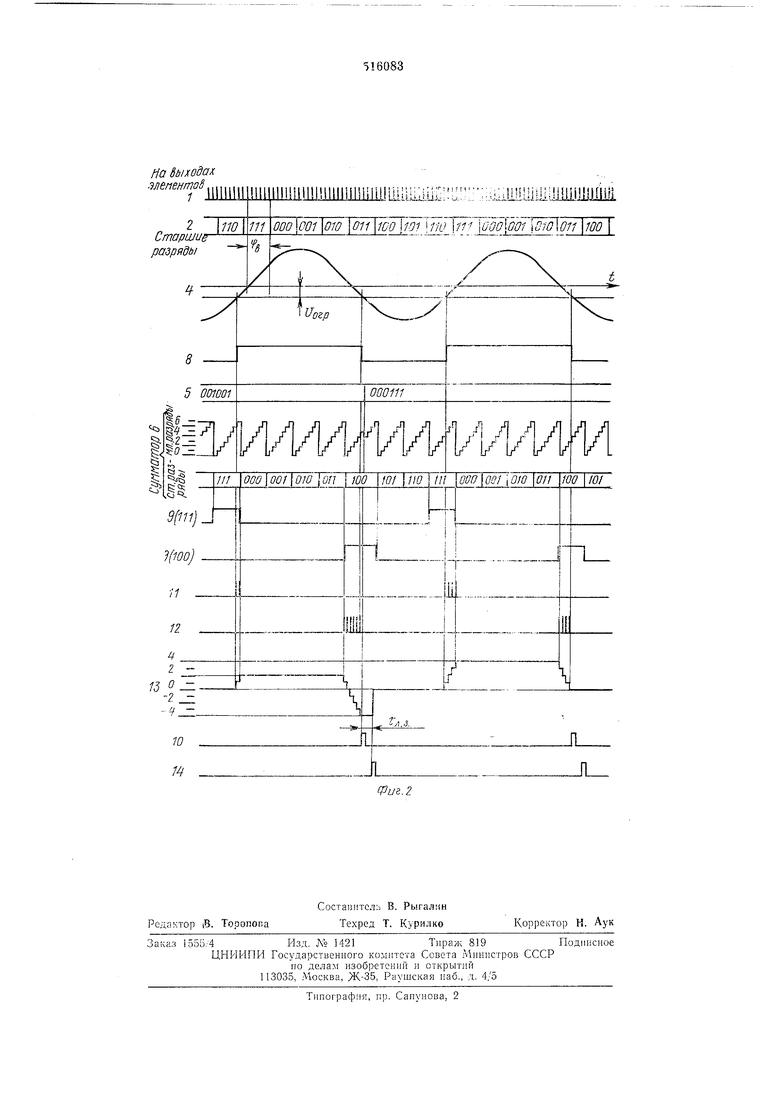

На диаграммах (см. фиг. 2) выходной код преобразователя представлен шестиразрядным, выходной вал - неподвижным и повернутым на положительную величину, равную J11 единицам, т. е. 7/64 долям угла полного оборота, а выходной код равным 001001 (ле1зая часть диаграмм) и 000111 (правая часть диаграмм). По диаграммам легко проследить, как выходной код преобразователя 001001, превышающий на две единицы код 000111 истинного положения вала, приводится к этому коду за один цикл работы преобразователя.

При выходном коде 001001 симметричность сигналов (111) и (100) дешифратора 9 относительно выходного импульса усилителя-ограничителя 8 нарушена - сигналы (111) и (100) смеш.ены вправо на два единичных интервала, в результате чего на суммирующий вход реверсивного счетчика 13 через элемент «И 11 нроходит два импульса, а на его зычитаюший вход - шесть, п по окончании импульса на выходе усилителя-ограничителя 8 на реверсивном счетчике 13 фиксируется код, равный четырем отрицательным единицам. Половина значения этого кода (со смеш,ением на один разряд вправо) суммируется к выходному коду 001001, приводя его к значению 000111, т. е. к точному коду положения угла входного вала преобразователя.

При выходном коде 000111 сигналы (111) и (100) симметричны относительно выходного импульса усилителя-ограничителя 8, в результате чего на суммирующий и вычитающий входы реверсивного счетчика 13 через элементы «И И и 12 проходят по четыре

импульса, оставляющие реверсивный счетчик в нулевом состоянии, а схему преобразователя - в устойчивом положении.

Фор мул а изобретения

Преобразователь угол - код, содержащий задающий генератор импульсов, соединенный со счетчиком, выход которого через формирователь синусно-косинусных напряжений соединей с фазовращателем, и фазовый детектор, первый вход которого подключен к выходу фазовращателя, отличающийся тем, что, с целью повышения точности п стабильности работы устройства, в него введены сумматор,

регистр и блок управления, причем выход сумматора подключен к второму входу фазового детектора, первый вход сумматора соединен с выходом счетчика, а его второй вход соединен с выходом регистра и с одним входом блока управления, два других зхода которого соединены с импульсным и числовым выходами фазового детектора, выход блока управления соединен с входом регистра.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь перемещений в код | 1983 |

|

SU1111188A1 |

| Преобразователь угла поворота вала в код | 1975 |

|

SU526934A1 |

| Преобразователь "угол-код | 1974 |

|

SU519749A1 |

| Устройство выбора каналов для разнесенного приема | 1988 |

|

SU1525925A1 |

| Устройство для измерения сдвига фаз | 1991 |

|

SU1827644A1 |

| Преобразователь угла поворота вала в код | 1982 |

|

SU1043703A1 |

| Двухотсчетный преобразователь угла поворота вала в код | 1977 |

|

SU734776A1 |

| Цифровой фазометр | 1982 |

|

SU1061062A1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ФАЗЫ РАДИОСИГНАЛА | 1991 |

|

RU2048676C1 |

| Устройство для измерения частоты частотно-модулированного телевизионного сигнала | 1983 |

|

SU1223157A1 |

UsLn(wt-tf)

ВыАО.

На бы ходах. элепентаВ 1 . Старшиеразряды

5 001001

V

I 100 I lot 1110

///

.a.iii:: :i: ::: :.;.L;MUiiuyjJiiJJMiiii

000111

VWbWW A

ОП

wo I/O/

///

1T-

Jt

101 WQ

Авторы

Даты

1976-05-30—Публикация

1974-12-11—Подача