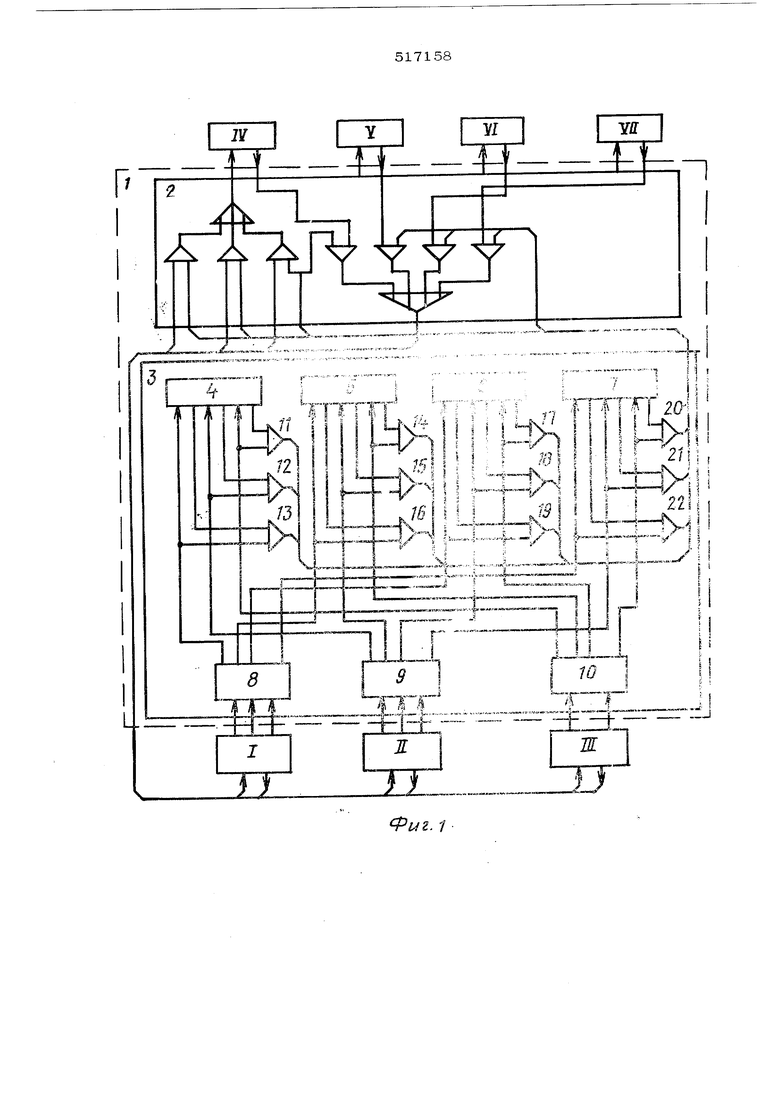

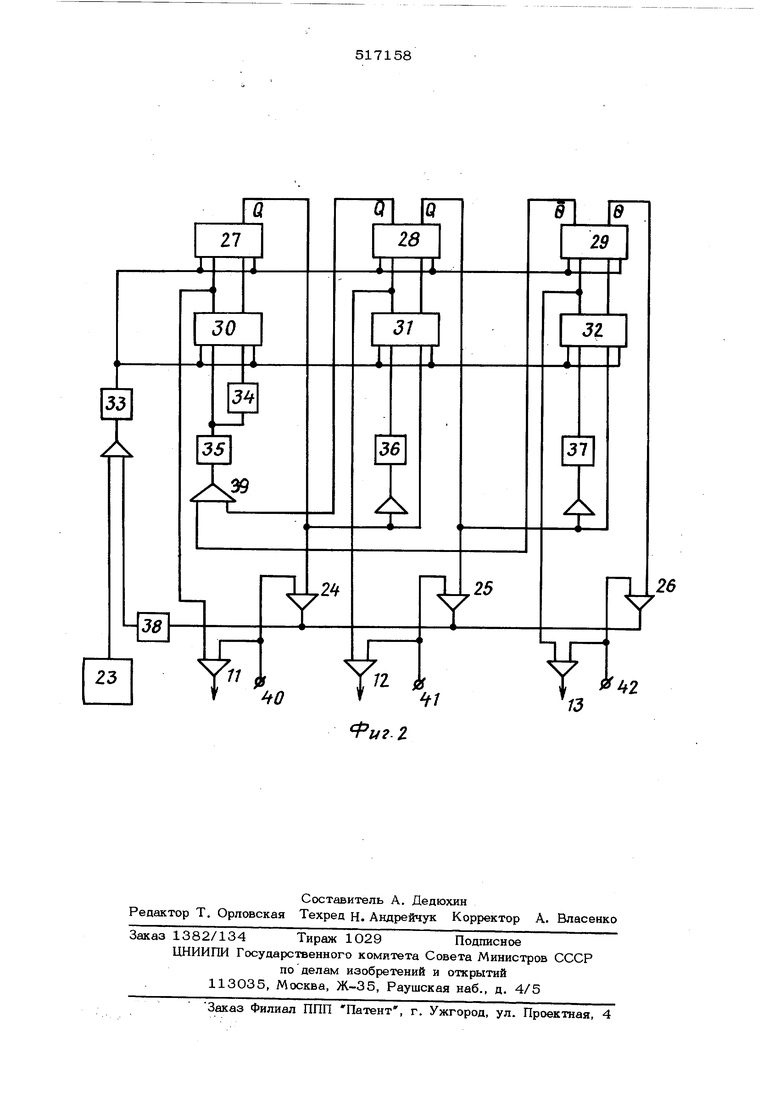

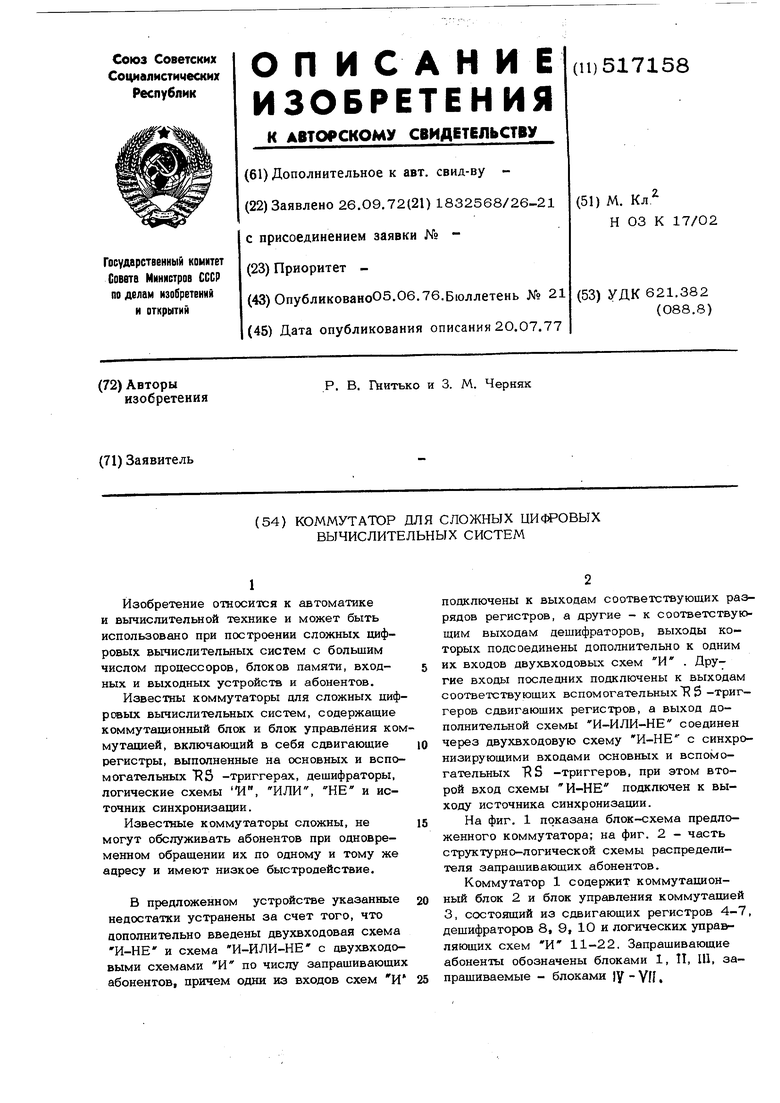

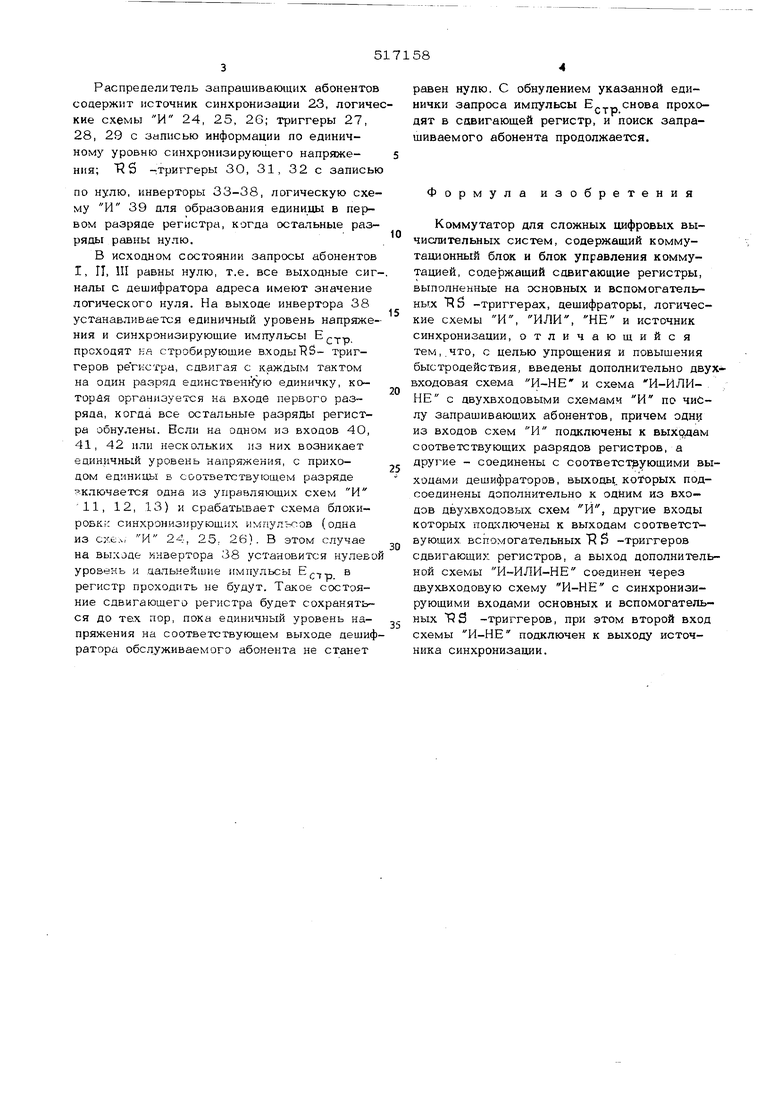

Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении сложных цифровых вычислительных систем с большим числом процессоров, блоков памяти, входных и выходных устройств и абонентов. Известны коммутаторы для сложных циф рсчзых вычислительных систем, содержащие коммутационный блок и блок управления ком мутацией, включающий в себя сдвигающие регистры, выполненные на основных и вспомогательных TRS -триггерах, дешифраторы, логические схемы И, ИЛИ, НЕ и источник синхронизации. Известные коммутаторы сложны, не могут обслуживать абонентов при одновременном обращении их по одному и тому же адресу и имеют низкое быстродействие. В предложенном устройстве указанные недостатки устранены за счет того, что дополнительно введены двухвходовая схема И-НЕ и схема И-ИЛИ-НЕ с двухвходовыми схемами И по числу запрашивающих абонентов, причем одни из входов схем И подключены к выходам соответствующих разрядов регистров, а другие - к соответствующим выходам дешифраторов, выходы которых подсоединены дополнительно к одним их входов двухвходовых схем И . Другие входы последних подключены к выходам соответствующих вспомогательных Т 5 -триггеров сдвигающих регистров, а выход дополнительной схемы И-ИЛИ-НЕ соединен через двухвходовую схему И-НЕ с синхронизирующими входами основных и вспомогательных RS -триггеров, при этом второй вход схемы И-НЕ подключен к выходу источника синхронизации. На фиг. 1 показана блок-схема предложенного коммутатора; на фиг. 2 - часть структурно-логической схемы распределителя запрашивающих абонентов. Коммутатор 1 содержит коммутационный блок 2 и блок управления коммутацией 3, состоящий из сдвигающих регистров 4-7, дешифраторов 8, 9, 10 и логических управляющих схем И 11-22. Запращивающие абоненты обозначены блоками 1, II, III, запрашиваемые - блоками )у - Yff, Распрепелитепь запрашивающих абонентов содержит источник синхронизации 23, логиче кие схемы И 24, 25, 26; триггеры 27, 28, 29 с записью информации по единичному уровню синхронизирующего напряжения; R S -триггеры 30, 31, 32 с запись по нулю, инверторы 33-38, логическую схе му И 39 для образования единицы в первом разряде регистра, когда остальные разряг1ы равны нулю. В исходном состоянии запросы абонентов I, Г1, Ш равны нулю, т.е. все выходные сиг налы с дешифратора адреса имеют значение логического нуля. На выходе инвертора 38 устанавливается единичный уровень напряже ния и синхронизирующие импульсы Е преходят на стробируюшие входы Т S триггеров регкстра, сдвигая с каждым тактом на один разряд еакнственную единичку, которая организуется на входе первого разряда, когда все остальные разряды регистра обнулены. Если на одном из входов 40, 41, 42 или нескольких из них возникает ециничный уровень напряжения, с приходом единицы Е соответствующем разряде включается одна из управляющих схем И 11, 12, 13) и срабатывает схема блокирОБК,;: синхронизирующих импульсов {одна из схел, И 24, 25: 26). В этом случае на выходе инвертора 38 установится нулево уровень и дальней иие импульсы Е регистр проходить не будут. Такое состояние сдвигающего регистра будет сохраняться до тех пор, пока единичный уровень напряжения на соответствующем выходе дешиф ратора обслуживаемого абонента не станет равен нулю. С обнулением указанной единички запроса импульсы Е.. снова проходят в сдвигающей регистр, и поиск запрашиваемого абонента продолжается. Формула изобретения Коммутатор для сложных цифровых вычислительных систем, содержащий коммутационный блок и блок управления коммутацией, соде5зжащий сдвигающие регистры, выполненные на основных и вспомогательны.х TRS -триггерах, дещифраторы, логические схемы И, ИЛИ, НЕ и источник синхронизации, отличающийся тем,.что, с целью упрощения и повышения быстродействия, введены дополнительно двух входовая схема И-НЕ и схема И-ИЛИ- . НЕ с двухвхоцовыми схемами И по числу запрашиваюш.их абонентов, причем одни из входов схем И подключены к соответствующих разрядов регистров, а другие - соединены с соответствующими выходами дешифраторов, выходьх, которых подсоединены дополнительно к одним из входов двухвходозых схем И, другие входы которых подключены к выходам соответствующих, вспомогательных Т S -триггеров сдвигающих регистров, а выход дополнительной схемы И-ИЛИ-НЕ соединен через двухвходовую схему И-НЕ с синхронизирующими входами основных и вспомогательных -триггеров, при этом второй вход схемы И-НЕ подключен к выходу источника синхронизации.

иг. 1

и.г

| название | год | авторы | номер документа |

|---|---|---|---|

| МНОГОКАНАЛЬНАЯ СИСТЕМА ДЛЯ СЕЙСМИЧЕСКИХ ИССЛЕДОВАНИЙ | 2020 |

|

RU2722462C1 |

| Программное устройство для фиксации и документирования времени | 1989 |

|

SU1677691A1 |

| Устройство для формирования синхроимпульсов | 1978 |

|

SU767747A1 |

| МОДУЛЬНАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2011 |

|

RU2474868C1 |

| Коммутационное устройство | 1990 |

|

SU1730635A1 |

| МНОГОКАНАЛЬНАЯ СИСТЕМА ДЛЯ ПРЕДУПРЕЖДЕНИЯ О ВОЗНИКНОВЕНИИ СЕЙСМИЧЕСКИХ ТОЛЧКОВ И ЦУНАМИ | 2008 |

|

RU2363963C1 |

| Коммутатор | 1977 |

|

SU663104A2 |

| Многодвигательный электропривод переменного тока | 1985 |

|

SU1307521A1 |

| Устройство для ввода информации | 1983 |

|

SU1151942A1 |

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 2005 |

|

RU2296365C1 |

Авторы

Даты

1976-06-05—Публикация

1972-09-26—Подача