элементов ИЛИ 6, первый, второй, третий и четвертый дешифраторы 7- 10, первый, второй и третий мультиплексоры 11-13, схему

14сравнения, первый и второй элементы И

15и 16, элемент НЕ 17, блок 18 управления. Устройство имеет группу информационных

входов 19, группу информационных выхо-

дов 20, адресный вход 21, первый и второй информационные входы 22 и 23, вход 24 адреса отказавшего абонента, вход 25 адреса резервного абонента, вход 26 выбора режима, тактовый вход 27, установочный вход 28, вход 29 пуска и выход 30 готовности. 2 з,

| название | год | авторы | номер документа |

|---|---|---|---|

| Коммутационное устройство | 1988 |

|

SU1539790A1 |

| Коммутационное устройство | 1989 |

|

SU1672464A1 |

| Коммутационное устройство | 1984 |

|

SU1246109A1 |

| Коммутационное устройство | 1989 |

|

SU1645963A1 |

| Устройство для обмена данными между электронно-вычислительной машиной и абонентами | 1985 |

|

SU1277125A1 |

| Коммутационное устройство | 1989 |

|

SU1621041A1 |

| Система коммутации | 1985 |

|

SU1317447A1 |

| Устройство для коммутации дискретных сообщений | 1986 |

|

SU1319302A1 |

| Система коммутации | 1985 |

|

SU1317448A1 |

| Распределенная система для программного управления технологическими процессами | 1990 |

|

SU1797096A1 |

Изобретение относится к вычислительной технике и технике связи. Целью изобретения является повышение скорости реконфигурации связей при выходе из строя абонентов коммутационной сети. Устройство, содержащее матричный коммутатор 1, который включает в себя N блоков 2 коммутации (N - количество абонентов на выходе матричного коммутатора), причем каждый блок 2 коммутации содержит М коммутаторов 3 (М - количество абонентов на входе матричного коммутатора), N блоков 4 модификации адреса, N блоков 5 адреса, группу (Л С vi СА о Os GO СП

Изобретение относится к вычислительной технике и может быть использовано при разработке и конструировании коммутационных систем.

Известно коммутационное устройство, содержащее первый и второй дешифраторы, блок микропрограммного управления, матричный коммутатор, два счетчика и три регистра и обеспечивающее высокую скорость передачи информации по коммутируемым каналам связи.

Известно также коммутационное устройство, содержащее матричный коммутатор, М дешифраторов, дополнительный дешифратор, М блоков управления настройкой и элемент И и обеспечивающее высокую скорость настройки связей матричного коммутатора.

Недостатком этих устройств является невысокая скорость реконфигурации структуры связей при отказах коммутируемых ресурсов.

Наиболее близким к предлагаемому является коммутационное устройство, содержащее матричный коммутатор, группу дешифраторов, N блоков памяти, группу элементов И, группу элементов ИЛИ, первый и второй элементы И, элемент ИЛИ, первый и второй дешифраторы, мультиплексор, элемент НЕ, блок управления, причем информационные входы группы и информационные входы матричного коммутатора соединены с информационными группами входов и выходов устройства соответственно, 1-й вход (где i 1 ,N - количество информационных входов группы) группы тактовых входов матричного коммутатора подключен к выходу 1-го элемента И (где i 1,N) группы, первые входы группы элементов И объединены и подключены к выходу первого элемента И, вторые входы группы элементов И соединены с первыми выходами соответствующих блоков памяти, вторые выходы которых подключены к соответствующим адресным входам первой группы матричного коммутатора, управляющие входы группы которого соединены с выходами дешифраторов группы, входы которых подключены соответственно к третьим выходам блоков памяти, входы адреса программы которых объединены и подключены к адресному входу устройства, адресные входы

блоков па1«яти объединены и подключены к выходу мультиплексора, первый информационный вход которого объединен с адресными входами второй группы матричного коммутатора и подключен к первому выходу

блока управления, второй информационный вход мультиплексора подключен к информационному входу первого дешифратора и входу второго адреса устройства, вход первого адреса устройства соединен с информационными входами первой группы блоков памяти, информационные входы второй группы которых подключены к выходу элемента НЕ, соединенного входом с первым входом второго элемента И, первым

входом элемента ИЛИ и входом сброса блока управления, подключенного к первому выходу второго дешифратора, вход которого соединен с входом режима устройства, второй выход второго дешифратора соединен с управляющим входом мультиплексора и вторым входом элемента ИЛИ и подключен к входу управления записью блока управления, третий выход второго дешифратора соединен с управляющим входом блока управления, первым входом первого элемента И и подключен к первым входам i-x элементов ИЛИ группы, второй вход первого элемента И соединен с управляющим входом первого дешифратора, вторым входом второго элемента И и подключен к второму выходу блока управления, третий выход которого соединен с выходом готовности устройства, установочный вход блока управления подключен к установечному входу устройства, тактовый вход которого соединен с тактовым входом блока управления, вход пуска блока управления подключен к входу пуска устройства, выход второго элемента И соединен с вторыми

входами i-x элементов ИЛИ группы, третьи входы которых подключены к соответствующим выходам первого дешифратора, а выходы элементов ИЛИ группы соединены с

первыми управляющими входами блоков памяти, вторые управляющие входы которых объединены и подключены к выходу элемента ИЛИ, кроме того, матричный коммутатор состоит из N блоков коммутации (N - количество информационных выходов группы матричного коммутатора), а каждый блок коммутации содержит М коммутаторов (М - количество информационных входов группы матричного коммутатора), причем j-e информационные входы (где j 1,М) группы матричного коммутатора подключены к j-м информационным входам (где j 1,M) группы блоков коммутации матричного коммутатора и соединены с информационными входами коммутаторов блоков коммутации матричного коммутатора, выходы коммутаторов i-ro блока коммутации объединены и подключены к информационным выходам I- го блока коммутации и соединены с i-м информационным выходом (где i 1,N) группы матричного коммутатора, адресные входы первой группы которого подключены к первым адресным входам всех блоков коммутации матричного коммутатора и соединены с первыми адресными входами всех коммутаторов каждого блока коммутации матричного коммутатора, вторые адресные входы всех коммутаторов подключены к вторым адресным входам каждого блока коммутации и соединены с адресными входами второй группы матричного коммутатора, тактовые входы группы которого подключены к соответствующим первым управляющим входам всех блоков коммутации матричного коммутатора и соединены с первыми управляющими входами всех коммутаторов каждого блока коммутации матричного коммутатора, вторые управляющие входы всех коммутаторов подключены к соответствующим вторым управляющим входам каждого блока коммутации матричного коммутатора и соединены с управляющими входами группы матричного коммутатора.

Недостатком прототипа является невысокая скорость реконфигураци связей матричного коммутатора при вы, оде из строя абонентов.

Цель изобретения - повышение скорости реконфигурации связей при выходе из строя абонентов.

Поставленная цель достигается тем, что в коммутационное устройство, содержащее матричный коммутатор, который включаете себя N блоков коммутации (N - количество абонентов на выходе матричного коммутатора), каждый блок коммутации содержит М коммутаторов (М - количество абонентов на входе матричного коммутатора), N блоков памяти, группу элементов ИЛИ, первый и

второй дешифраторы, первый мультиплексор, элемент НЕ, первый элемент И, блок управления, i-й (f 1,М) информационный вход группы и j-й О 1.N) информационный

выход группы матричного коммутатора соединены соответственно с i-м информационным входом группы и j-м информационным выходом группы устройства, вход первого дешифратора подключен к входу выбора ре0 жима устройства, первый выход первого дешифратора соединен с первым входом выбора режима блока управления, первым входом первого элемента И и входом элемента НЕ, выход элемента НЕ подключен к

5 первым информационным входам блоков памяти, вторые информационные входы которых соединены с первым информационным входом устройства, адресный вход которого подключен к первым адресным

0 входам блоков памяти, входы разрешения каждого j-ro блока памяти (j 1,N) соединены с выходами j-ro элемента ИЛИ группы, первые входы элементов ИЛИ группы объединены и подключены к выходу первого эле5 мента И, второй вход которого подключен к первому выходу блока управления и соединен с входом разрешения второго дешифратора, информационный вход которого соединен со старшими разрядами второго

0 информационного входа устройства, младшие разряды второго информационного входа устройства соединены с первым информационным входом первого мультиплексора, соединенного управляющим

5 входом с вторым входом выбора режима блока управления и вторым выходом первого дешифратора, третий выход которого подключен к третьему входу выбора режима блока упргзления и вторым входам элемен0 тов ИЛИ группы, третий вход каждого j-ro элемента ИЛИ группы соединен с j-м выходом второго дешифратора, тактовый вход блока управления подключен к тактовому входу устройства, установочный вход кото5 рого соединен с установочным входом блока управления, подключенного входом пуска к входу пуска устройства, выход готовности которого соединен с выходом готовности блока управления, подключенного

0 своим вторым выходом к второму информационному входу первого мультиплексора, i-e информационные входы (i 1,М) группы матричного коммутатора подключены к i-м информационным входам группы всех блоков

5 коммутации матричного коммутатора и соединены с информационными входами коммутаторов всех блоков коммутации матричного коммутатора, выходы коммутаторов j-ro (j 1,N) блока коммутации объединены и подключены к информациейному выходу j-ro блока коммутации и соединены с j-м информационным выходом груп- пы матричного коммутатора, первый управляющий вход которого подключен к первым управляющим входам всех блоков коммутации матричного коммутатора и соединен с первыми управляющими входами всех коммутаторов каждого j-ro блока коммутации матричного коммутатора, вторые управляющие входы всех коммутаторов каждого j-ro блока коммутации объединены и подключены к второму управляющему входу j-ro блока коммутации и j-му управляюще- му входу первой группы матричного коммутатора, j-й тактовый вход группы которого подключен к третьему управляющему входу каждого j-ro блока коммутации матричного коммутатора и соединен с всеми третьими управляющими входами коммутаторов j-ro блока коммутации, четвертые уп- равляющие входы всех коммутаторов каждого j-ro блока коммутации объединены и подключены к четвертому управляющему входу j-ro блока коммутации и j-му управляющему входу второй группы матричного коммутатора введены второй и третий мультиплексоры, третий и четвертый дешифраторы, схема сравнения, второй элемент И, N блоков модификации адреса, причем второй выход разрешения блока управления соединен с входом разрешения схемы сравнения и входами разрешения всех блоков модификации адреса, входы режима которых объединены и подключены к выходу второго элемента И, соединенного своим первым входом с третьим выходом первого дешифратора, выход первого мультиплексора подключен к первому информационному входу второго мультиплексора и первому информационному входу схемы сравнения, второй информационный вход которой объединен с первым информационным входом третьего мультиплексора и подключен к младшим разрядам входа адреса отказавшего абонента устройства и входам кода блоков модификации адреса, старшие разряды входа адреса отказавшего абонента устройства подключены к информационному входу третьего дешифратора, j-й выход которого подключен к входу выбора j-ro блока модификации адреса, управляющий вход третьего дешифратора объединен с управляющим входом второго мультиплексора и вторым входом второго элемента И и подключен к второму выходу разрешения блока управления, третий выход разрешения которого соединен с управляющим входом третьего мультиплексора и управляющим входом четвертого дешифратора, j-й выход которого соединен с входом выбора новой связи

j-ro блока модификации адреса, информационный вход четвертого дешифратора подключен к младшим разрядам входа адреса резервного абонента устройства, второй информационный вход третьего мультиплексора соединен со старшими разрядами входа адреса резервного абонента устройства и первыми информационными входами всех блоков модификации адреса, входы

0 сравнения которых объединены и соединены с входом сравнения блока управления и выходом схемы сравнения, четвертый выход разрешения блока управления подключен к входам чтение/запись блоков памяти, вы5 ход каждого j-ro Q 1,N) блока памяти соединен с вторым информационным входом j-ro блока модификации адреса, третьи информационные входы блоков модификации адреса объединены и подключены к второму

0 информационному выходу блока управления, тактовый выход каждого j-ro блока модификации адреса соединен с j-м тактовым входом группы матричного коммутатора, вторые адресные входы блоков памяти объ5 единены и соединены с первым входом перекоммутации матричного коммутатора и выходом второго мультиплексора, второй информационный вход которого соединен с выходом третьего мультиплексора, выход

0 перекоммутации каждого j-ro блока моди- фикации.адреса соединен с j-м входом группы перекоммутации адреса матричного коммутатора, выход разрешения каждого j- го блока модификации адреса соединен с j-м

5 управляющим входом группы матричного коммутатора, информационные выходы всех блоков модификации адреса объединены.

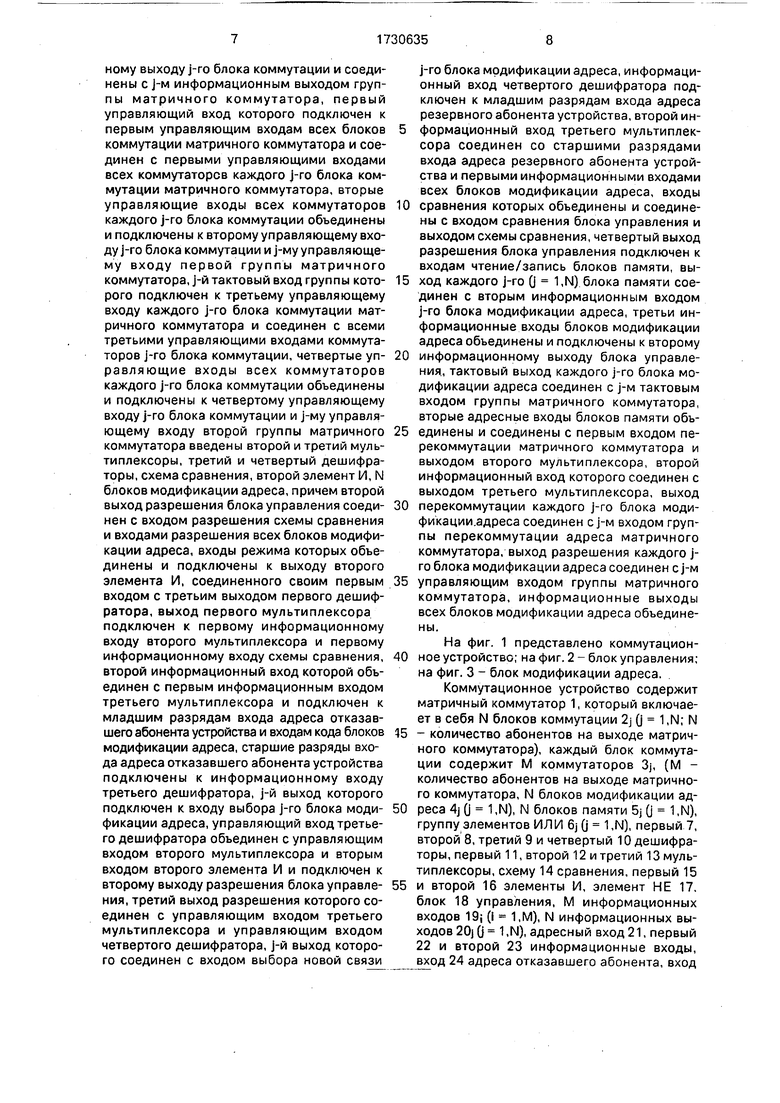

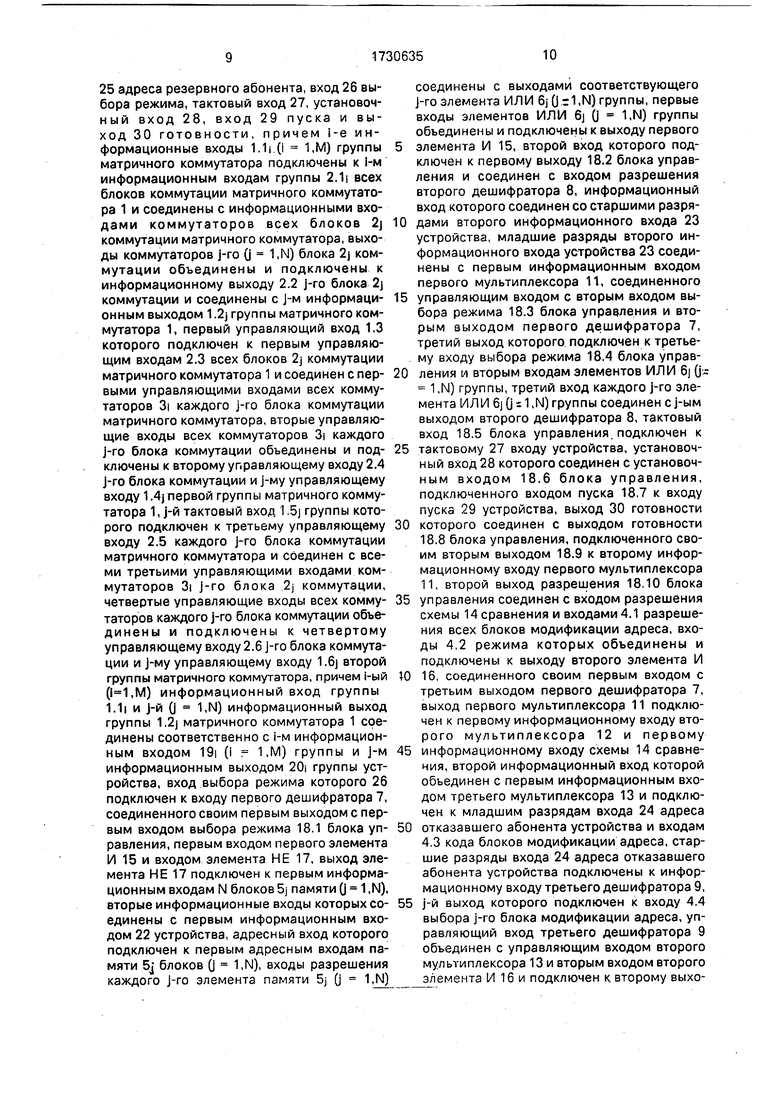

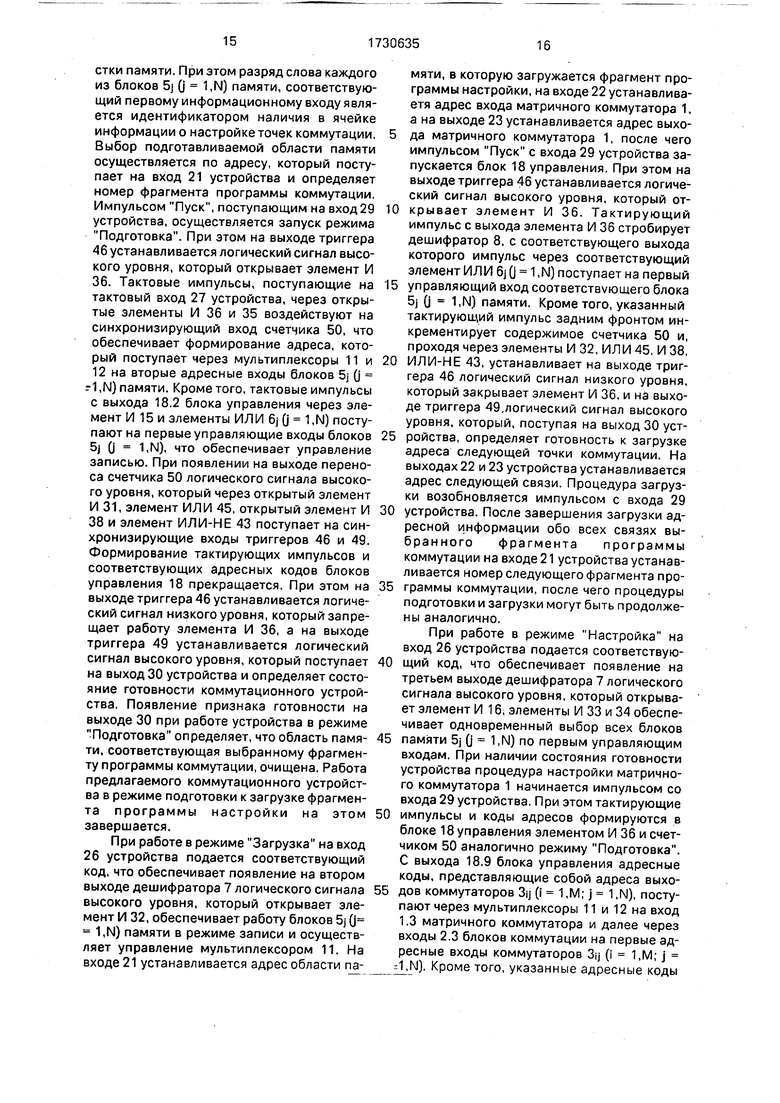

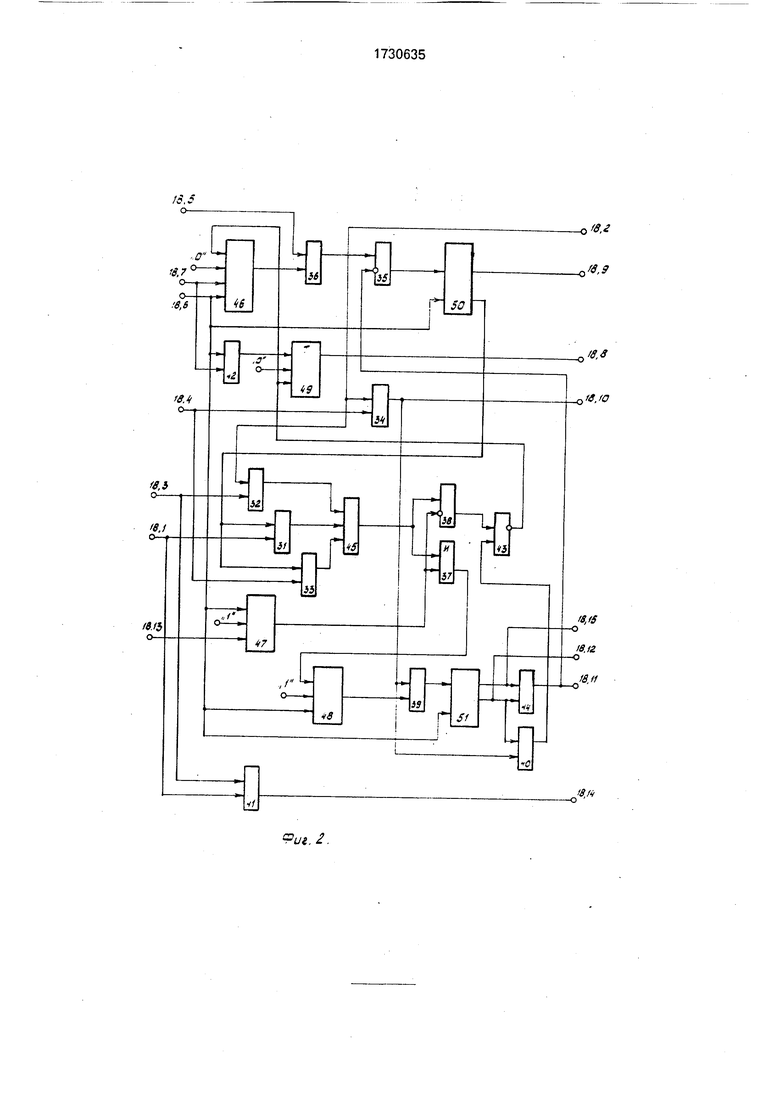

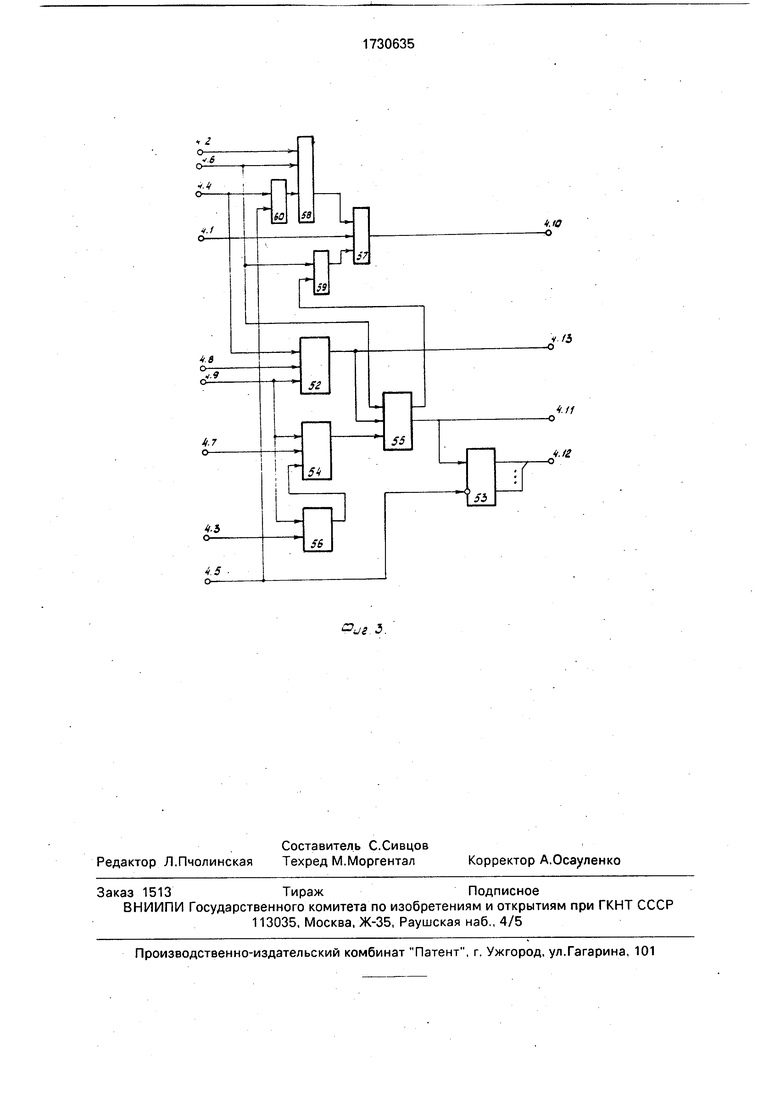

На фиг. 1 представлено коммутацион0 ное устройство; на фиг. 2 - блок управления; на фиг. 3 - блок модификации адреса.

Коммутационное устройство содержит матричный коммутатор 1, который включае- ет в себя N блоков коммутации 1 (j 1 ,N; N

5 - количество абонентов на выходе матричного коммутатора), каждый блок коммутации содержит М коммутаторов 3j, (M - количество абонентов на выходе матричного коммутатора, N блоков модификации ад0 реса 4j Q 1 ,N), N блоков памяти 5j (j 1 ,N), группу элементов ИЛИ 6j (j 1,N), первый 7, второй 8, третий 9 и четвертый 10 дешифраторы, первый 11, второй 12 и третий 13 мультиплексоры, схему 14 сравнения, первый 15

5 и второй 16 элементы И, элемент НЕ 17. блок 18 управления, М информационных входов 19j (i 1,M), N информационных выходов 20j (j 1 ,N), адресный вход 21, первый 22 и второй 23 информационные входы, вход 24 адреса отказавшего абонента, вход

25 адреса резервного абонента, вход 26 выбора режима, тактовый вход 27, установоч- ный вход 28, вход 29 пуска и выход 30 готовности, причем i-e информационные входы 1.1; (i 1,M) группы матричного коммутатора подключены к i-м информационным входам группы 2.1| всех блоков коммутации матричного коммутатора 1 и соединены с информационными входами коммутаторов всех блоков 2 коммутации матричного коммутатора, выходы коммутаторов j-ro 0 1.N) блока 1 коммутации объединены и подключены к информационному выходу 2.2 j-ro блока 2j коммутации и соединены с j-м информационным выходом 1.2j группы матричного коммутатора 1, первый управляющий вход 1.3 которого подключен к первым управляющим входам 2.3 всех блоков 1 коммутации матричного коммутатора 1 и соединен с первыми управляющими входами всех коммутаторов 3| каждого j-ro блока коммутации матричного коммутатора, вторые управляющие входы всех коммутаторов 3i каждого j-ro блока коммутации объединены и подключены к второму управляющему входу 2.4 j-ro блока коммутации и j-му управляющему входу 1 А первой группы матричного коммутатора 1, j-й тактовый вход 1,5j группы которого подключен к третьему управляющему входу 2.5 каждого j-ro блока коммутации матричного коммутатора и соединен с всеми третьими управляющими входами коммутаторов 3i j-ro блока 2j коммутации, четвертые управляющие входы всех коммутаторов каждого j-ro блока коммутации объе- динены и подключены к четвертому управляющему входу 2.6 j-ro блока коммутации и j-му управляющему входу 1.6j второй группы матричного коммутатора, причем i-ый (,M) информационный вход группы 1.1| и j-й (j 1,N) информационный выход группы 1.2j матричного коммутатора 1 соединены соответственно с i-м информационным входом 19i (i 1,M) группы и j-м информационным выходом 20i группы устройства, вход выбора режима которого 26 подключен к входу первого дешифратора 7, соединенного своим первым выходом с первым входом выбора режима 18.1 блока управления, первым входом первого элемента И 15 и входом элемента НЕ 17, выход элемента НЕ 17 подключен к первым информационным входам N блоков 5j памяти (j 1 ,N), вторые информационные входы которых соединены с первым информационным входом 22 устройства, адресный вход которого подключен к первым адресным входам памяти 5j блоков (j 1,М), входы разрешения каждого j-ro элемента памяти 5j (j 1,N)

соединены с выходами соответствующего j-ro элемента ИЛИ 6j 0 r1,N) группы, первые входы элементов ИЛИ 6j (j 1,N) группы объединены и подключены к выходу первого

элемента И 15, второй вход которого подключен к первому выходу 18.2 блока управления и соединен с входом разрешения второго дешифратора 8, информационный вход которого соединен со старшими разря0 дами второго информационного входа 23 устройства, младшие разряды второго информационного входа устройства 23 соединены с первым информационным входом первого мультиплексора 11, соединенного

5 управляющим входом с вторым входом выбора режима 18.3 блока управления и вторым выходом первого дешифратора 7, третий выход которого подключен к третьему входу выбора режима 18.4 блока управ0 ления и вторым входам элементов ИЛИ 6j О- 1 ,N) группы, третий вход каждого j-ro элемента ИЛИ 6j (j 1.N) группы соединен cj-ым выходом второго дешифратора 8, тактовый вход 18.5 блока управления, подключен к

5 тактовому 27 входу устройства, установочный вход 28 которого соединен с установоч- ным входом 18.6 блока управления, подключенного входом пуска 18.7 к входу пуска 29 устройства, выход 30 готовности

0 которого соединен с выходом готовности 18.8 блока управления, подключенного своим вторым выходом 18.9 к второму информационному входу первого мультиплексора 11, второй выход разрешения 18.10 блока

5 управления соединен с входом разрешения схемы 14 сравнения и входами 4.1 разрешения всех блоков модификации адреса, входы 4,2 режима которых объединены и подключены к выходу второго элемента И

16, соединенного своим первым входом с третьим выходом первого дешифратора 7, выход первого мультиплексора 11 подключен к первому информационному входу второго мультиплексора 12 и первому

5 информационному входу схемы 14 сравнения, второй информационный вход которой объединен с первым информационным входом третьего мультиплексора 13 и подключен к младшим разрядам входа 24 адреса

0 отказавшего абонента устройства и входам 4.3 кода блоков модификации адреса, старшие разряды входа 24 адреса отказавшего абонента устройства подключены к информационному входу третьего дешифратора 9,

5 j-й выход которого подключен к входу 4.4 выбора j-ro блока модификации адреса, управляющий вход третьего дешифратора 9 объединен с управляющим входом второго мультиплексора 13 и вторым входом второго элемента И 16 и подключен к второму выходу 18.11 разрешения блока управления, третий выход 18.12 разрешения которого соединен с управляющим входом третьего мультиплексора 12 и управляющим входом четвертого дешифратора 10, j-й выход которого соединен с входом 4.5 выбора новой связи j-ro блока модификации адреса, информационный вход четвертого дешифратора подключен к младшим разрядам входа 25 адреса резервного абонента устройства, второй информационный вход третьего мультиплексора 13 соединен с старшими разрядами входа 25 адреса резервного абонента устройства и первыми информационными входами 4.6 всех блоков модификации адреса, входы 4.7 сравнения которых объединены и соединены с входом 18.13 сравнения блока управления и выходом схемы 14 сравнения, четвертый выход 18.14 разрешения блока управления подключен к входам чтения-записи блоков 5j 0 1iN) памяти, выход каждого j-ro блока памяти соединен с вторым информационным входом 4.8j j-ro блока модификации адреса, третьи информационные входы 4.9 блоков модификации адреса объединены и подключены к второму информационному выходу 18.15 блока управления, тактовый выход 4.10 каждого j-ro блока модификации адреса соединен с j-м тактовым входом 1.5j (j 1 ,N) группы матричного коммутатора, вторые адресные входы блоков 5j 0 1tN) памяти объединены и соединены с первым входом 1.3 перекоммутации матричного коммутатора и выходом второго мультиплексора 12, второй информационный вход которого соединен с выходом третьего мультиплексора 13, выходы 4.11 перекоммутации каждого j-ro блока модификации адреса соединен с j-ым входом группы перекоммутации адреса 1.4j(j 1.N) матричного коммутатора, выход 4.12 разрешения каждого j-ro блока модификации адреса соединен с j-м управляющим входом 1.6j 0 1.N) группы матричного коммутатора, информационные выходы 4.13 всех блоков модификации адреса объединены.

Блок 18 управления содержит первый 31, второй 32, третий 33, четвертый 34, пятый 35, шестой 36, седьмой 37, восьмой 38, девятый 39 и десятый 40 элементы И, первый 41 и второй 42 элементы ИЛИ, элемент ИЛИ-НЕ 43, четвертый 44 и третий 45 элементы ИЛИ, первый 46, второй 47, третий 48 и четвертый 49 триггеры, а также первый 50 и второй 51 счетчики, причем первый вход режима 18.1 блока управления соединен с первыми входами первого элемента И 31 и первого элемента ИЛИ 41, второй вход первого элемента ИЛИ 41 объединен с первым входом второго элемента И 32 и подключен

к второму входу режима 18.3 блока управления, третий вход режима 18.4 блока управления соединен с первыми входами элементов И 33 и 34, второй вход четвертого

элемента И 34 соединен со вторым входом второго элемента И 32, первым входом пятого элемента И 35 и первым выходом разрешения 18.2 блока управления и подключен к выходу шестого элемента И 36,

0 первый вход шестого элемента И соединен с тактовым входом 18.5 блока управления, установочный вход блока управления 18.6 соединен с первым входом второго элемента ИЛИ 42 и подключен к входам установки

5 в ноль первого 46, второго 47, третьего 48 триггеров, а также первого 50 и второго 51 счетчиков, вход 18.7 пуска блока управления подключен к входу установки в единицу первого триггера 46 и второму входу второго

0 элемента ИЛИ 42, выход второго элемента ИЛИ 42 подключен к входу установки в ноль четвертого триггера 49, информационный вход которого соединен с источником логического нуля устройства, а выход подключен

5 к выходу готовности 18.8 блока управления, вход 18.13 сравнения которого соединен с входом синхронизации второго триггера 47, информационный вход второго триггера 47 подключен к источнику 1 устройства, а вы0 ход соединен с первыми входами седьмого элемента И 37 и восьмого элемента И 38, выход восьмого элемента И 38 подключен к первому входу элемента ИЛИ-НЕ 43, выход которого подключен к входам синхрониза5 ции первого триггера 46 и четвертого триггера 49, информационный вход первого триггера 46 подключен к источнику О устройства, выход первого триггера подключен к второму входу шестого элемента И 36,

0 первый информационный выход 18.9 блока управления соединен с первым выходом первого счетчика 50, второй выход которого подключен к вторым входам первого элемента И 31 и третьего элемента И 33, выхо5 ды которых соединены соответственно с первым и вторым входами четвертого элемента ИЛИ 45, третий вход которого подключен к выходу второго элемента И 32, выход четвертого элемента ИЛИ со0 единен с вторыми входами элементов И 38 и 37, выход седьмого элемента И 37 подключен к входу синхронизации третьего триггера 48, информационный вход которого соединен с источником

5 1 устройства, а выход подключен к первому входу девятого элемента И 39, второй вход которого соединен с первым входом десятого элемента И 40, вторым выходом 18.10 разрешения блока управления и подключен к выходу четвертого элемента И 34, выход девятого элемента И 39 соединен с входом синхронизации второго счетчика 51, первый выход которого подключен к второму информационному выходу 18.15 блока управления и первому входу третьего элемента ИЛИ 44, выход которого соединен с третьим выходом 18.11 разрешения блока управления и подключен к второму входу пятого элемента И 35, выход которого соединен с входом синхронизации первого счетчика 50, второй выход второго счетчика 51 соединен с вторым выходом разрешения 18.12 блока управления, с вторым входом третьего элемента ИЛИ 44 и подключен к второму входу десятого элемента И 40, выход которого соединен с вторым входом элемента ИЛИ-НЕ 43, четвертый выход 18.14 разрешения блока управления подключен к выходу первого элемента ИЛИ 41.

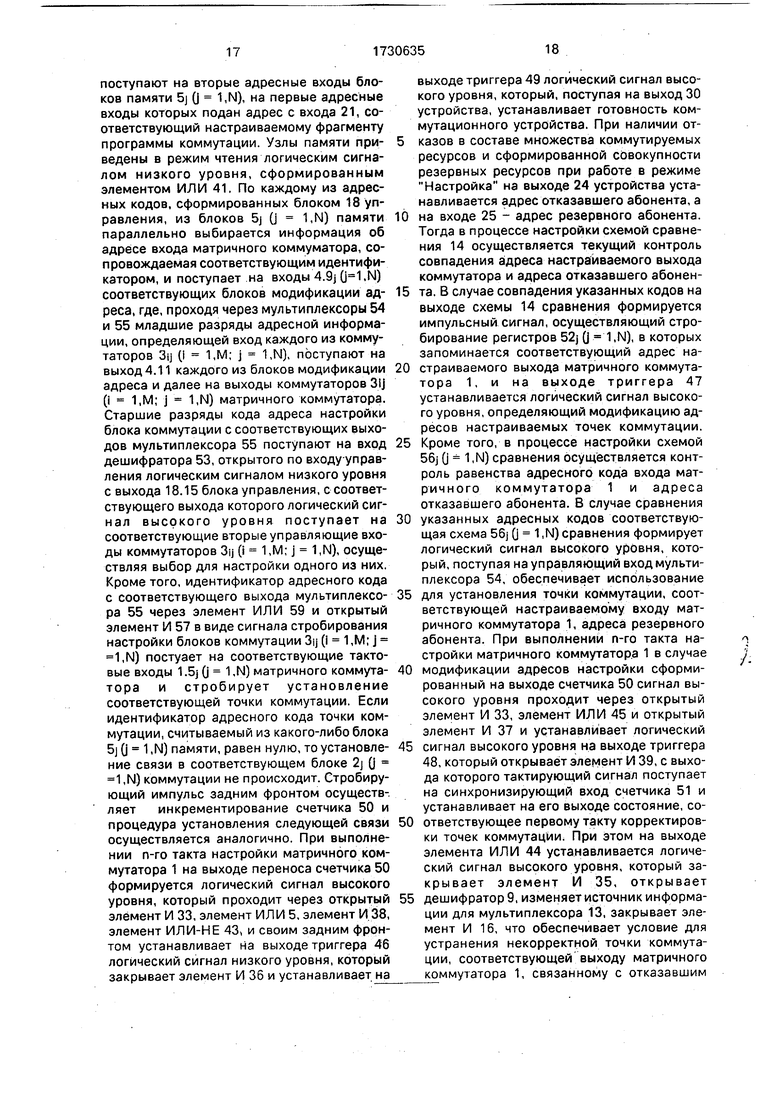

Блок 4 модификации адреса содержит регистр 52, дешифратор 53, первый 54 и второй 55 мультиплексоры, схему 56 сравнения, первый элемент И 57, первый 58 и второй 59 элементы ИЛИ и второй элемент И 60, причем первый вход 4.1 разрешения блока модификации адреса соединен с первым входом первого элемента И 57, выход которого подключен к тактовому выходу 4.10 блока модификации адреса, вход 4.2 режима блока соединен с первым входом первого элемента ИЛИ 58, выход которого подключен к второму входу первого элемента И 57, вход 4.3 кода блока модификации адреса соединен с первым входом схемы 56 сравнения, выход которой подключен к управляющему входу первого мультиплексора 54, выход которого соединен с первым входом второго мультиплексора 55, информационный выход второго мультиплексора подключен к первому входу второго элемента ИЛИ 59, выход которого соединен с третьим входом первого элемента И 57, выход второго мультиплексора 55 подключен к выходу 4.11 перекоммутации адреса блока модификации адреса, выход 4.12 разрешения которого соединен с соответствующими N выходами дешифратора 53, информационный вход дешифратора подключен к выходу кода старших разрядов адреса второго мультиплексора 55, вход 4.4 выбора блока модификации адреса соединен с первым входом второго элемента И 60 и управляющим входом регистра 52, выход второго элемента И 60 подключен к второму входу первого элемента ИЛИ 58, выход регистра соединен с вторым входом второго мультиплексора 55 и информационным выходом 4.13 блока модификации адреса, вход адреса резервного абонента 4.5 блока соединен

с вторым входом второго элемента И 60 и управляющим входом дешифратора 53, первый информационный вход 4.6 блока модификации адреса соединен с управляющим

входом второго мультиплексора 55, вторым входом второго элемента ИЛИ 59 и третьим входом первого элемента ИЛИ 58, вход 4.7 сравнения блока модификации адреса соединен с первым входом первого мульти0 плексора 54, второй информационный вход 4.8 блока подключен к входу синхронизации регистра 52, информационный вход регистра соединен с вторым входом первого мультиплексора 54, с вторым входом схемы 56

5 сравнения и подключен к третьему информационному входу 4,9 блока модификации адреса.

Предлагаемое коммутационное устройство работает в четырех режимах: в режиме

0 Подготовка приводятся в исходные состояния блоки 5j 0 1.N) памяти; в режиме Загрузка в узлы 5j Q 1 ,N) памяти загружается программа коммутации; в режиме Настройка программа коммутации

5 загружается в матричный коммутатор 1, что обеспечивает установление требуемых коммутационных связей, при наличии отказавших коммутационных ресурсов в ходе режима Настройка осуществляется моди0 фикация адресов точек коммутации с целью установления корректных соединений; по окончании режима Настройка устройство готово к работе в режиме Обмен, в котором осуществляется передача информации

5 через матричный коммутатор 1 с выходов 19i (i 1 ,М) на выходы 20j 0 1 .N).

Предлагаемое устройство работает следующим образом.

Импульсом начальной установки с вхо0 да 28 устройства приводятся в исходное состояние триггеры 46 - 49 и счетчики 50 и 51. Выбор режима работы коммутационного устройства осуществляется кодом, поступающим на вход 26. При работе в режиме

5 Подготовка на первом выходе дешифратора 7 формируется логический сигнал высокого уровня, что обеспечивает работу блоков 5j (j 1,N) памяти в режиме записи воздействием на их вторые управляющие

0 входы через элемент ИЛИ 41 и управление записью информации в блоки 5j (j 1,N) памяти посредством воздействия на их первые управляющие входы стробирующих импульсов с первого выхода 18.2 блока

5 управления через элемент И 15 и группу элементов ИЛИ 6j 0 1.N). Кроме того, на первые информационные входы блоков 5 Q 1.N) памяти поступает логический сигнал низкого уровня с выхода элемента НЕ 17, что обеспечивает эмуляцию процедуры очистки памяти. При этом разряд слова каждого из блоков 5j О 1,М) памяти, соответствующий первому информационному входу является идентификатором наличия в ячейке информации о настройке точек коммутации. Выбор подготавливаемой области памяти осуществляется по адресу, который поступает на вход 21 устройства и определяет номер фрагмента программы коммутации. Импульсом Пуск, поступающим на вход 29 устройства, осуществляется запуск режима Подготовка. При этом на выходе триггера 46 уста н а вливается логический сигнал высокого уровня, который открывает элемент И 36. Тактовые импульсы, поступающие на тактовый вход 27 устройства, через открытые элементы И 36 и 35 воздействуют на синхронизирующий вход счетчика 50, что обеспечивает формирование адреса, который поступает через мультиплексоры 11 и 12 на вторые адресные входы блоков 5j Q г1 ,N) памяти. Кроме того, тактовые импульсы с выхода 18.2 блока управления через элемент И 15 и элементы ИЛИ 6j Q 1,N) поступают на первые управляющие входы блоков 5j 0 1 N), что обеспечивает управление записью. При появлении на выходе переноса счетчика 50 логического сигнала высокого уровня, который через открытый элемент И 31, элемент ИЛИ 45, открытый элемент И 38 и элемент ИЛИ-НЕ 43 поступает на синхронизирующие входы триггеров 46 и 49. Формирование тактирующих импульсов и соответствующих адресных кодов блоков управления 18 прекращается. При этом на выходе триггера 46 устанавливается логический сигнал низкого уровня, который запрещает работу элемента И 36, а на выходе триггера 49 устанавливается логический сигнал высокого уровня, который поступает на выход 30 устройства и определяет состояние готовности коммутационного устройства. Появление признака готовности на выходе 30 при работе устройства в режиме Подготовка определяет, что область памяти, соответствующая выбранному фрагменту программы коммутации, очищена. Работа предлагаемого коммутационного устройства в режиме подготовки к загрузке фрагмента программы настройки на этом завершается.

При работе в режиме Загрузка на вход 26 устройства подается соответствующий код, что обеспечивает появление на втором выходе дешифратора 7 логического сигнала высокого уровня, который открывает элемент И 32, обеспечивает работу блоков 5j 0 1,1М) памяти в режиме записи и осуществляет управление мультиплексором 11. На входе 21 устанавливается адрес области памяти, в которую загружается фрагмент программы настройки, на входе 22 устанавлива- етя адрес входа матричного коммутатора 1, а на выходе 23 устанавливается адрес выхода матричного коммутатора 1, после чего импульсом Пуск с входа 29 устройства запускается блок 18 управления. При этом на выходе триггера 46 устанавливается логический сигнал высокого уровня, который от0 крывает элемент И 36. Тактирующий импульс с выхода элемента И 36 стробирует дешифратор 8, с соответствующего выхода которого импульс через соответствующий элемент ИЛИ 6j Q 1 ,N) поступает на первый

5 управляющий вход соответствующего блока 5j (j 1,N) памяти. Кроме того, указанный тактирующий импульс задним фронтом ин- крементирует содержимое счетчика 50 и, проходя через элементы И 32, ИЛИ 45, И 38,

0 ИЛИ-НЕ 43, устанавливает на выходе триггера 46 логический сигнал низкого уровня, который закрывает элемент И 36, и на выходе триггера 49.логический сигнал высокого уровня, который, поступая на выход 30 уст5 ройства, определяет готовность к загрузке адреса следующей точки коммутации. На выходах 22 и 23 устройства устанавливается адрес следующей связи. Процедура загрузки возобновляется импульсом с входа 29

0 устройства. После завершения загрузки адресной информации обо всех связях выбранного фрагмента программы коммутации на входе 21 устройства устанавливается номер следующего фрагмента про5 граммы коммутации, после чего процедуры подготовки и загрузки могут быть продолжены аналогично.

При работе в режиме Настройка на вход 26 устройства подается соответствую0 щий код, что обеспечивает появление на третьем выходе дешифратора 7 логического сигнала высокого уровня, который открывает элемент И 16, элементы И 33 и 34 обеспечивает одновременный выбор всех блоков

5 памяти 5j Q 1,N) по первым управляющим входам. При наличии состояния готовности устройства процедура настройки матричного коммутатора 1 начинается импульсом со входа 29 устройства. При этом тактирующие

0 импульсы и коды адресов формируются в блоке 18 управления элементом И 36 и счетчиком 50 аналогично режиму Подготовка. С выхода 18.9 блока управления адресные коды, представляющие собой адреса выхо5 дов коммутаторов 3ij (i 1 ,М; j 1 ,N), поступают через мультиплексоры 11 и 12 на вход 1.3 матричного коммутатора и далее через входы 2.3 блоков коммутации на первые адресные входы коммутаторов 3jj (i 1,M; j 1,N). Кроме того, указанные адресные коды

поступают на вторые адресные входы блоков памяти 5j Q 1,М), на первые адресные входы которых подан адрес с входа 21, соответствующий настраиваемому фрагменту программы коммутации. Узлы памяти приведены в режим чтения логическим сигналом низкого уровня, сформированным элементом ИЛИ 41, По каждому из адресных кодов, сформированных блоком 18 управления, из блоков 5j 0 1iN) памяти параллельно выбирается информация об адресе входа матричного коммуматора, сопровождаемая соответствующим идентификатором, и поступает на входы 4.9j .N) соответствующих блоков модификации адреса, где, проходя через мультиплексоры 54 и 55 младшие разряды адресной информации, определяющей вход каждого из коммутаторов 3ij (i 1,M; j 1,N), поступают на выход 4.11 каждого из блоков модификации адреса и далее на выходы коммутаторов 3IJ (i 1,М; j 1,N) матричного коммутатора. Старшие разряды кода адреса настройки блока коммутации с соответствующих выходов мультиплексора 55 поступают на вход дешифратора 53, открытого по входу управления логическим сигналом низкого уровня с выхода 18.15 блока управления, с соответствующего выхода которого логический сиг- нал высокого уровня поступает на соответствующие вторые управляющие входы коммутаторов 3ij (i 1,M; j 1,N), осуществляя выбор для настройки одного из них. Кроме того, идентификатор адресного кода с соответствующего выхода мультиплексора 55 через элемент ИЛИ 59 и открытый элемент И 57 в виде сигнала стробирования настройки блоков коммутации 3ij (i 1 ,М; j 1,N) постуает на соответствующие тактовые входы 1.5j (j 1,N) матричного коммутатора и стробирует установление соответствующей точки коммутации. Если идентификатор адресного кода точки коммутации, считываемый из какого-либо блока 5j (j 1 ,N) памяти, равен нулю, то установление связи в соответствующем блоке 2j 0 1,М) коммутации не происходит. Стробиру- ющий импульс задним фронтом осуществляет инкрементирование счетчика 50 и процедура установления следующей связи осуществляется аналогично. При выполнении n-го такта настройки матричного коммутатора 1 на выходе переноса счетчика 50 формируется логический сигнал высокого уровня, который проходит через открытый элемент И 33, элемент ИЛИ 5, элемент И 38, элемент ИЛИ-НЕ 43, и своим задним фронтом устанавливает на выходе триггера 46 логический сигнал низкого уровня, который закрывает элемент И 36 и устанавливает на

выходе триггера 49 логический сигнал высокого уровня, который, поступая на выход 30 устройства, устанавливает готовность коммутационного устройства. При наличии отказов в составе множества коммутируемых ресурсов и сформированной совокупности резервных ресурсов при работе в режиме Настройка на выходе 24 устройства устанавливается адрес отказавшего абонента, а

0 на входе 25 - адрес резервного абонента. Тогда в процессе настройки схемой сравнения 14 осуществляется текущий контроль совпадения адреса настраиваемого выхода коммутатора и адреса отказавшего абонен5 та. В случае совпадения указанных кодов на выходе схемы 14 сравнения формируется импульсный сигнал, осуществляющий стро- бирование регистров 52j (J 1.N), в которых запоминается соответствующий адрес на0 страиваемого выхода матричного коммутатора 1, и на выходе триггера 47 устанавливается логический сигнал высокого уровня, определяющий модификацию адресов настраиваемых точек коммутации.

5 Кроме того, в процессе настройки схемой 56j 0 1-М) сравнения осуществляется контроль равенства адресного кода входа матричного коммутатора 1 и адреса отказавшего абонента. В случае сравнения

0 указанных адресных кодов соответствующая схема 56j (j 1 ,N) сравнения формирует логический сигнал высокого уровня, который, поступая на управляющий вход мультиплексора 54, обеспечивает использование

5 для установления точки коммутации, соответствующей настраиваемому входу матричного коммутатора 1, адреса резервного абонента. При выполнении n-го такта настройки матричного коммутатора 1 в случае

0 модификации адресов настройки сформированный на выходе счетчика 50 сигнал высокого уровня проходит через открытый элемент И 33, элемент ИЛИ 45 и открытый элемент И 37 и устанавливает логический

5 сигнал высокого уровня на выходе триггера 48, который открывает элемент И 39, с выхода которого тактирующий сигнал поступает на синхронизирующий вход счетчика 51 и устанавливает на его выходе состояние, со0 ответствующее первому такту корректировки точек коммутации. При этом на выходе элемента ИЛИ 44 устанавливается логический сигнал высокого уровня, который закрывает элемент И 35, открывает

5 дешифратор 9, изменяет источник информации для мультиплексора 13, закрывает элемент И 16, что обеспечивает условие для устранения некорректной точки коммутации, соответствующей выходу матричного коммутатора 1, связанному с отказавшим

абонентом. Так адрес выхода матричного коммутатора поступает с входа 24 устройства через мультиплексоры 13 и 12 на соответствующие первые адресные входы коммутаторов 3ij (i - 1 ,М; j 1,N), принадле- жащих блокам 2j Q 1,N) коммутации. При этом логический сигнал высокого уровня с первого выхода счетчика 51 поступает на управляемые нулем управляющие входы дешифраторов 53j 0 1.N) и запрещает их работу. Кроме того, логический сигнал высокого уровня запрещает работу счетчика 50. На j-м выходе дешифратора 9 формируется логический сигнал высокого уровня, который поступает на вход 4.4 соответствующего блока модификации адреса и далее через элемент И 60 и элемент ИЛИ 58 на второй вход элемента И 57. Тактирующий сигнал с выхода 18.10 блока управления поступает на входы 4.1 (| г 1,М) блоков модификации адреса и далее на входы элементов И 57j 0 1 ,N). При этом откры- тым остается только элемент И 57, соответствующий выбранному блоку 4j Q d ,N) модификации адреса, что обеспечивает стробирование с выхода 4.10 только соответствующего блока коммутации 2 ( 1 ,N) и размыкание точки коммутации, соответствующий выходу матричного коммутатора 1, подключенного к входу отказавшего або- нента. Далее задним фронтом тактирующего сигнала счетчика 51 устанавливается в состояние, соответствующее второму такту корректировки. При этом разрешена работа дешифраторов 9 и 10, на выходах которых формируются логические сигналы высокого уровня, соответствующие адресу отказавшего и адресу резервного ресурсов соответственно, изменено направление передачи информации мультиплексора 13. Логиче- ский сигнал высокого уровня с соответствующего выхода дешифратора 9 поступает на вход 4.4 блока 4j (j 1 ,N) модификации адреса, соответствующего выходу матричного коммутатора 1, подключенного к входу отка- завшего абонента, где снимает третье состояние с выхода регистра 52, что обеспечивает появление на вторых информационных входах мультиплексоров 55j (j 1 ,N) адресного кода входа матричного ком- мутатора 1, соответствующего отказавшему абоненту. Логический сигнал высокого уровня с соответствующего выхода дешифратора 10 поступает на вход 4.5 блока 4j (j 1,N) модификации адреса, соответствующе- го выходу матричного коммутатора 1, подключенного к входу резервного абонента, где изменяет направление передачи в мультиплексоре 55 и открывает элемент И 57 для передачи стробирующего импульса, который, поступая на первые управляющие входы соответствующих коммутаторов 3ij (i 1,М; j 1.N), осуществляет организацию точки коммутации в соответствии с адресом входа матричного коммутатора 1, поступающим с выхода мультиплексора 55. Кроме того, задним фронтом тактирующего импульса, соответствующего второй фазе корректировки устанавливаются в соответствующие состояния триггеры 46 и 49, что определяет завершение настройки матричного коммутатора. Таким образом, для выполнения настройки матричного коммутатора в предлагаемом коммутационном устройстве необходимо два дополнительных такта, первый из которых соответствует фазе уничтожения некорректной точки коммутации, а второй определяет фазу установления точки коммутации, соответствующей адресу резервного абонента.

В качестве коммутаторов 3ij (i 1,M; j 1 ,N) могут быть использованы микросхемы 1509 КП1, в качестве узлов 5j 0 1,N) памяти - микросхемы 541 РУ1, в качестве мультиплексоров 11 - 13, 54 и 55 - микросхемы 530 КП11.

В устройстве-прототипе процедура реконфигурации коммутационных связей в случае отказа абонента и замены его соответствующим резервным может быть реализована за время

Ti Ti + Т2,

где Ti - время корректировки списка связей;

Та - время повторной настройки матричного коммутатора.

Время корректировки списка связей может быть определено соотношением

Ti Nnp x n x tK, где tK - длительность такта корректировки;

Nnp - количество программ настройки коммутатора.

Время настройки матричного коммутатора определяется соотношением

Т2 n x tH, где tn - длительность такта настройки.

При этомт,к т.н.

В предлагаемом устройстве реконфигурация коммутационных связей осуществляется непосредственно в процессе настройки.

Время настройки при этом составляет Тз (п -(- 2) x tH.

Приведем t и tH к длине машинного такта tM, определяемой тактирующими импульсами. Допустим, что 1н tM. а и L x tM, где L - сложность программной реализации одной операции корректировки.

Тогда для устройства-прототипа

Т Nnp xnxLxtM + пхТм

для предлагаемого устройства

Тз (л + 2) х т.н.

Учитывая, что Т2 Тз, a Ti Т2, можно считать, что Т Тз, т. е. проедлагаемое коммутационное устройство позволяет повы- сить скорость реконфигурации связей при выходе из строя абонентов в К (Nnp x L + 1) раз.

Формула изобретения

подключен к тактовому входу устройства, установочный вход которого соединен с установочным входом блока управления, подключенного входом пуска к входу пуска устройства, выход готовности которого соединен с выходом готовности блока управления, подключенного своим вторым выходом к второму информационному входу первого мультиплексора. 1-е информационные входы (i 1,М) группы матричного коммутатора подключены к i-м информационным входам группы всех блоков коммутации матричного коммутатора и соединены с информационными входами коммутаторов всех блоков коммутации матричного коммутатора, выходы коммутаторов j-ro (j T7R) блока коммутации объединены, подключены к информационному выходу j-ro блока коммутации и соединены с j-м информационным выходом группы матричного коммутатора, первый управляющий вход которого подключен к первым управдляющим входам всех блоков коммутации матричного коммутатора и соединен с первыми управляющими входами всех коммутаторов каждого j-ro блока коммутации матричного коммутатора, вторые управляющие входы всех коммутаторов каждого j-ro блока коммутации объе- динены и подключены к второму управляющему входу j-ro блока коммутации и j-му управляющему входу первой группы матричного коммутатора, j-й тактовый вход группы которого подключен к третьему управляющему входу каждого j-ro блока коммутации матричного коммутатора и соединен со всеми третьими управляющими входами коммутаторов j-ro блока коммутации, четвертые управляющие входы всех коммутаторов каждого j-ro блока коммутации объединены и подключены к четвертому управляющему входу j-ro блока коммутации и j-му управляющему входу второй группы матричного коммутатора, отличающее- с я тем, что, с целью повышения скорости реконфигурации связей при выходе из строя абонентов коммутационной сети, в него ввевдены второй и третий мультиплексоры, третий и четвертый .дешифраторы, схема сравнения, второй элемент И, N блоков модификации адреса, причем второй выход разрешения блока управления соединен с входом разрешения схемы сравнения и входами разрешения всех блоков модификации адреса, входы режима которых объединены и подключены к выходу второго элемента И, соединенного своим первым входом с третьим выходом первого дешифратора, выход первого мультиплексора подключен к первому информационному входу второго мультиплексора и первому

информационному входу схемы сравнения, второй информационный вход которой объединен с первым информационным входом третьего мультиплексора и подключен к младшим М разрядам входа адреса отказав- шего абонента устройства и входам кода блоков модификации адреса, старшие разряды входа адреса отказавшего абонента устройства подключены к информационному входу третьего дешифратора, j-й выход которого подключен к входу выбора j-ro блока модификации адреса, управляющий вход третьего дешифратора объединен с управляющим входом второго мультиплексора и вторым входом второго элемента И и под- ключей к второму выходу разрешения блока управления, третий выход разрешения которого соединен с управляющим входом третьего мультиплексора и управляющим входом четвертого дешифратора, j-й выход которого соединен с входом выбора новой связи j-ro блока модификации адреса, информационный вход четвертого дешифратора подключен к младшим разрядам входа адреса резервного абонента устройства, второй информационный вход третьего мультиплексора соединен со старшими разрядами входа адреса резервного абонента устройства и первыми информационными входами всех блоков модификации адреса, входы сравнения которых объединены и соединены с входом сравнения блока управления и выходом схемы сравнения, четвертый выход разрешения блока управления подключен к входам Чтение-запись блоков памяти, выход каждого j-ro 0 1.N) блока памяти соединен с вторым информационным входом j-ro блока модификации адреса, третьи информационные входы блоков модификации адреса объединены и под- ключены к второму информационому выходу блока управления, тактовый выход каждого j-ro блока модификации адреса соединен с j-м тактовым входом группы матричного коммутатора, вторые адресные входы блоков памяти объединены и соединены с первым входом перекоммутации матричного коммутатора и выходом второго мультиплексора, второй информационный вход которого соединен с выходом третьего мультиплексора, выход перекоммутации каждого j-ro блока модификации адреса соединен с J-м входом группы перекоммутации адреса матричного коммутатора, выход разрешения каждого j-ro блока модифика- ции адреса соединен с j-м управляющим входом группы матричного коммутатора, информационные выходы всех блоков модификации адреса объединены.

3, Устройство по п. 1, отличающее- с я тем, что блок модификации адреса содержит регистр, дешифратор, первый и второй мультиплексоры, схему сравнения, первый и второй элементы И, первый и вто- рой элементы ИЛИ, причем вход разрешения блока модификации адреса соединен с первым входом первого элемента И, выход которого подключен к тактовому выходу блока модификации адреса, вход режима блока соединен с входом первого элемента ИЛИ, выход которого подключен к второму входу первого элемента И, вход кода блока модификации адреса соединен с первым входом схемы сравнения, выход которой

подключен к управляющему входу первого мультиплексора, выход которого соединен с первым входом второго мультиплексора, информационный выход второго мультиплексора подключен к первому входу второго элемента ИЛИ, выход которого соединен с третьим входом первого элемента И, младшие разряды выхода адреса второго мульти- плексора подключены к выходу перекоммутации адреса блока модификации адреса, выход разрешения которого соединен с соответствующими N выходами дешифратора, информационный вход дешифратора подключен к старшим разрядам выхода адреса второго мультиплексора, вход выбора блока модификации адреса соединен с первым входом второго элемента И и управляющим входом регистра, выход второго элемента И подключен к второму входу первого элемента ИЛИ, выход регистра соединен с входом второго мультиплексора и информационным выходом блока модификации адреса, вход адреса резервного абонента блока соединен с вторым входом второго элемента И и управляющим входом дешифратора, первый информационный вход блока модификации адреса соединен с управляющим входом второго мультиплексора, с вторым входом второго элемента ИЛИ и третьим входом первого элемента ИЛИ, вход сравнения блока модификации адреса соединен с1 первым входом первого мультиплексора, второй информационный вход блока подключен к входу синхронизации регистра, информационный вход регистра соединен с вторым входом первого мультиплексора, вторым входом схемы сравнения и подключен к третьему информационному входу блока модификации адреса.

}6

46

8Л ot$

tf.i

о-

LJ

„f

/a/3 o47

/S

y/

°ut.2.

-o«

.9

rSO

I S. O

ГЫ

18, fS

18, IZ -O

J5

г

Si

i8.lv -o

V /

О-

47 О

п

&иг 3

МО

-о

55

./г

Si

| Коммутационное устройство | 1986 |

|

SU1387006A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Коммутационное устройство | 1989 |

|

SU1645963A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

1992-04-30—Публикация

1990-04-10—Подача