(54) КОММУТАТОР

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для ввода информации | 1982 |

|

SU1064275A1 |

| Коммутатор для переключения резервных генераторов | 1988 |

|

SU1541763A1 |

| Умножитель частоты следования импульсов | 1986 |

|

SU1403356A1 |

| Селектор импульсов по длительности | 1981 |

|

SU980270A1 |

| Селектор импульсов по длительности | 1980 |

|

SU902240A1 |

| Устройство для сложения и вычитания чисел с плавающей запятой | 1980 |

|

SU959070A1 |

| Устройство для преобразования контролируемых параметров | 1986 |

|

SU1320816A1 |

| СПОСОБ ИЗМЕРЕНИЯ СКОРОСТИ ВРАЩЕНИЯ ВАЛА И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1991 |

|

RU2017156C1 |

| Устройство для считывания графической информации | 1989 |

|

SU1654852A1 |

| Устройство для формирования серий импульсов | 1985 |

|

SU1280693A1 |

1

Изобретение относится к области автоматики и может найти применение в системах синхронизации вычислительных приборов и комплексов.

По основному авт. св. № 572925 известен коммутатор, содержащий триггер, единичный выход которого соединен с одним из входов первого элемента И, а нулевой выход - с одним из входов второго элемента И выходы элементов И подключены к входам элемента ИЛИ-НЕ, выход которого соединен с выходом коммутатора, другой вход первого элемента И - с первой входной шиной коммутатора, которая подключена также к одному из входов первого элемента И-НЕ, другой вход которого соединен с единичным выходом триггера, другой вход второго элемента И соединен с второй входной шиной коммутатора, которая подключена также к одному из входов второго элемента И-НЕ, другой вход последнего соединен с нулевым выходом триггера, а также два счетчика, при этом счетный вход первого счетчика соединен с первой входной шиной, вход сброса - с выходом первого элемента И-НЕ, а выход подключен к нулевому входу триггера.

Однако это устройство имеет недостаточные функциональные возможности, поскольку реагирует лишь на такие формы отказов источников сигналов, которые приводят к появлению vTorH4ecKoro нуля в одной из входных шин. На отказ, проявляюшийся в форме логической единицы, устройство не реагирует, при этом следование импульсов с его выхода прекрашается.

Цель изобретения - расширение функциональных возможностей коммутатора.

Для этого в коммутатор введены два инвертора, два сдвигающих регистра, два элемента ИЛИ-НЕ и шина «логическая единица. К первой входной шине подключены

5 вход первого инвертора, первый вход первого элемента ИЛИ-НЕ и синхронизируюший вход второго сдвигающего регистра. К второй входной шине подключены вход второго инвертора, первый вход второго элемента ИЛИ-НЕ и синхронизирующий вход первого сдвигающего регистра. Инфор.мационные входы сдвигающих регистров объединены и подключены к шине «логическая единица.

Установочный вход первого сдвигающего регистра соединен с выходом первого инвертора, а выход - с вторым входом первого элемента ИЛИ-НЕ, выход которого подключен к счетному входу первого счетчика. Счетный вход второго счетчика соединен с выходом второго элемента ИЛИ-НЕ, который своим вторым входом подключен к выходу второго сдвигаюп1.его регистра, установочный вход которого соединен с выходом второго инвертора.

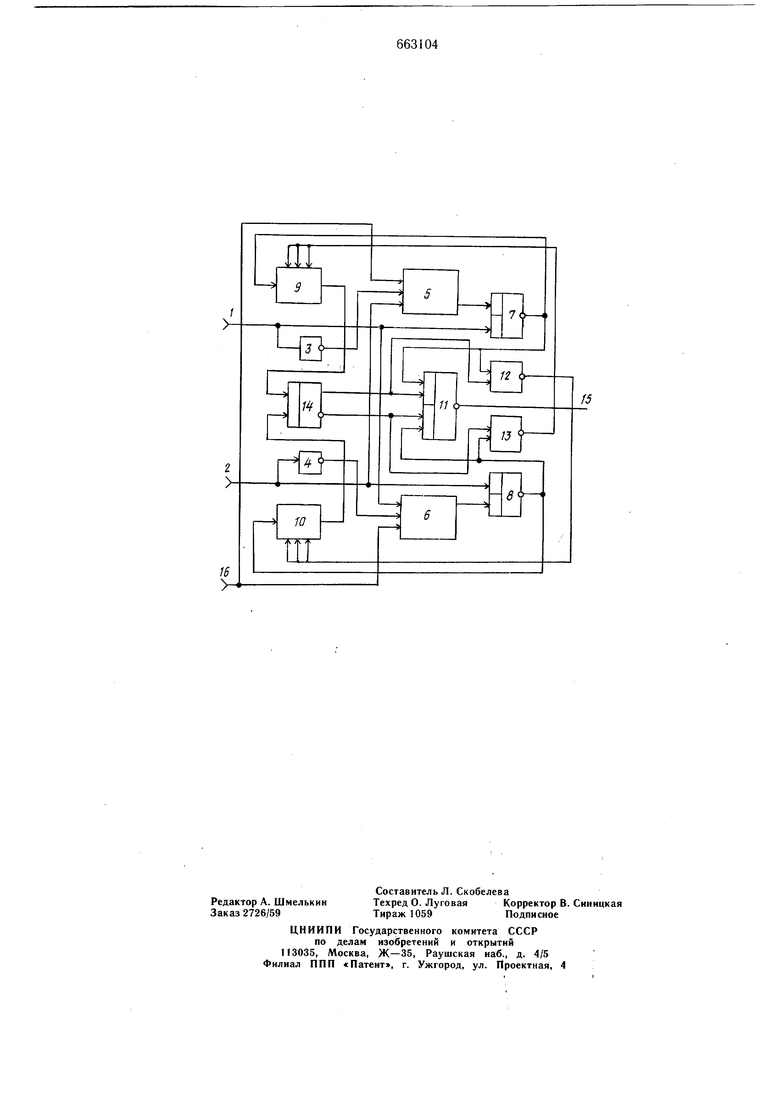

Схема коммутатора приведена на чертеже.

Коммутатор содержит входные шины 1,2, подключенные к входам инверторов 3,4, к синхронизирующим входам сдвигаюш.их регистров 5,6 и входам элементов ИЛИ-НЕ 7-8, которые своими выходами соединены со счетными входами счетчиков 9 и 10, с входами элемента И-ИЛИ-НЕ 11, а также с входами элементов И-НЕ 12 и 13, выходы которых подключены к установочным входам счетчиков 9,10. Выходы счетчиков 9,10 подсоединены к входам триггера 14, своими выходами соединенного с входами элементов И-НЕ 12,13 и с входами элемента И-ИЛИ-НЕ 11, при этом выход 15 эле.мента И-ИЛИ-НЕ 11 является выходом коммутатора. Установочные входы сдвигающих регистров 5,6 соединены с выходами инверторов 3 и 4, а их информационные входы подключены к нине 16 «логическая единица.

Работа коммутатора осуществляется следующим образом.

В исходно.м состоянии сигналы подаются на входные пгипы и 2, а триггер 14 находится в единичном состоянии. Входные сигналы через инверторы 3, 4 поступают на установочные входы сдвигающих регистров 5 и 6, удерживая на их выходах уровень логического нуля. Этот уровень обеспечивает разрешение для прохождения входных сигналов через элементы ИЛИ-НЕ 7,8. Сигналы с выхода элемента ИЛИ-НЕ 7 через элемент И-ИЛИ-НЕ 11 поступают на выход 15 коммутатора, а через элемент И-НЕ 12 удерживают счетчик 10 в сброщенном состоянии. При этом счетчик 9, отсчитывая сигналы с выхода элемента ИЛИ-НЕ 7, выдает сигнал переполнения, которым подтверждается единичное состояние триггера 14. Нулевым выходом триггера 14 устанавливается запрет на прохождение сигналов с выхода эле.мента ИЛИ-НЕ 8 через элемент И-ИЛИ-НЕ И. При прекращении поступления сигналов по входной шине 1 на ней, в зависимости от

вида отказа источника сигнала, устанавливается либо уровень логической единицы, либо логического нуля. Логическая единица состояние выходов сдвигающих регистров 5,6 не изменяет, а на выходе элемента ИЛИНЕ 7 устанавливает уровень логического нуля. При этом снимается блокировка счетчика 10.от выхода элемента И-НЕ 12, триггер 14 переходит в нулевое состояние и сигналы с выхода элемента ИЛИ-НЕ 8 через элемент И-ИЛИ-НЕ 1 1 поступают на выход 15 коммутатора. Появление логического нуля при прекращении поступления сигналов по входной шине 1 снимает блокировку сдвигающего регистра 5. Под действием сигналов поступающих на его синхронизирующий вход по входной тине 2, происходит запись и сдвиг единичной информации, которая постоянно действует на информационный вход регистра по тине 16 «логическая единица. В результате сдвига выход сдвигающего регистра 5 принимает единичное состояние, а выход элемента ИЛИ-НЕ 7 - нулевое.

Формула изобретения

Коммутатор по авт. св. Л 572925, отличающийся тем, что, с целью расширения функциональных возможностей, в него введены два инвертора, два сдвигающих регистра, два элемента ИЛИ-НЕ и тина «логическая единица, к первой входной шине подключены вход первого инвертора, первый вход первого элемента ИЛИ-НЕ и синхронизирующий вход второго сдвигающего регистра, к второй входной щине подключены вход второго инвертора, первый вход второго элемента ИЛИ-НЕ и синхронизирующий вход первого сдвигаюнхего регистра, информационные входы сдвигающих ре1истров объединены и подключены к шине «логическая единица, установочный вход первого сдвигающего регистра соединен с выходом первого инвертора, а выход этого регистра с вторым входом первого элемента ИЛИНЕ, выход которого подключен к счетному входу первого счетчика, при этом счетный вход второго счетчика соединен с выходом второго элемента ИЛИ-НЕ, который своим вторым входом подключен к выходу второго сдвигающего регистра, установочный вход которого соединен с выходом второго инвертора.

Авторы

Даты

1979-05-15—Публикация

1977-05-03—Подача