(54) БЛОК ПРИОРИТЕТА

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для регистрации информации | 1977 |

|

SU711559A1 |

| Двухвходовое устройство приоритета | 1982 |

|

SU1059574A1 |

| Устройство управления прерыванием | 1982 |

|

SU1098001A1 |

| Устройство для защиты электромагнитов печатающей головки телеграфного аппарата | 1985 |

|

SU1354329A1 |

| Счетное устройство с предварительной уставкой кода | 1982 |

|

SU1027832A1 |

| Блок приоритета | 1983 |

|

SU1091162A2 |

| Устройство для управления очередностью обслуживания | 1987 |

|

SU1481765A2 |

| Устройство для управления доступом к магистрали | 1980 |

|

SU935961A1 |

| Устройство для передачи информации | 1989 |

|

SU1700571A1 |

| Преобразователь угла поворота вала в код | 1988 |

|

SU1594689A1 |

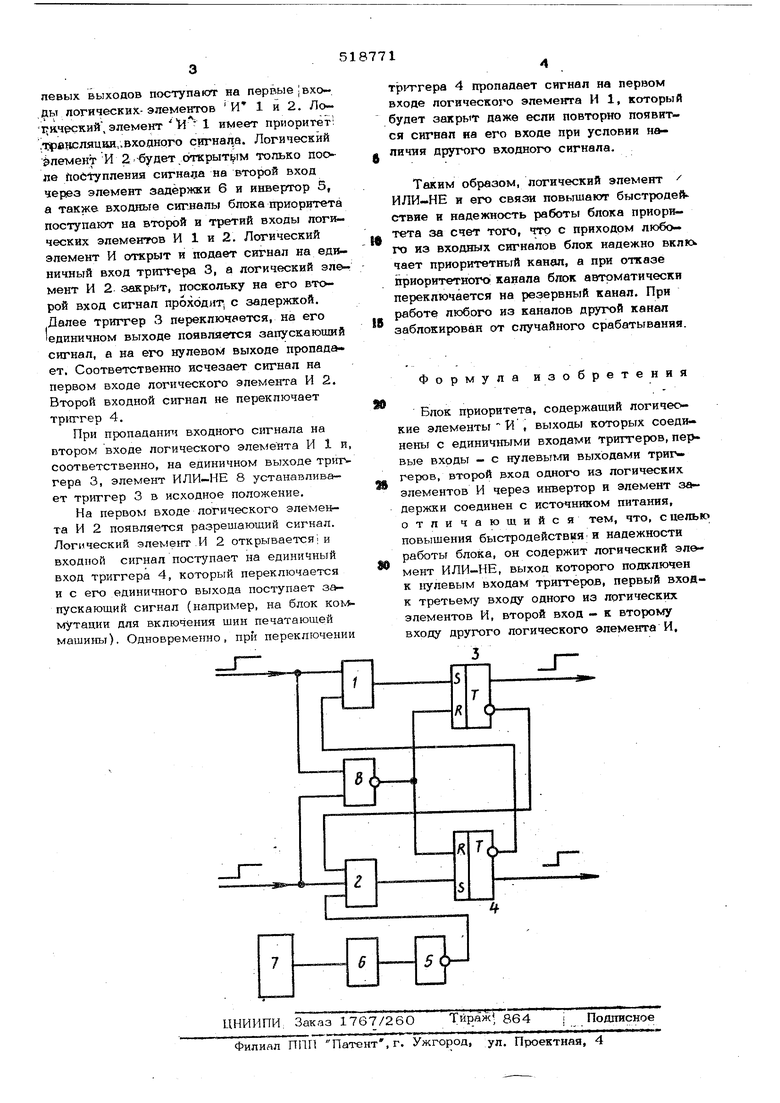

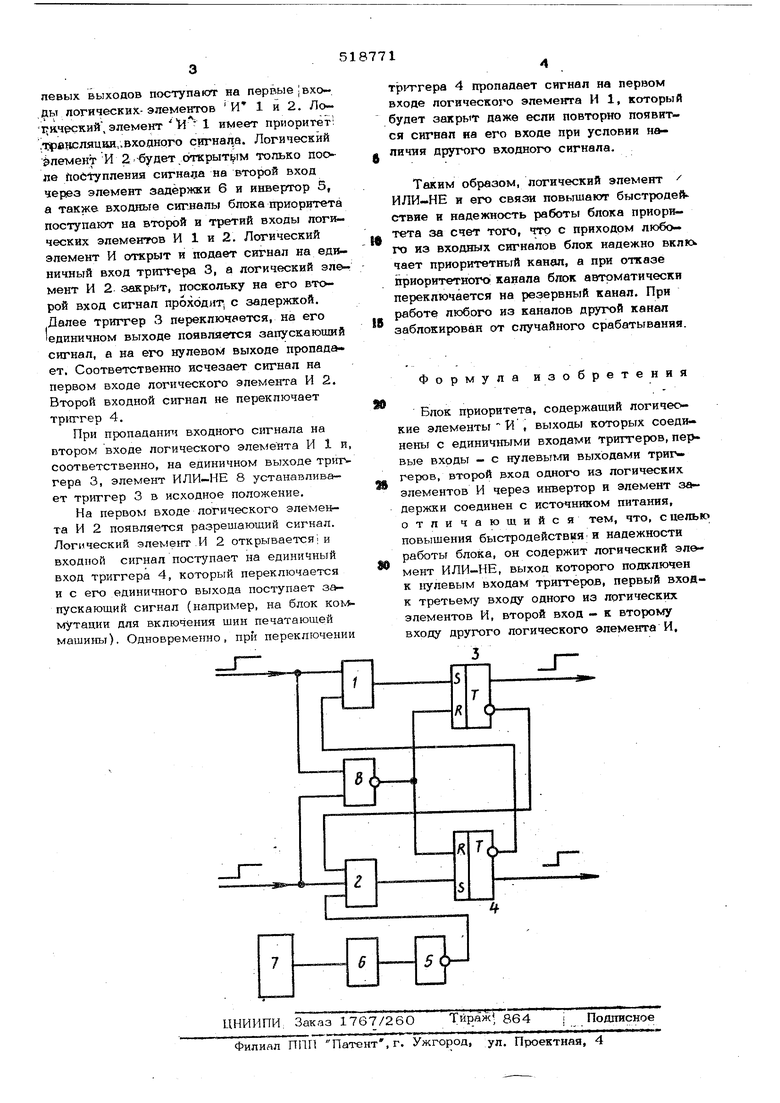

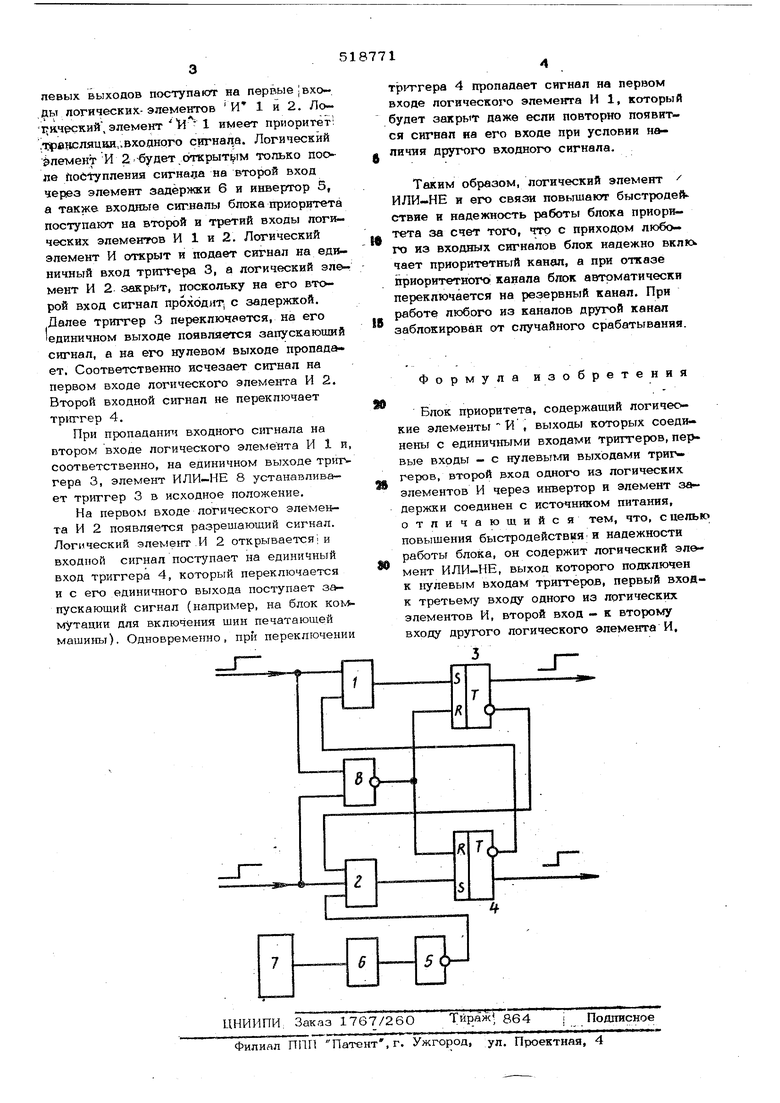

Изобретение относится к aвтo faтиke к вычислительной технике и может быть нспользовано, в частности, в устройствах для управления электрическими печатающи ми машинами. Известен блок приоритета, содержащий логические элементы И, выходы которых соединены с единичными входами триггеров, первые входы - с нулевыми выходами треггеров, второй вход одного из логических элементов И через инвер тор и элемент задержки соединен с источ ником питания. Целью изобретения является повышение быстродействия и надежности работы блока.-/ -: : . Достигается это тем, что блок содержит логический элемент ИЛИ-НЕ, выход которого подключен к нулевым входам триггеров, первый вход - к третьему ду одного из логических -элементов И и второй вход - ко второму входу другого логического элемента И. На чертеже показана функциональная схема блока приоритета. Блок приоритета содержит логические элементы И 1 и 2., выходы каждого из которых соединены с единичными входг - ми соответствующих им триггеров 3 |первь1е входы - с нулевыми выxoдa триггеров 4 и 3, соответственно, второй вход одного из логических элементов И 2 через инвертор 5 и элемент задержки 6 соединен с нсточником питания 7, а так-же блок приоритета содержит логический элемент ИЛИ-НЕ 8, выход которого подключен к нулевым входам; триггеров 4 и 3, а входы соединены: один - с третьим входом логического элемента И 2 и с первым входом блока, другой - с вторым входом логического элемента И 1 и с вторым входом блока. Блок приоритета работает следующим образом. При включении блока питания любой из входных сигналов (например, готовности , из резервированных печатающих электрических машин - на рисунке не показано) через .логический элемент ИЛИ-. НЕ 8 устанавливает триггеры 6 н 4 в исходное положение, а сигналы с их нулевых выходов поступают на первые JBXO ы логических-эпементов И 1 и 2. Ло1;ический элемент И 1 имеет приоритет: .т:)в1К;ляц ш,;входнрго сигнапа. Логический Элемент И 2-будет открыт ш только после йобТупления сигнала на второй вход через элемент задержки б и инвертор 5, а также входные сигналы блока приоритета поступают на второй и третий входы логических элементов И 1 и 2. Логический элемент И открыт и подает сигнал на единичный вход триггера 3, а логический элемент И 2 закрыт, поскольку на его второй вход сигнал проходиТ; с задержкой. Далее триггер 3 переключается, на его единичном выходе появляется запускающий сигнал, а на его нулевом выходе пропадает. Соответственно исчезает сигнал на первом входе логического элемента И 2. Второй входной сигнал не переключает триггер 4.

При пропаданш входного сигнала на втором входе логического элемента И 1 и, соответственно, на единичном выходе триг гера 3, элемент ИЛИ-НЕ 8 устанавпива- ет триггер 3 в исходное положение.

На первом входе логического элемента И 2 появляется разрешающий сигнал. Логический элемент .И 2 открывается и входной сигнал поступает на единичный вход триггера 4, который переключается и с его единичного выхода поступает запускающий сигнал (например, на блок коммутации для включения шин печатающей машины). Одновременно, при переключении

триггера 4 пропадает сигнал на первом входе логического элемента И 1, который будет закрыт даже если повторно появится сигнап на его входе при условии наличия другого входного сигнала.

Таким образом, логический элемент / ИЛИ-НЕ и его связи повышают быстродействие и надежность работы блока приоритета за счет того, что с приходом любо го из входных сигналов блок надежно вклк чает приоритетный канал, а при отказе 11риорнтетного канала блок автоматически переключается на резервный канал. При работе любого из каналов другой канал заблокирован от случайного срабатывания.

Формула изобретения

Блок приоритета, содержащий логические элементы И , выходы которых соединены с единичными входами триггеров, первые входы - с нулевытли выходами триггеров, второй экод одного из логических элементов И через инвертор и элемент задержки соединен с источником питания, отличающийся тем, что, с целы повышения быстродействия и надежности работы блока, он содержит логический элемент ИЛИ-НЕ, выход которого подключен к нулевым входам триггеров, первый вход- к третьему входу одного из логических элементов И, второй вход - к второму входу другого логического элемента И,

Авторы

Даты

1976-06-25—Публикация

1972-10-09—Подача