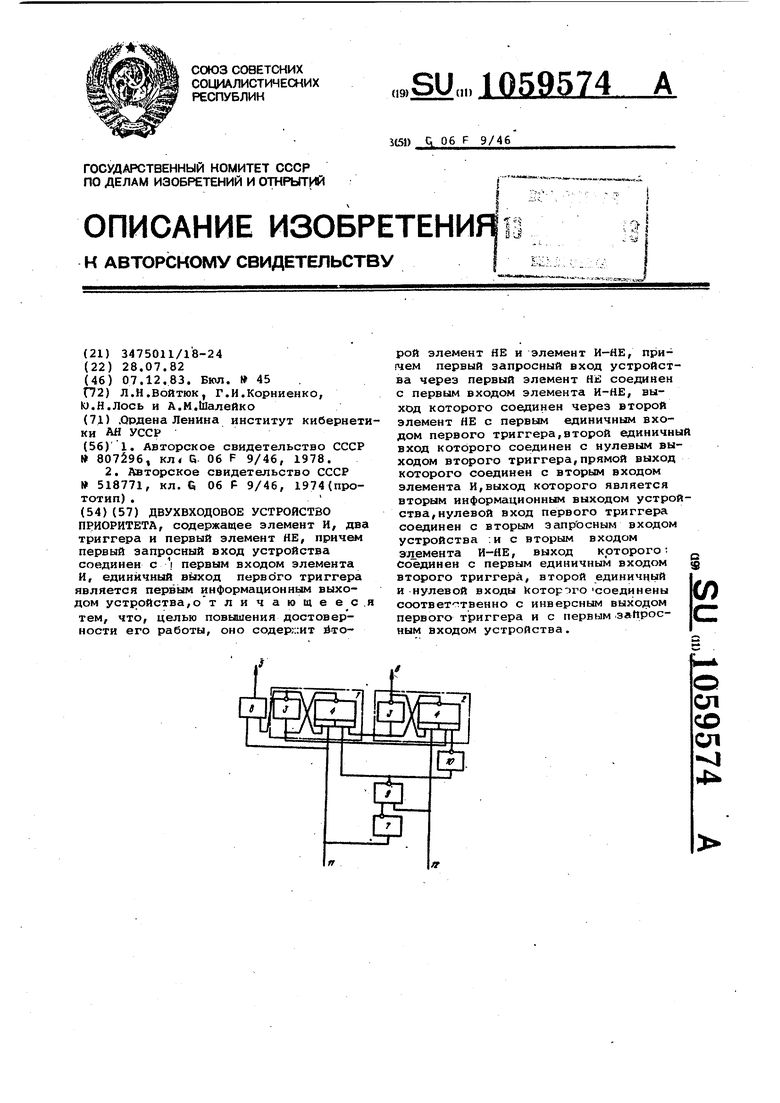

Изобретение относится к цифровой вычислительной технике и может быть использовано в блоках управления ycтpoйcтвa a общего пользования, например общей памятью вычислитель ной системы. Известно .двухвходовоё устройство приоритета(Содержащее .триггер, двазлемента И, элемент задержки и два элемента НЕ,причем прямой выход триггера и выход первого элемен.та И являются выходами устройства ClJ. Недостатком даннбго устройства явпяетс.я высокое быстродействие приоритетного канала, т.е. пришедщему более п&иоритетному запросу необходимо взвести триггер. Наиболее близким к изобретению по техническойсущности является блок приоритета, содержащий элементы И, выходы каждого из которых соединены с единичны-;: входами соответ ствующих им триггеров, первые входы элементов И подключены к, нулевым . выходам триггеров, второй вход одно го из элементов К через инвертор и элемент задержки соединен с источником питания, третий вход элемента И подключен.к входу элемента ИЛИ-НЕ к другому входу которого подключен второй вход другого элемента и, а выход элемент ИЛИ-йЕ связан с нулев ми входами триггеров C2J. Известное устройство характеризуется недостаточной достоверностью работы при одновременном приходе двух запросов . Цель изобретения - повышение достоверности работы устройства. Поставленная цель достигается те что в двухвходовое устройство приоритета, содержащее элемент И, два триггера и первый элемент НЕ, причем первый запросный вход устройств соединен с первым входом элемента И, единичный выход первого триггера является первым информационным выходом устройства, введены второй элемент НЕ и элемент И-НЕ, причем первый запросный вход устройства через первый элемент НЕ соединен с первым входом элемента И-НЕ, выход которого соединен через второй элемент НЕ с первым единичным входом первого триггера, второй единичный вход которого соединен с нулевым вы ходом второго триггера, прямой выход которого соединен с вторым входом элемента И, выход которого явля ется вторым информационным выходом устройства, нулевой вход первого триггера соединен .с вторым запросны входом устройства и с вторым входом элемента И-НЕ, выход которого соеди нен, с первым единичным входом второ го триггера, второй единичный и нулевой входы которого соединены соответственно с.инверсным выходом первого триггера и с первым запросным входом устройства. На чертехке приведена структурная схема устройства. Устройство содержит триггеры.1 и 2, каждый из которых содержит элемент НЕ, 3 и элемент 2И-ИЛ.И-НЕ 4, информационные выходы 5 И-й устройства, элемент НЕ 7, элемент И 8, элемент И-НЕ 9, элемент НЕ 10 и заnpocHiae входцл 11 и 12 устройства. Устройство работает Следующим образом. В: исходном сос- оянии на входы 11 и 12 устройства -поступают сигналы логических нулей. Сигналы логичес-, ;ких нулей, поступая на нулевые входы первого . и второго триггеров, устанавливают их в нулевой состояние, Сигнал логического нуля с входа 12 устройства поступает однбвре.менно на вход зц&лекч-а И-НЕ 9, Сигнал логической единицы с входа элемента И-НЕ 9 поступает на первый единичный вход триггег а 1. На второй еди.ничный вход триггера 1 поступает сигнал логической единицы с Нулевого выхода триггера 2, При совпадении сигналов e,tyiниц. на первом и втором входах триггера 1 он.переключается в единичное состояние. Сигнал нуля а нулевого выхода триггера поступает на первый единичный вход триггера 2, запрещая ему переключаться в единичное состояние. Сигнал логической единицы, с единичного выхода триггера 1 посту.пает на вход элемента И 8, разрешая работать первому каналу. Если на вход 1. устройства поступит-сигнал логической единицы, то с- нулевого входа триггера 1 снимается сигнал установки в нуль этого триггера. Сигнал с входа Ц устройства поступает на вход элемента И 8 и элемента НЕ 7. Сигнал нуля с выхода НЕ элемента 7 поступает на вход элемента И-НЕ 9, на выходе которого вырабатывается сигнал логической единицы. Состояние первого и второго триггеров на изменяется, и на выход, 5 устройства поступает сигнал, разрешающий работать первому каналу. Если после этого на вход 12 устройства поступает сигнал логической единицы, то с нулевого входа триггера 2 снимается сигнал.установки в нуль триггера, i|o состояние триггеров не изменится и устройство приоритета разрешит работать первому каналу. .После окончания работы первого канала на вход 11 ус±ройства поступает сигнал логического нуля, который передается на входы элемента И S элемента НЕ 7 и нулевой вход триггера 1, На выход 5 устройства поступает сигнал логического нуля. Сигнал единицы с выхода элемента НЕ 7, поступая на вход элемента . И-НЕ 9,совпадает .с сигналом единицы, поступающим с входа 12 устройст ва на вход элемента И-НЕ 9; на выходе элемента И-НБ 9 вырабатывает ся сигнал логического нуля, котог рый поступает на первый единичный вход первого триггера и блокирует установку его в единичное состояние Под действием сигналов нуля, поступающего с входа 11, триггер 1 пере ключается Б нулевре состояние. Кроме того, сигнал нуля с выхода эл мента И-НЕ 9 через элемент НЕ 10 пер ключается триггер 2 в единичное состояние, досле чего сигнал нуля с нулевого выхода триггера 2 блокирует установку в единичное состояние триг гера 1, а сигнал единицы, поступая на выход 6 устройства, разрешает работу второго канала. Состояние триггера устройства приоритета изменится только тогда, когда второй канал закончит работу и на вход 12 устрйства поступает сигнал нуля. Если на входы 11 и 12 устройства одновременно поступят сигналы логических единиц, то с нулевых входов первого и второго триггеров будут сняты сигналы установки внуль. Сигнал логической единицы с входа 11 устройства поступает на входы элемен та И 8 и элемента НЕ 7 г с выхода которого сигнал логического нуля поступает на вход элемента И-НЕ 9. Сигнал логическра единицы с выхода элемента .И-НЕ 9 Поступает на вход элемента НЕ 10, с выхода которого сигнал логического нуля, поступая иг. второй вход триггера 2,запрещает переключение его в единичное состояние. Сигнал логической единицы с выхода элемента И-НЕ .9,поступая на первый единичный вход триггера 1,переключает его в единичное состояние, и на вход элемента И 8 поступает сигнал логической единицы. Элемент И 8 подключает к выходу 5 устройства сигнал,логической единицы, V который разрешает работу первому каналу, СостЪяниЬ триггеров не изменится до тех пор, пока первый канал не закончит работу и на вход 11 устройства не поступит сигнал логического нуля. Применение изобретения позволяет повысить достоверность работы устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное устройство приоритета для подключения к общей магистрали | 1990 |

|

SU1735849A2 |

| Многорежимное устройство приоритета | 1990 |

|

SU1805469A1 |

| Многоканальное устройство приоритета для подключения к общей магистрали | 1990 |

|

SU1749896A2 |

| Асинхронное приоритетное устройство | 1986 |

|

SU1336002A1 |

| Многоканальное устройство для управления очередностью запросов | 1987 |

|

SU1444767A1 |

| Двухвходовое устройство приоритета | 1987 |

|

SU1495798A2 |

| Многоканальное устройство для управления обслуживанием запросов | 1988 |

|

SU1552183A1 |

| Многоканальное устройство приоритета | 1983 |

|

SU1148030A1 |

| МНОГОКАНАЛЬНОЕ УСТРОЙСТВО ПРИОРИТЕТА | 1992 |

|

RU2108618C1 |

| Многоканальное устройство приоритета | 1979 |

|

SU822185A1 |

ДВУХВХОДОВОЕ УСТРОЙСТВО ПРИОРИТЕТА, содержащее элемент И, два триггера и первый элемент НЕ, причем первый запросный вход устройства соединен с i первым входом элемента И, единичный выход первого триггера является первым информационным выходом устройства, от личающеес.я тем, что, целью повышения достоверности его работы, оно содер;::ит йторой элемент НЕ и элемент И-НЕ, примем первый запросный вход устройства через первый элемент НЕ соединен с первым входом элемента И-НЕ, выход которого соединен через второй элемент НЕ с первым единичным входом первого триггера,второй единичный вход которого соединен с нулевым выходом второго триггера,прямой выход которого соединен с вторым входом элемента И,выход которого является вторым информационным выходом устройства, нулевой вход первого триггера соединен с вторым эапросным входом устройства .и с вторым входом элемента И-НЕ, выход которого; соединен с первым единичным входом второго триггера, второй единичный и -нулевой входы Которого соединены соответственно с инверсным выходом С первого триггера и с первым .sattpocным входом устройства. ел 01 ppil.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Авторское свидетельство СССР , кл« G 06 F 9/46, 1978 | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Блок приоритета | 1972 |

|

SU518771A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1983-12-07—Публикация

1982-07-28—Подача