1

Изобретение относится к вычислитель ной технике и может быть исполь зовано присоздании микропроцессор Ш1х систем, использующих магистральный принцип связи.

Известно устройство управления доступом к магистрали, содержащее блок приоритета, выход которого подключен ко входам дешифратора, выходами соединенного с информационными входами запоминающего регистра, управляющий вход к о- торого подключен к источнику синхронизирующих сигналов. На входы блока приоритета поступают сигналы запроса доотупа к магистрали, а с выходов запоминающего регистра--выдаются сигналы подтверждения доступа к магистрали ij.

Недостатками известного устройства являются необходимость синхрокизашга к низког быстродействие, определяемое чаототой синхронизации.

Наиболее близким по технической сущности к предлагаемому изобрететпо является многоканальное устройство приоритета, содержащее элемент И-НЕ, а в каж- . дом канале - , элемент ИЛИ, элемент ИЛИ-НЕ и элемент И, причем гасящий вход триггера соединен с соответствующим входом группы входов устройства, установочный вход триггеров каналов, кроме первого, соединен с выходом триггера предыдущего канала, выход элемента ИЛИ каждого канала, кроме первого, соединен с первым вхо10дом элемента ИЛИ предыдущего канала, прямой выход триггера последнего канала и выход элемента ИЛИ первого ка - нала через элемент И-НЕ соединен с установочным входом триггера первого ка15нала, а первый вход элемента ИЛИ пос-леднего канала соединен с первым входом устройства, инверсный выход и установочный вход триггера канала через эл&мент ИЛИ-НЕ канала соединен с первым

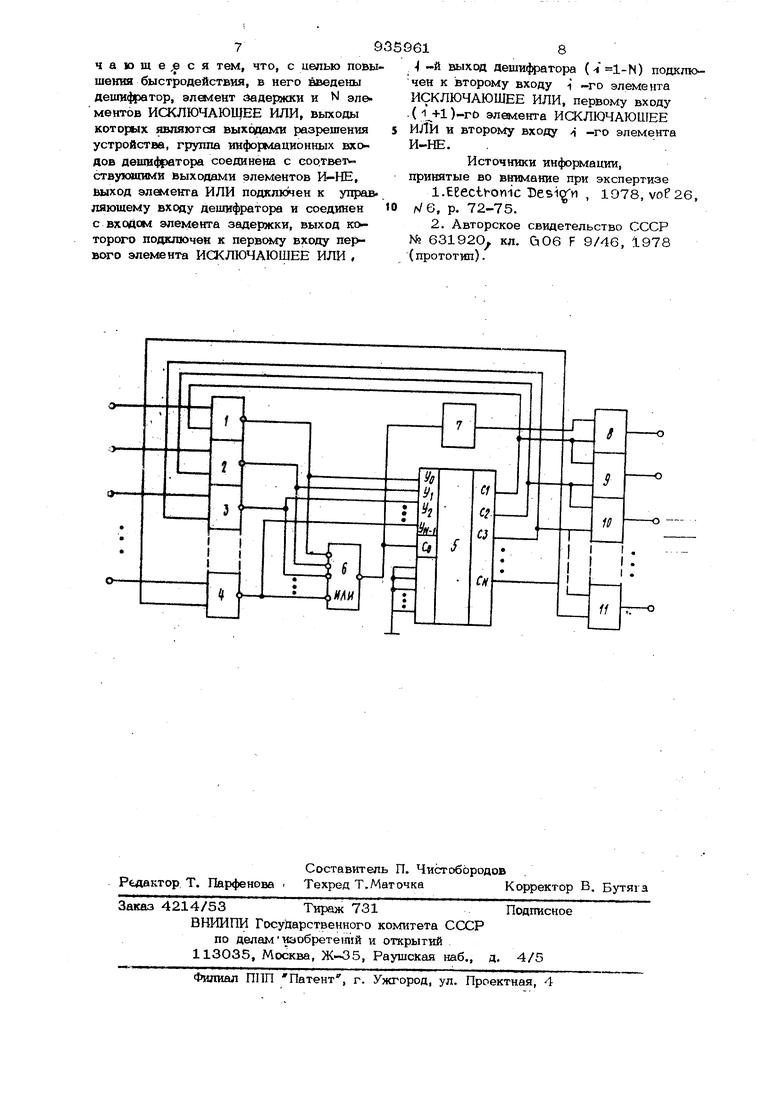

20 входом элемента И канала и соответствующим-вход ом запускающего элемента ИЛИ, выход элемента И канала соединен с соответствующим выходом гругаты устройства, а вход-выход, вход и выход коммутатора соединены соотвеч ственно с шняой обмена, с ввыходом запускающего элемента ИЛИ я со вторыми Екода ш элементов И каналов 2j. Недостатком известного устройства, йшяется то, что с увеличением числа запросов к обмену, быстродейст еие ул ройства снижается пропоршюнально «шел/ этих входов я время появления сигнала ва И --ом выходе подключения источника информации относительно появ ления сигнала на я рм входе запроса к обмену в Н раз больше, чем у первого в4«хода подключения источника информации. Целью изобретения является увеличе-- ние быстродействия устройства. Поставпенгыля цепь достигается тем, что .в устройство для управления досту пом к магистрали, содержащее N эл&ментов И-НЕ, зпеменг Ш1И, выхош г которого подключены к выходам элементов И-НЁ, первые входы элементов И-НЕ являются входами запроса устройства, введены дешиф|штор, элемент задержки и N элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, БыхоДь которых яишются выходами разрешения устройства, группа ин(} рм&пионных входов дешифратора соединена с соответ ствуюшими выходами элементов И-НЕ, выходы элемекга ИЛИ подключнйы к управляющему входу дешифратора к ко входу элемента задержки, выход которог подключен к первому входу первого элемента ИСКЛЮЧАЮШЕЕ ИЛИ, -и выход дешифратора (i 1 - N) подключен ко второму входу 1 ,-fo элемента ИСКЛЮ ЧАЮШЕЕ ИЛИ, первсжу входу f +j -г элемента ИСКЛЮ -1АЮШЕЕ ИЛИ и втором входу 1-го элемента И-НЕ. На чертеже представлена блок- :хвма предлагаемого устройсгеа.; Устройство содержит элементы И-НЕ , выход каждого из которых подклкнен к соответствующему входу гру пы информационных входов дешифратора 5 и ж соответствующему входу элемента ИЛИ 6, выход которого соединен с упра& ляющим входом дешифратора 5 и со вхо дом блока задержки 7, выход последнего подключен к одному из бходов элемента, ИС1 ЛЮЧАЮЩЕЕ ИЛИ 8, первый выхОд дешифратора 5 подключен ко второму вхо ду элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 8, к aiepBOMy входу элемента ИСКЛЮЧАЮ UEE ИЛИ 9 м к одному вз входов элемента И-НЕ 1, второй выход деши4$)атор 9 14 5 соединен со вторым входом элемента СКЛЮЧАЮШЕЕ ИЛИ 9, к первому вхоу элемента ИСКЛЮЧАЮШЕЕ ИЛИ 10 и к одному из входов элалента И-НЕ 2, третий выход деши(}ратора подключен ко второму входу элемента .ИСКЛЮЧАЮШЕЕ ИЛИ 10 и к одному из входов элемента И-НЕ 3, -ый выход дешифратора соединен со вторым входом элемента ИСКЛЮЧАЮШЕЕ ИЛИ 11 и с одним .из входов элемента И-НЕ 4, другие входы элементов И-НЕ 1-4 соединены с источниками запросов доступа к магистрали. Предлагаемое устройство работает следующим образом. На входы устройства поступают, например, единичные уровни сигналов запроса доступа к магистрали. Сигналу згtqjoca, поступающ«лу на -f -ый вход, соответствует единичный уровень 17И. -нала на Ч-ом выходе устройства. В случае поступления на входы устройства несколькнх сигналов запроса устройство воспринимает только один из них и формирует только один сигнал подтверждения на выходе. Другие запросы обслуживаются только после снятия обслуживаемого запроса. В исходном СОСТОЯНИИ при отсутствии запросов на доступ к магистрали на первые входы элементов И-Н 1-4 поступают сигналы, соответствующие логическому нулю, при этом на выходах эпемеН тов И-НЕ 1-4 появляются сигналы, соответствующие логической , которые поступают на входы элемента ИЛИ б. На выходе элемента ИЛИ б пояатяется единичный сигнал, который поступает ка управляющий вход и на вход блока задержки 7. Время задержки сигнала в блоке задержки 7 равно времени раопросч-ранения сигнала от управляющего входа. Состояние сигналов на выходах деши(|фатора описываются следующими логическими уравнениями: V С, УО I Со УО У,; . УО у С , у . в соответствии с уравнениями на выходах дешифратора 5 присутствуют единичные сигналы, при этом на выходах элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 8-11 присутствуют нулевые сигналы, что COOTW ветствует отсутствию сигнапов подтверходения доступа к магистрали. Если на вход элемента И-НЕ 1 поступает сигнал запроса поступа к магистрали, то при совпадении единичного уровня этого сигнала с единичным уровнем СИ1 нала, поступающего с выхода дешифратора 5, на выходе элементна И-НЕ 1 формируется нулевой сигнал; который поступает на информационный вход )атора 5 и на первый вход элемента ИЛИ 6, с выхода которого нулевой сигнал поступает на управляющий вход и на вход блока задержки 7. Так как значение первого входа У входит во все уравнения, описывающие сигналы на выходах дешифратора 5, то на всех его выходах при этом присутствуют единичные cwrHatлы, в этом случае на обоих входах элементовь ИСКЛЮЧАЮЩЕЕ ИЛИ 9-11 присутствуют единичные сигналы. На первый вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 8 с выхода блока задержки 7 поступает сиг нал нулевого уровня, а на дру/ой вход, элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 8 с выхода С дешифратора 5 поступает сиг нал единичного уровня, в результате чего на его выходе формируется сигнал единичного уровня, который является ответным сигналом на сигнал, постутюший на вход элемента И-НЕ 1, После снятия сигнаШ запроса доступа к магистрали со входа элемента И-НЕ 1 устройство возвращается в исходное состояние. Если на вход элемента И-НЕ 3 поступает сигнал запроса доступа к магистрали,до снятия сигнала запроса со входа элемента H-4iE 1, тосс выхода элемента И-НЕ 3 снимается сигнал нулевого уров ня, который поступает на информационный вход У дешифратора 5 и на третий вход элемента ИЛИ 6. Появление на входе У дешифратора 5 нулевого сигнала не изменяет состояние сигналов на выходах , С -С дешифартора 5 так как они удер-живаются в единичном состоянии нул&вым сигналом, на его входе Уо. После снятия сигнала запроса на входе элемента И-НЕ 1 сигнал на информационном входе УО дешифратора 5 и на первом входе элемента ИЛИ 6 изменяет свой ypt уровень на единичный. При этом на вт ходе элемента ИЛИ 6 присутствует нулевой сигнал, так как на его .третий вход поступает нулевой сигнал с выхода элемента И-НЕ 3. Согласно логическим уравнениям исигналы на выходах С , CT. дешифратора принимают нулевое зна-. чение, а сигналы на выходах С--С остаются в единичном состоянии. При этом на входы ИСКЛЮЧАЮЩЕЕ ИЛИ 8 поступают нулевые сигналы и на его выходе также появляется нулевой сигнал. На вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 10 поступают сигналы разных уровней и на его выходе появляеться единичный сигнал, который соответ ствует налич 1ю сигнала запроса на входе элемента И-НЕ 3. На вторые входы элементов И-НЕ 2 и И-НЕ 1 поступают нулевые сигналы с выходов С, С дешифратора 5, запрещающие прохождение сигналов, поступающих на первые входы элементов И-НЕ 1, И-НЕ 2, -до тех пор на его входах и Cj, не появятся единичные сигналы Таким образом, если устройство находится в исходном состоянии и на его -i -ый зход поступает сигнал запроса доотупа к магистрали, то на выходах С О. ю.оккяются сигналы нулевого уровня, а .на лыходах С--С остаются сигналы единичного уровня, сигнал подтверждения ,иХ;тупа сформируется на выходе i -го элемента ИСКЛЮЧАЮЩЕЕ ШШ и время появления сигнала подтверждения относ тельно сигнала запроса будет одинаковым для всех выходов. Если дчя снятия сигнала запроса, т. е. до ьозврашр шя устройства в исходное состояние на другие входы запроса поступают сигналы, то и после снятия 1 -ого запросу сигнал подтверждения формирует г ся в ответ на запрос, поступающий на i-H вход устройства. В этом случае обслуживание сигнала осуществляется без возврата устройства в исходное состояние. Запросы с номерами, меньшими i , воспринимаются устройством после возврата его в исходное состоккие, обслуживание начинается с запроса, имеющего млименьший номер. Таким образом, вве.Щ.ние в устройст во -дешифратора, блока задержки, элеменгов ИСЮ1ЮЧАЮЩЕЕ И/Га позволяет . увеличить быстродействие устройства, имеющего N входов, в W раз. Формула изобретения Устройство для управления доступом к магистрали, содержащее N элементов И-НЕ, ИЛИ, входы которого подключены к выходам элементов И-НЕ, первые входы элементов И-НЕ являются входами запроса устройства, о т л и чающе,еся тем, что, с целью повышетш быстродействия, в него ёведены деши4 мтор, элемент задержки и М элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, выходы которых являются выходами разрешения устройства, группа информационных входов дешифратора соединена с еортвет ствуюнгами выходами элементов И-НЕ, Выход элемента ИЛИ подключен к управ, ляюшему входу дешифратора и соединен с входом элемента задержки, выход Kt торого подключен к первсжсу входу первого элемента ИСЖЛЮЧАЮШЕЕ ИЛИ ,

4 -и выход дешифратора () подключен к второму входу -( -го элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, первому входу .(i +D-rO элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и второму входу /i -го элемента И-НЕ.

Источники информации, принятые во внимание при экспертизе

l.EEectKonic Desi(M , 1978, voP26, л/6, p. 72-75.

2. Авторское свидетельство СССР № 63192О, кл, GO6 F 9/46, 1978 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения вычислительных машин с магистралью | 1988 |

|

SU1647576A1 |

| Устройство прерывания | 1982 |

|

SU1084795A1 |

| Многоканальное устройство приоритета для подключения к общей магистрали | 1990 |

|

SU1735849A2 |

| Устройство для сопряжения магистрали ЭВМ с периферийными устройствами | 1990 |

|

SU1751775A1 |

| Устройство приоритетного доступа к магистрали | 1990 |

|

SU1839249A1 |

| Устройство для сопряжения микропроцессора с периферийными устройствами | 1987 |

|

SU1434440A1 |

| Устройство микропроцессорного управления и обработки информации | 1979 |

|

SU947867A1 |

| Многоканальное устройство для обмена данными между модулями вычислительной системы | 1987 |

|

SU1444796A1 |

| Устройство для сопряжения микропроцессорной системы с внешними устройствами с контролем | 1984 |

|

SU1242956A1 |

| Устройство для сопряжения двух ЭВМ | 1989 |

|

SU1649559A1 |

//

НЛИ

ff

Авторы

Даты

1982-06-15—Публикация

1980-08-22—Подача