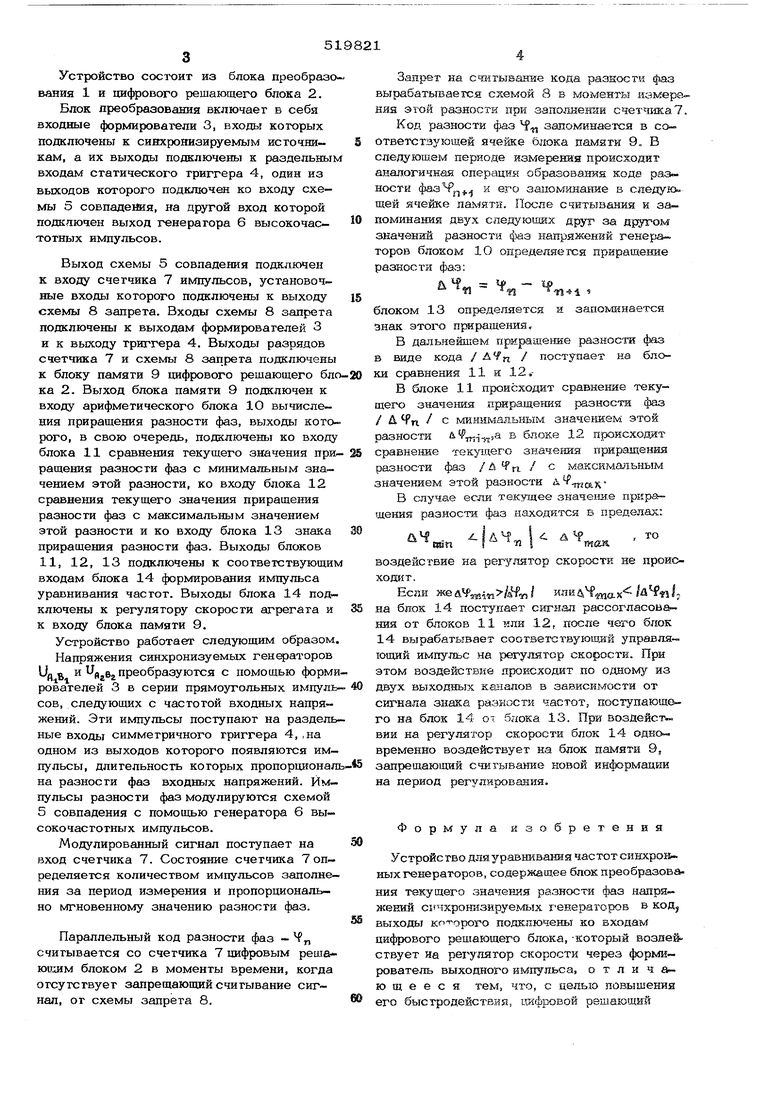

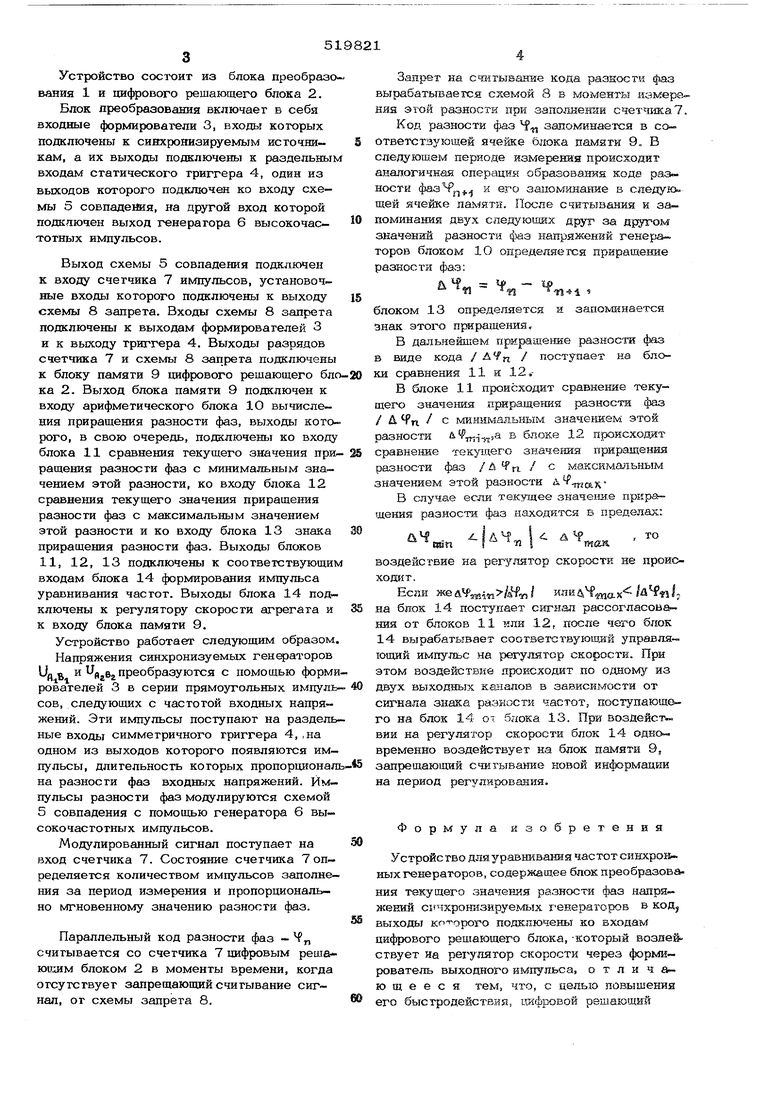

Устройство дпя уравнивания частот относится к области механики регупирования час тоты синхронных генераторов и может быть использовано при синхронизации генераторов переменного тока, в частности судовых син- хронных генераторов. Известны устройства для уравнивания частот синхронных i-енераторов в процессе их синхронизации 1, 2, в которых определение знака разности частот и формирование импул ьса на уравнивание част-от производятся при определенной разности фаз один раз за период разностной частоты. Блил-сайшим аналогом является устройство для выравнивания частот 3 , содержащее блок преобразователя- текущего .значений разнос ги фаз напряжений синхро1шзуемых генераторов в код, выходы которого подключены ко входам цифрового решающего блока, ко горый воздействует на регулятор скорости через формирователь выходного импульс Зто устройство реализуют жесткий ап горЕгм Пропорционального регулирования, что приводит к затягиванию процесса синхронизации, особенно при малых значениях взаимной разности частот генераторов. Целью изобретения является повышение быстродействия системы уравнивания частот генераторов. С этой целью цифровой решающий блок содержит блок памяти, арифметический блок вычисления приращения разности фаз, блоки сравнения этого приращения с минимальным и максимальным значениями разности фаз и блок памяти, подключенный к выходам блока преобразования, выход блока памяти подключен к входу блока вычисления приращения разности фаз, выходы которого подключены к входам блоков сравнения текущего значения разности фаз с IИHИмaльными значениями этой разности и блока знака приратения разности фаз, причем выход этого блока вместе с выходами блоков сравнения подключен к входам блока формирования выходиого импульса, второй выход которого подключен к блоку памяти. На чертеже представлена струк1урная схема устройства. Устройство состоит из блока преобразо вания 1 и цифрового решающего бпока 2. Блок яреобразования включает в себя входные формирователи 3, входы которых подключены к синхронизируемым источникам, а их выходы подключены к раздельным входам статического триггера 4, один из выходов которого подключен ко входу схемы 5 совпадения, на другой вход которой подключен выход генератора 6 высокочастотных импульсов. Выход схемы 5 совпадения подключен к входу счетчика 7 импульсов, установочные входы которого подключены к выходу схемы 8 запрета. Входы схемы 8 запрета подключены к выходам формирователей 3 и к выходу триггера 4. Выходы разрядов счетчика 7 и схемы 8 запрета подключены к блоку памяти 9 цифрового решающего бл ка 2. Выход блока памяти 9 подключен к входу арифметического блока 1О вычисления приращения разности фаз, выходы кото рого, в свою очередь, подключены ко входу блока 11 сравнения текущего значения при ращения разности фаз с минимальным значением этой разности, ко входу блока 12 сравнения текущего значения приращения разности фаз с максимальным значением этой разности и ко входу блока 13 знака приращения разности фаз. Выходы блоков 11, 12, 13 подключены к соответствующим входам блока 14 формирования импульса уравнивания частот. Выходы блока 14 подключены к регулятору скорости агрегата и к входу блока памяти 9. Устройство работает следующим образом Напряжения синхронизуемых ген эаторов Ц В и UfljBj преобразуются с помощью форми рователей 3 в серии прямоугольных импуль сов, следующих с частотой входных напряжений. Эти импульсы поступают на раздель ные входы симметричного триггера 4, ,на одном из выходов которого появляются импульсы, длительность которых пропорционал на разности фаз входных напряжений. Импульсы разности фаз модулируются схемой 5 совпадения с помощью генератора 6 высокочастотных импульсов. Модулированный сигнал поступает на вход счетчика 7. Состояние счетчика 7 определяется количеством импульсов заполнения за период измерения и пропорционально мгновенному значению разности фаз. Параллельный код разности фаз - 4 считывается со счетчика 7 цифровым решающим блоком 2 в моменты времени, когда отсутствует запрещающий считывание сигнал, от схемы запрета 8. Запрет на считывание кода разности шз вырабатывается схемой 8 Б моменты яамераНИИ этой разности при заполнежш счетч1жа7. Код разности фаз запоминается в соответствующей ячейке блока памяти 9. В следующем периоде измерения происходит аналогичная операция образования кода раз носги фаз и его запомина гае в сяедую щей 51чейке памитн. Посяе считывания и за поминания двух следующих друг за другом значений разности фаз напряжений генераторов блоком Ю определяется приращение разности фаз; л f ч -IP t п 41 блоком 13 определяется и загюь/шнается знак этого приращения. В дальнейшем приращение разности фаз в виде кода / I поступает на блоки сравнения 11 и 12,В блоке 11 происходит сравнение текущего значения приращения разности фаз / Д Чп I с минимальным значением этой разности в блоке 12 происходит сравне1ше текущего значения приращения разности фаз / Д f гг / с максимальным значением этой разности .гсе.к В случае если текущее значение приращения разности фаз находится в пределах: DЕ - вйп I- -п i - иак. воздействие на регулятор скорости не происходит. Если же(,/a4V I илидМа аих M%ilj на блок 14 поступает сигнал рассогласова ния от блоков 11 или 12, после чего блок 14 вырабатывает соответствующий управля ющий импульс на регулятор скорости. При этом воздействие яронсходит по одному из двух выходных каналов в зависимости от сигнала знака разности частот, поступающего на блок 14 07 блока 13. При воздействии на регулятор скорости блок 14 одновременно воздействует на блок 9, запрещающий счигываш е новой информации на период регулирования. Формула изобретения Устройс тво ДЛИ уравнивания час тот синхрог-ьных генераторов, содержащее блок преобразования текущего значения разности фаз напряжений сичхронизируемьзх генераторов в код выходы ко орого подключены ко входам цифрювого решающего блока, -который воздействует на рехупятор скорости через формирователь выходного импульса, отличающееся тем, что, с целью повышения его быстродействия, ттифровой решающий

блок содержит блок памяти, арифметический блок вычисления приращения разности фаз, блоки ср авнениз этого приращения с минимальным и максимальным значениями разности фаз и блок знака приращения ра ности фаз, причем входы блока памяти noftключены к выходам блока преобразования, а выход блока памяти подключен к входу блока вычисления прир ащения разности фаз, выходы которого подключены к входам блоков сравнения текущего значения разности фаз с минимальным и максимальным значениями этой разности и блока знака приращения разности фаз, причем выход этого блока вместе с выходами блоков сравнения подключен к входам блока формирования выходного импуль са, второй выход которого подключен к блоку памяти.

Источники информации, принятые во внимание при экспертизе:

1.Авт. св. № 146838 кл. Н О2 J3/42, 1961.

2.Авт. св. № 39489О кл. Н 02 J 3/42, 1971.

3.Авт. св. № 415768 кл. Н 02 J 3/4О, 1971.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство синхронизации генераторов | 1974 |

|

SU531230A1 |

| Устройство для синхронизации генераторов | 1975 |

|

SU553711A1 |

| Устройство для синхронизации генераторов | 1977 |

|

SU687530A1 |

| Устройство для регулирования скорости электродвигателя | 1984 |

|

SU1267375A1 |

| Цифровой функциональный преобразователь | 1980 |

|

SU942034A1 |

| Устройство для уравнивания частот синхронных генераторов | 1979 |

|

SU788271A1 |

| Устройство для автоматическогоРЕгулиРОВАНия чАСТОТы | 1979 |

|

SU838896A1 |

| Устройство для поворота вектора (его варианты) | 1982 |

|

SU1078431A1 |

| Устройство для управления и контроля автономной электроэнергетической установки | 1976 |

|

SU649099A1 |

| Устройство для измерения параметра динамического процесса и управления им с самоконтролем | 1986 |

|

SU1423985A1 |

Авторы

Даты

1976-06-30—Публикация

1974-09-09—Подача