(54) УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ГЕНЕРАТОРОВ

синхронизации, появляется угловая ошибка, которая будет тем больше, чем больше ве- пичина ускорения.

Цель изобретения - псвышение точности включения генераторов на параллельную рабо у.

Указанная цель достигается тем, что в устройстве для синхронизации генераторов, содержащем блок преобразования текущего значения разности фаз напряжений синхрошК зируемых генераторов в код, выходы которого подключены ко входам цифрового решающего блока, который воздействует на автоматический выключатель и с одержит-блок

памяти текущего значения кода разности фаз, связанный с блоком вычисления приращения разности фаз, выход которого подключен к входу блока сравнения текущего и допустимого значений разности фаз, выход которого подключен к выходу цифрового решенощего блока по регулированию частоты, и блок вычисления времени опережения, выход которого подключен ко входу блока запрета по разности напряжений, другой вход которого подключен к выходу блока преобразования, а выходы один - к выходу цифрового решающего блока по регулированию напряжения, а второй - к выходу по включению автоматического выключателя,решающий блок снабжен блоком вычисления кода углового ускорения и блоком вычисления времени ожидания момента совпадения фаз, причем входы блока вычисления кода углО-. вого ускорения поддслючеьш соответственно к выходу блока вычисления приращения раэности фаз и к выходу блока сравнения текущего и допустимого значений разности фаз, а его выход подключен к одному из входов блока вычисления времени ожидания момент сс«падения фаз, друг:ие входы которого подключены соответственно к выходу блока вычисления приращения разности фаз и к выходу блока памяти текущего значения раэности фаз, а выход блока вычисления вреMBira ожидания момента совпадения подключен к входу блока вычисле1шя времени опереже1шя.

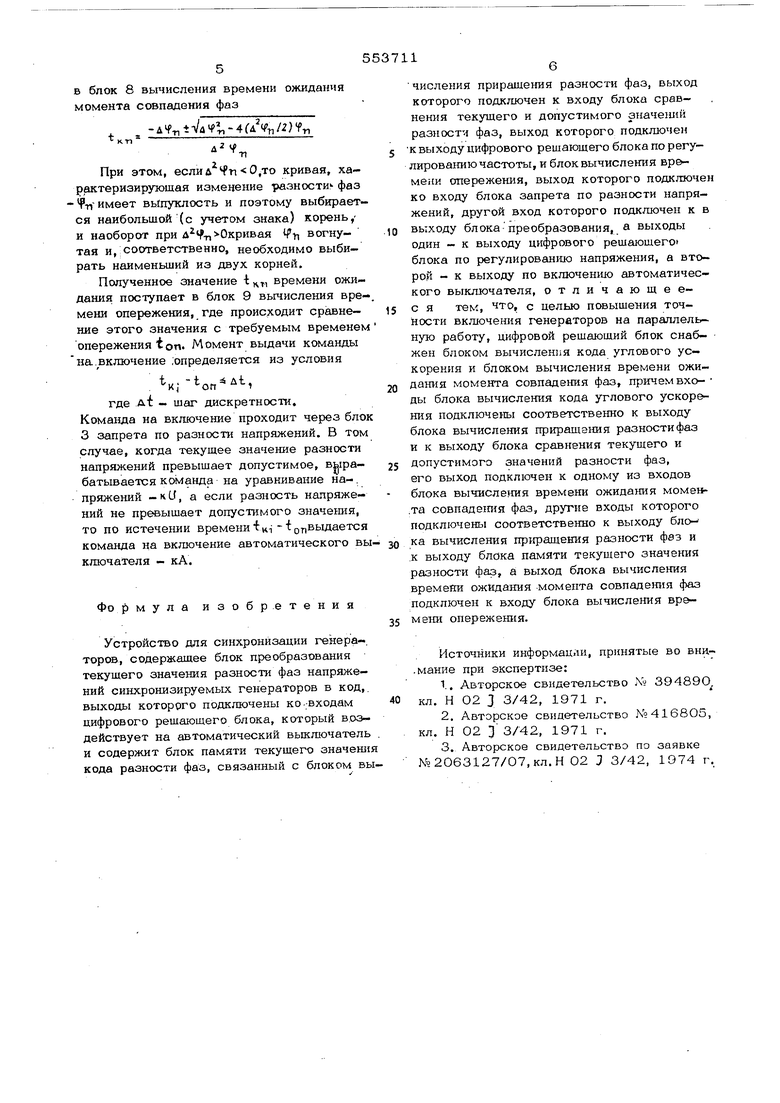

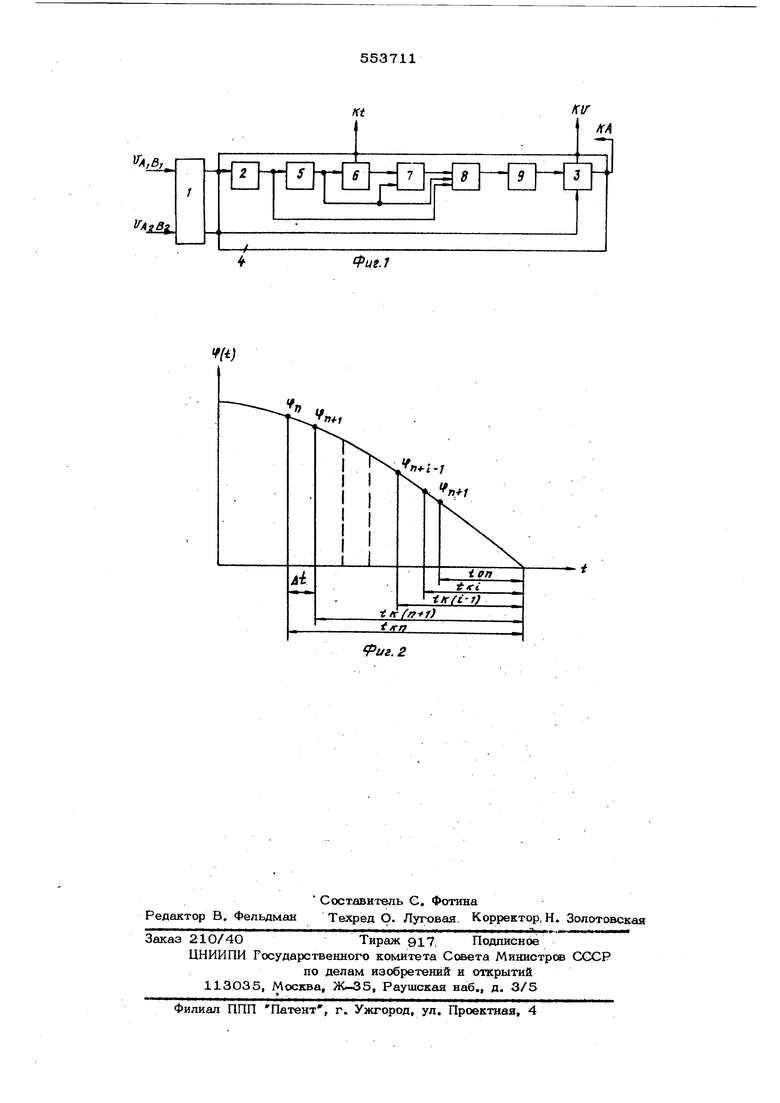

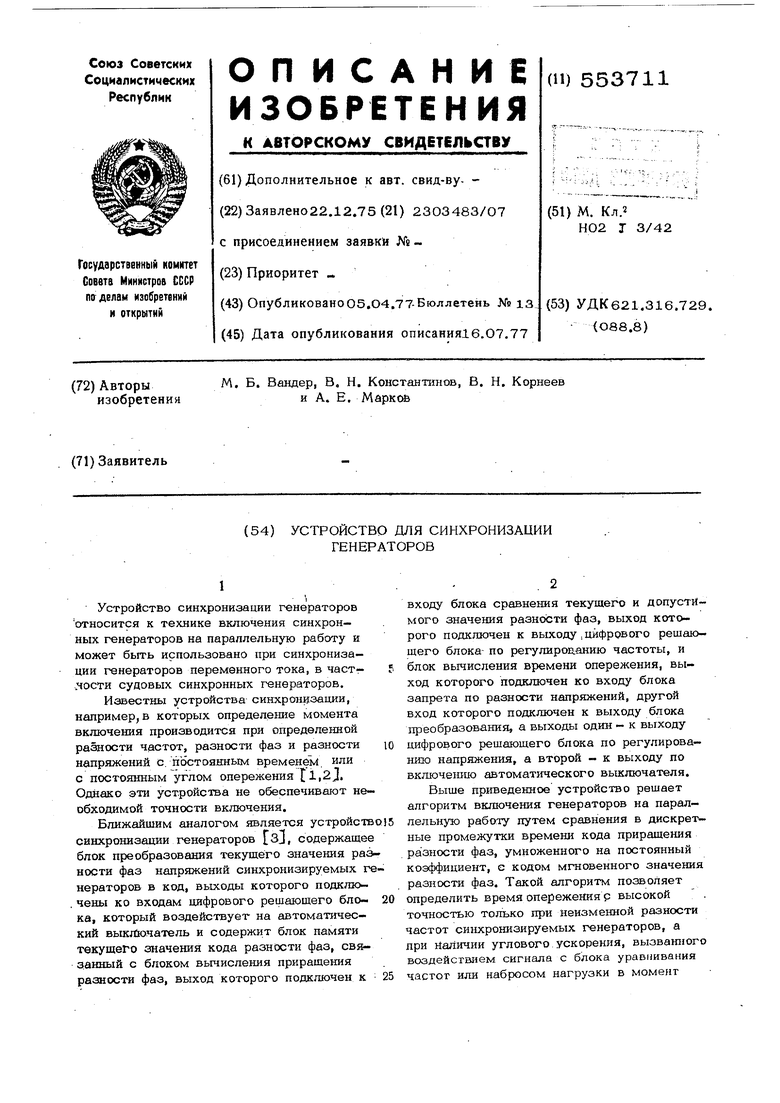

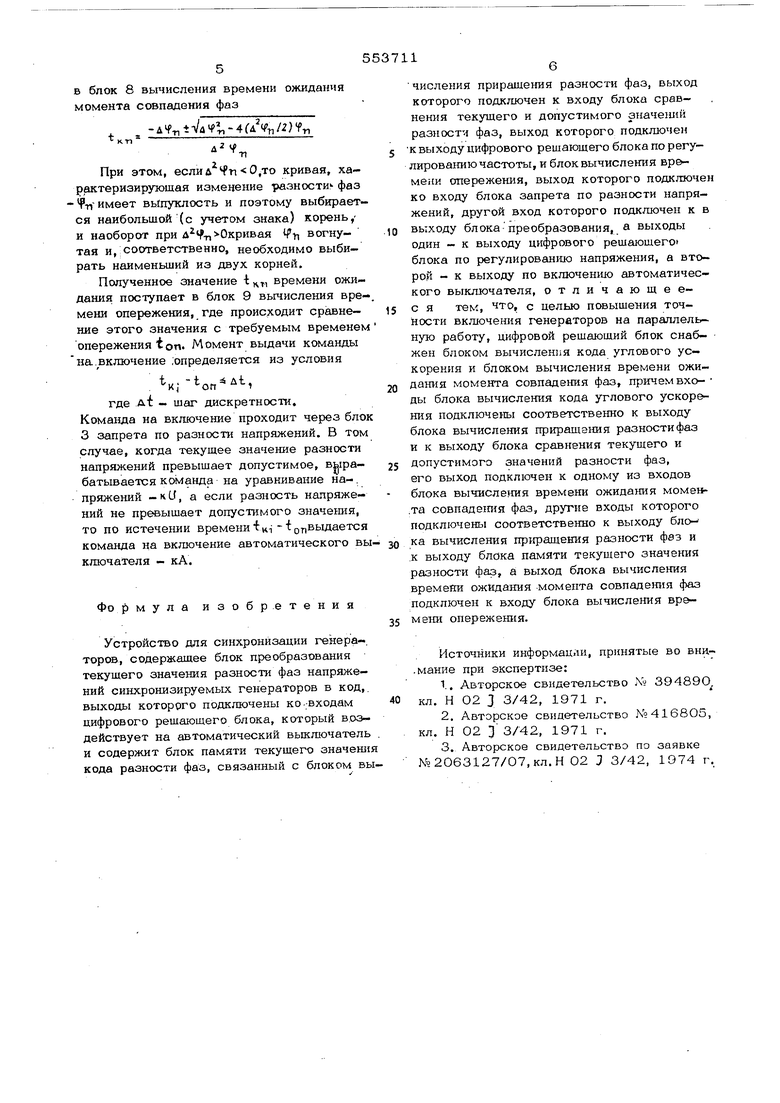

На фиг. 1 представлена структурная схема устройства; на фиг. 2 - диаграмма, поясняющая работу устройства.

Выходы блока преобразования 1 подключены к синхронизируемым источникам. Выход блока преобразования по разности фаз подключен к входу блока памяти 2, а выход по разности напряжений к входу блока 3 запрета по разности напряжений цифрового решающего блока 4. Выход блока памяти подключен к входу блока 5 вычисления кода приращени5 разности фаз, выход которого подключен к входу

блока б сравнения текущего и допустимого значегшй приращения разности фаз, выход которого, в свою очередь, подключен к выходу блока 4 по регулированию чао.тоты. Одновремешю выход блока 5 подключен к входу блока 7 вычисления кода углового ускорения, выход которюго 1 одключен к входу блоку 8 вычисления време ни ожидания момента ссжпадения фаз. Выход блока 8 подключен к входу блока 9 вычисления времени опережения, выход которого подключен ко второму входу блока запрета по разности напряжений. Выходы блока 3 подключены один - к выходу бло- ка 4 по регулирсжанию напряжения, а второй - к выходу блока 4 управления авто- матическим выключателем.

Устройство работает следующим образо

Напряжение синхронизируемых генераторов . AiBi А2В2. преобразуются с помощью блока преобразования в код разности фаз Чт), поступающий в блок памяти 2 и в код А и , пропорциональный разности напряжений, поступающий на вход блока 3 запрета по разности напряжений. Измерение и запоминание кодов происходит в каждом периоде напряжений синхронизируемых генераторов. Таким образом, в блоке памяти 2 запоминается посладо- вательность дискретных значений коде

разности фаз: -n,.,

Значения этих кодов последовательно поступают в блок 5, где производится вычисление приращений разности фаз 3Ja пе риод измерения

Д P -Ч„- f,,,

-nt 1 Ti-n Ti-f i

Полученные коды приращений поступают в блок 6 сравнения текущего и допустим(го значений приращения разности фаз. При превышении допустимого значения блоком 6 вырабатывается команда на уравнивание . частот синхронизируемых генераторов - Kjt.

Одновремеш1о с предыдущей операцией коды приращений разности фаз последсшательно поступают в блок 7 вьлисления кода углового ускорения, в котором происходит вычисление вторых конечных разностей

,,,

,,,-д,,,,,

Конечные разности первого и второго порядка вместе с соответствующими значениями кодов разности фаз Рп поступают Б блок 8 вычисления времени ожидания момента совпадения фаз .-4UЧ/г)Ут При этом, еслий ,то кривая, характеризируюшая изменение ра-зности фаз - п имеет выпуклость и поэтому выбирает ся наибольшой (с учетом знака) корень,и наоборот при д Рп Окривая Vti вогнутая и, соответственно, необходимо выбирать наименьший из двух корней. Полученное значение i л времени ожидания поступает в блок 9 вычисления вре мени опережения, где происходит сравнение этого значения с требуемым времене опережения t on. М омент выдачи команды на.включение ;определяется из условия . где At шаг дискретности, Команда на включение проходит через бло 3 запрета по разности напряжений. В том случае, когда текущее значение разности напряжений превышает допустимое, вырабатывается команда на уравнивание на-. пряжений - к Lf, а если разность напряжений не пр ышает допустимого значеьшя, то по истечении времени t кт оп ыдается команда на включение автоматического вы ключателя - кА, Фо р и у п а изобретения Устройство для синхронизации генера- торов, содержащее блок преобразования текущего значения разности фаз напряжений синхронизируемых генераторов в код, выходы которого подключены ко-входам цифрового решающего блока, который в.оздействует на автоматический вьпслючатель и содержит блок памяти текущего значени кода разности фаз, связанный с блоком вы числения приращения разности фаз, выход которого подк почен к входу блока сравнения текущего и допустимого значат разности фаз, выход которого подключен к выходу цифрового решающего блока по регулировахшю частоты, и блок вычисления времени опережения, выход которого подключен ко входу блока запрета по разности напряжений, другой вход которого подключен к в выходу блокапреобразования, а выходы один - к выходу цифрового решающего блока по регулированию напряжения, а второй - к выходу по включению автоматического выключателя, отличающеес я тем, что, с целью повышения точности включения генераторов на параллельную работу, цифровой решающий блок снабжен блоком вычисления кода углового ускорения и блоком вычисления времени ожидашш момента совпадения фаз, причем вхо- ды блока вычисления кода углового ускорения подключены соответственно к выходу блока вычисления приращэния разности фаз и к выходу блока сравнения текущего и допустимого значений разности фаз, его выход подключен к одному из входов блока вычисления времени ожидания .та совпадезшя фаз, другие входы которого подключены соответственно к выходу блока вычисления пр фащения разности фаз и .к выходу блока памяти текущего значения разности фаз, а выход блока вычисления времени ожидания -момента совпадения фаз подключен к входу блока вычисления времени опережения. Источники информац.ш, принятые во вни.мание при экспертизе: .. Авторское свидетельство Х 304890 кл. Н 02 3 3/42, 1971 г. 2.Авторское свидетельство №416805, кл. Н 02 3 3/42, 1971 г. 3.Авторское свидетельство по заявке КЬ2О63127/07,кл.Н 02 3 3/42, 1974 г.

Kir

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для синхронизации генераторов | 1977 |

|

SU687530A1 |

| Устройство синхронизации генераторов | 1974 |

|

SU531230A1 |

| Устройство дя уравнивания частот | 1974 |

|

SU519821A1 |

| Устройство для синхронизации генераторов | 1971 |

|

SU471637A1 |

| Устройство для синхронизации генераторов переменного тока | 1980 |

|

SU983892A1 |

| Устройство для включения на парал-лЕльНую РАбОТу гЕНЕРАТОРОВ пЕРЕМЕННО-гО TOKA | 1979 |

|

SU817860A1 |

| Устройство для автоматической синхронизации | 1983 |

|

SU1094106A1 |

| Устройство для уравнивания частот синхронных генераторов | 1979 |

|

SU788271A1 |

| Цифровой синхронизатор | 1978 |

|

SU736267A1 |

| Синхронизатор с постоянным временем опережения | 1990 |

|

SU1771034A1 |

n+i-j

ЛЧ/

иг.2

Авторы

Даты

1977-04-05—Публикация

1975-12-22—Подача