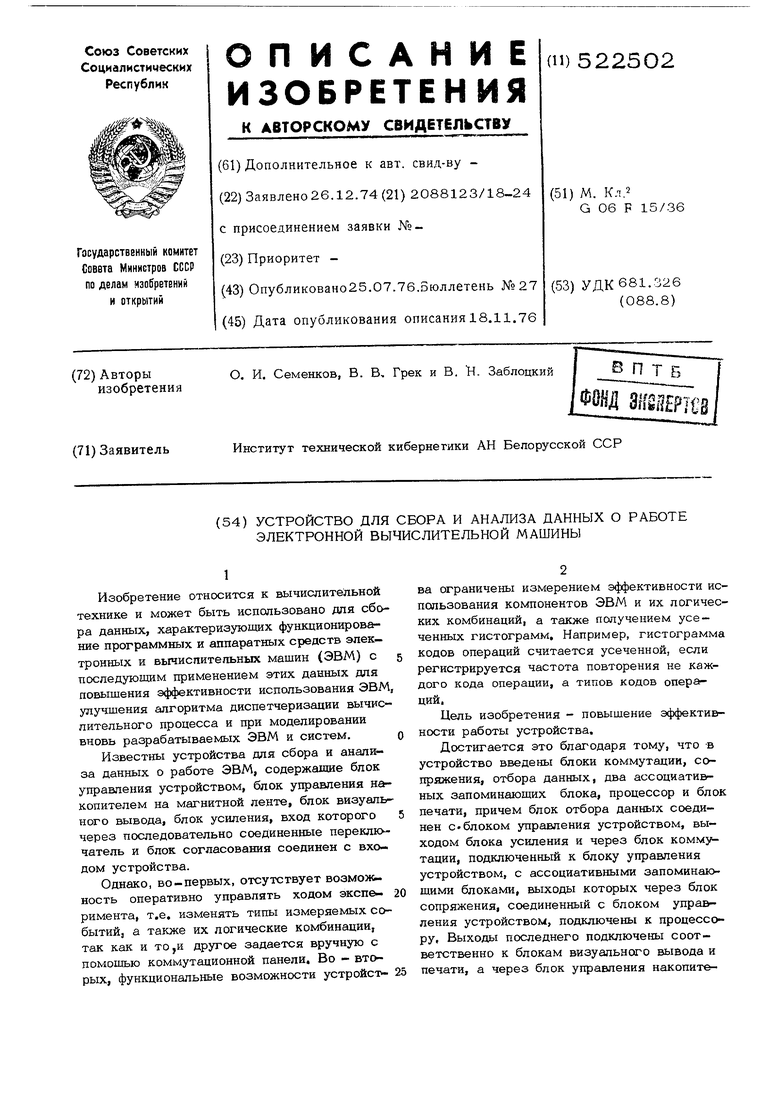

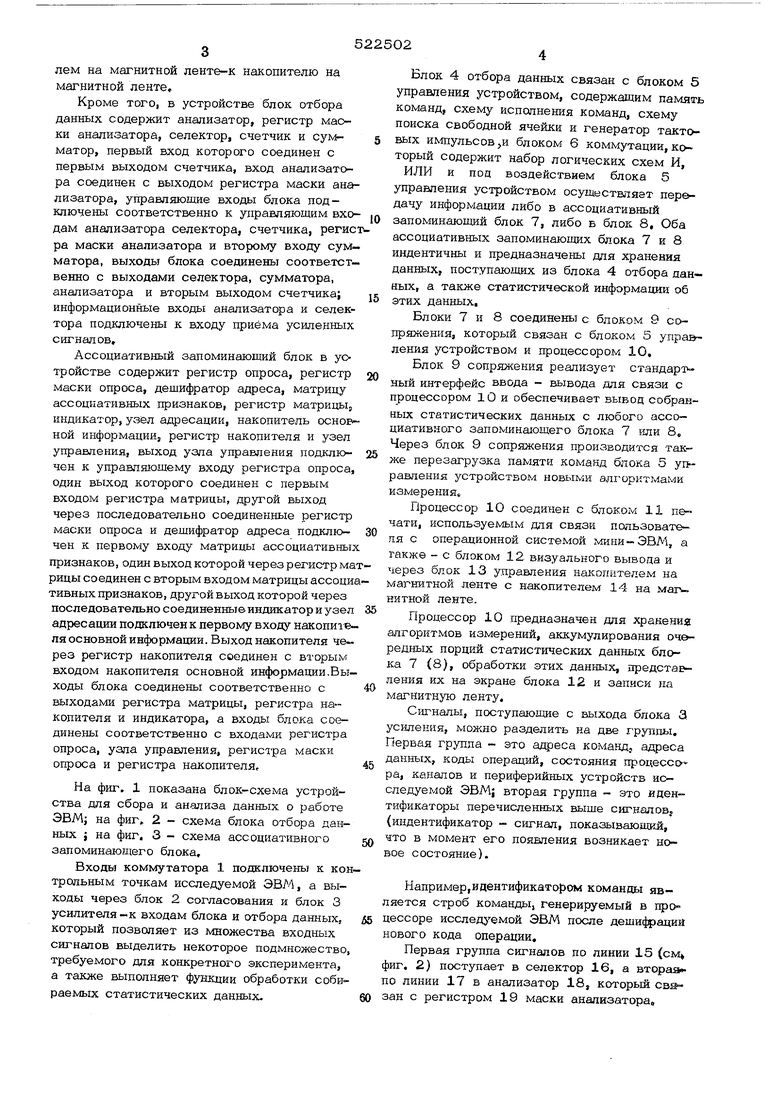

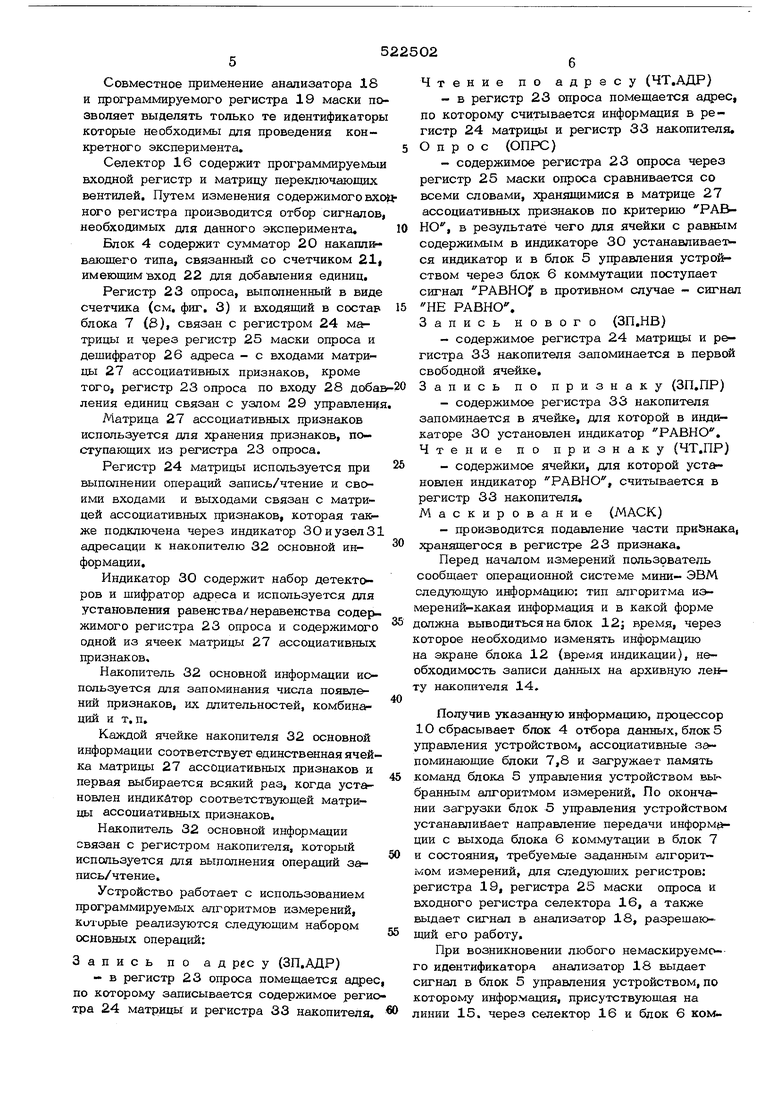

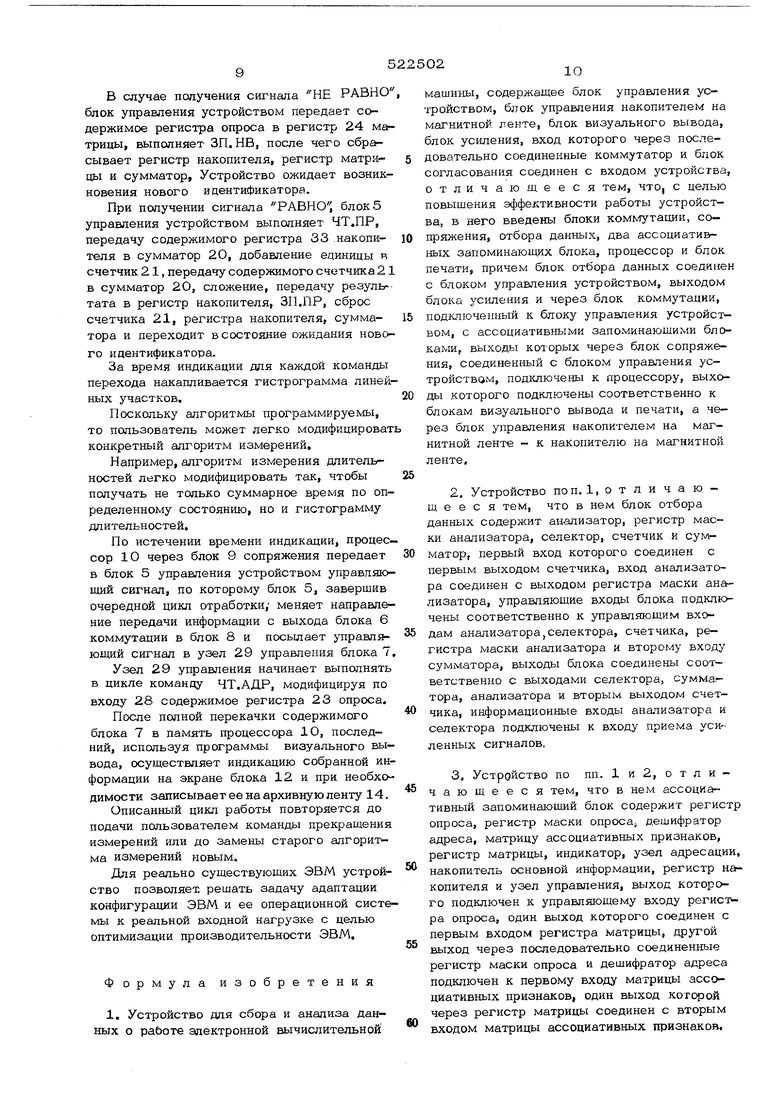

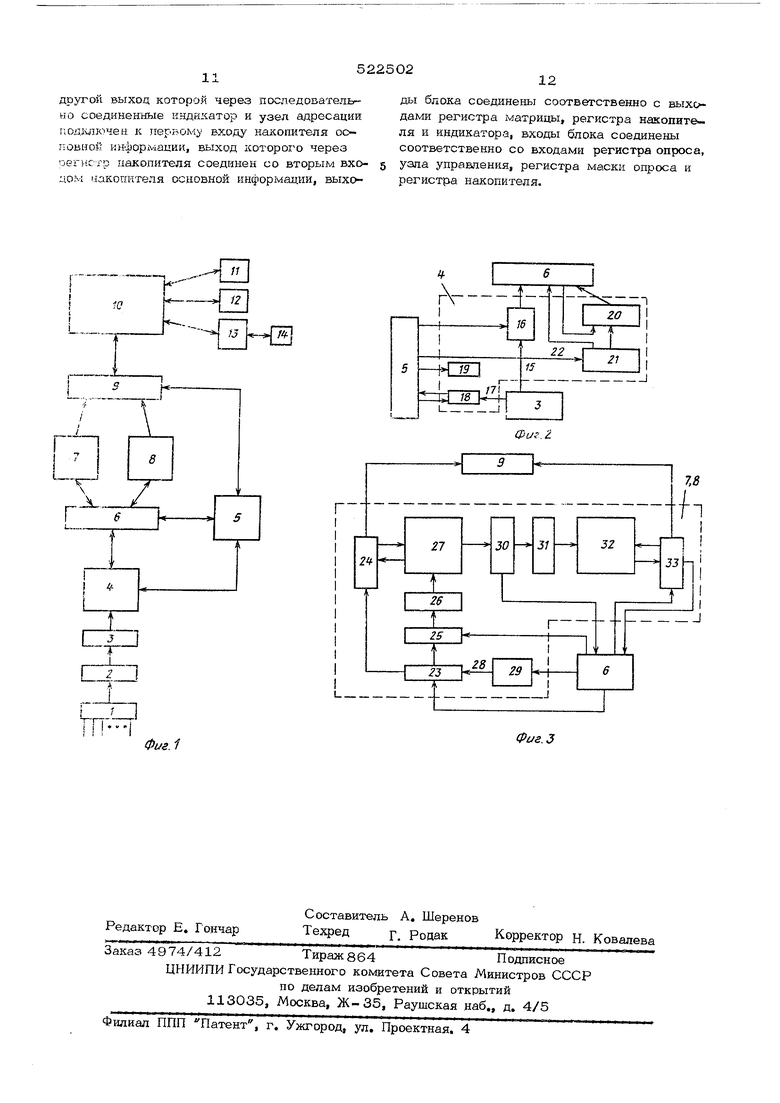

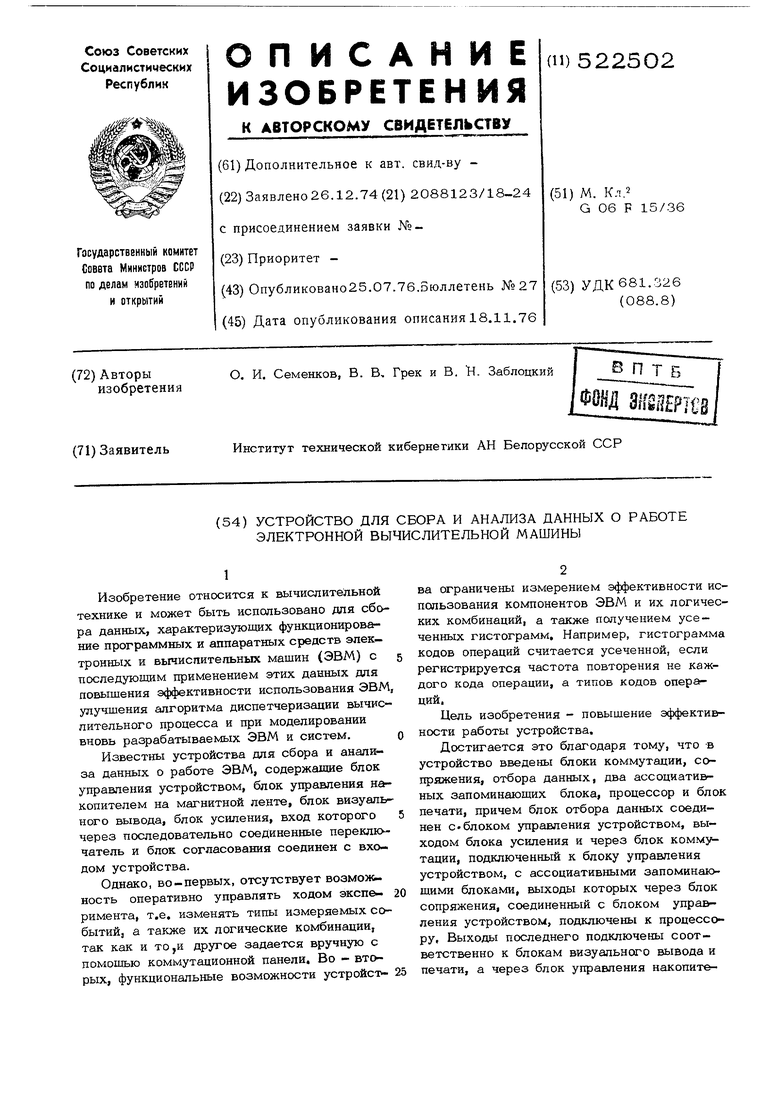

лем на магнитной ленте-к накопителю на магнитной ленте Кроме того, в устройстве блок отбора данных содержит анализатор, регистр маски анализатора, селектор, счетчик и сумматор, первый вход которого соединен с первым выходом счетчика, вход анализатора соединен с выходом регистра маски анализатора, управляющие входы блока подключены соответственно к управляющим входам анализатора селектора, счетчика, регис ра маски анализатора и второму входу сумматора, выходы блока соединены соотве.тственно с выходами селектора, сумматора, анализатора и вторым выходом счетчика; информационные входы анализатора и селектора подключены к входу приёма усиленных сигналов. Ассоциативный запоминающий блок в устройстве содержит регистр опроса, регистр маски опроса, дешифратор адреса, матрицу ассоциативных признаков, регистр матрицы, индикатор, узел адресации, накопитель основ ной информации, регистр накопителя и узел управления, выход узла управления подключен к управляющему входу регистра опроса, один выход которого соединен с первым входом регистра матрицы, другой выход через последовательно соединенные регистр маски опроса и дешифратор адреса подключен к первому входу матрицы ассоциативны признаков, один выход которой через регистр ма рицы соединен с вторым входом матрицы ассоци тивных признаков, другой выход которой через последовательно соединенные индикатор и узел адресации подключен к первому входу накопиае ля основной информации. Выход накопителя через регистр накопителя соединен с вторым входом накопителя основной информации,Выходы блока соединены соответственно с выходами регистра матрицы, регистра накопителя и индикатора, а входы блока соединены соответственно с входами регистра опроса, узла управления, регистра маски опроса и регистра накопителя, На фиг. 1 показана блок-схема устройства для сбора и анализа данных о работе ЭВМ; на фиг, 2 - схема блока отбора данных ; на фиг. 3 - схема ассоциативного запоминающего блока. Входы коммутатора 1 подключены к кон трольным точкам исследуемой ЭВМ, а выходы через блок 2 согласования и блок 3 усилителя-к входам блока и отбора данных, который позволяет из множества входных сигналов выделить некоторое подмножество, требуемого для конкретного эксперимента, а также выполняет функции обработки собираемых статистических данных. Блок 4 отбора данных связан с блоком 5 управления устройством, содержащим память команд, схему исполнения команд, схему поиска свободной ячейки и генератор тактовых импульсов jH блоком 6 коммутации, ко торый содержит набор логических схем И, ИЛИ и под воздействием блока 5 управления устройством осуществляет передачу информации либо в ассоциативный запоминающий блок 7, либо в блок 8, Оба ассоциативных запоминающих блока 7 и 8 индентичны и предназначены для хранения данных, поступающих из блока 4 отбора данных, а также статистической информации об этих данных. Блоки 7 и 8 соединены с блоком 9 сопряжения, который связан с блоком 5 управления устройством и процессором 10, Блок 9 сопряжения реализует стандартный интерфейс ввода - вывода для связи с процессором 10 и обеспечивает вывод собранных статистических данных с любого ассоциативного запоминающего блока 7 или 8, Через блок 9 сопряжения производится также перезагрузка памяти команд блока 5 управления устройством новыми ал1оритмами измерения Процессор 10 соединен с блоком 11 пе чати, используемым для связи пользователя с операционной системой мини-ЭВМ, а также - с блокам 12 визуального вывода и через блок 13 управления накопителем на магнитной ленте с накопителем 14 на маг. нитной ленте. Процессор 10 предназначен для хранения алгоритмов измерений, аккумулирования очередных порций статистических данных блока 7 (8), обработки этих данных, представ ления их на экране блока 12 и записи на магнитную ленту. Сигналы, поступающие с выхода блока 3 усиления, можно разделить на две группы. Первая группа - это адреса команд., адреса данных, коды операций, состояния продессо ра, каналов и периферийных устройств исследуемой ЭВМ; вторая группа - это идентификаторы перечисленных выше сигнапов., (индентификатор - сигнал, показывающий, что в момент его появления возникает новое состояние). Например,идентификаторюм команды является строб команды, генерируемый в процессоре исслещемой ЭВМ после дешифраций нового кода операции. Первая группа сигналов по линии 15 (см фиг, 2) поступает в селектор 16, а втора по линии 17 в анализатор 18, который свазан с регистром 19 маски анализатора. Совместное применение анализатора 18 и программируемого регистра 19 маски по зволяет выделять только те идентификаторы которые необходимы для проведения конкретного эксперимента. Селектор 16 содержит программируемы входной регистр и матрицу переключающих вентилей. Путем изменения содержимого Bx ного регистра производится отбор сигналов необходимых для данного эксперимента. Блок 4 содержит сумматор 20 накаплкн ваюшего типа, связанный со счетчиком 21, имеющим вход 22 для добавления единиц. Регистр 23 опроса, выполненный в виде счетчика (см, фиг, 3) и входящий в состав блока 7 (3), связан с регистром 24 матрицы и через регистр 25 маски опроса и дешифратор 26 адреса - с входами матрицы 27 ассоциативных признаков, кроме того, регистр 23 опроса по входу 28 доба ления единиц связан с узлом 29 управлени Матрица 27 ассоциативных признаков используется для хранения признаков, поступающих из регистра 23 опроса. Регистр 24 матрицы используется при выполнении операций запись/чтение и своими входами и выходами связан с матрицей ассоциативных признаков, которая также подключена через индикатор ЗО и узел 31 адресации к накопителю 32 основной информации. Индикатор 30 содержит набор детекторов и шифратор адреса и используется для установления равенства/неравенства содержимого регистра 23 опроса и содержимого одной из ячеек матрицы 27 ассоциативных признаков. Накопитель 32 основной информации используется для запоминания числа появлений признаков, их длительностей, комбинаций и т, п, Каждой ячейке накопителя 32 основной информации соответствует единственная ячейка матрицы 27 ассоциативных признаков и первая выбирается всякий раз, когда установлен индикатор соответствующей матрицы ассоциативных признаков. Накопитель 32 основной информации связан с регистром накопителя, который используется для выполнения операций запись/чтение. Устройство работает с использованием программируемых алгоритмов измерений, Которые реализуются следующим набором основных операций; Запись по ад рее у (ЗП,АДР) - в регистр 23 опроса помещается адрес по которому записывается содержимое регис тра 24 матрицы и регистра 33 накопителя, Чтение по адресу (ЧТ,АДР) -в регистр 23 опроса помещается адрес, по которому считывается информация в регистр 24 матрицы и регистр 33 накопителя. Опрос (ОПРС) -содержимое регистра 23 опроса через регистр 25 маски опроса сравнивается со всеми словами, зфанящимися в матрице 27 ассоциативных признаков по критерию РАВНО, в результате чего для ячейки с равным содержимым в индикаторе 30 устанавливается индикатор и в блок 5 управления устройством через блок 6 коммутации поступает сигнал РАВНО} в противном случае - сигнал НЕ РАВНО, Запись нового (ЗП,НВ) -содержимое регистра 24 матрицы и регистра 33 накопителя запоминается в первой свободной ячейке. Запись по признаку (ЗП,ПР) - содержимое регистра 33 накопителя запоминается в ячейке, для которой в индикаторе 30 установлен индикатор РАВНО, Чтение по признаку {ЧТ,ПР) -содержимое ячейки, для которой установлен индикатор РАВНО, считывается в регистр 33 накопителя. Маскирование (MACK) -производится подавление части признака, хранящегося в регистре 23 признака. Перед началом измерений пользователь сообщает операционной системе мини- ЭВМ следующую информацию: тип алгоритма иэмерени1 какая информация и в какой форме должна выводиться на блок 12j время, через которое необходимо изменять информацию на экране блока 12 (время индикации), необходимость записи данных на архивную ле№ту накопителя 14. Получив указанную информацию, процессор 10 сбрасывает блок 4 отбора данных, блок 5 управления устройством, ассоциативные запоминающие блоки 7,8 и загружает память команд блока 5 управления устройством выбранным алгоритмом измерений. По окончании загрузки блок 5 управления устройством устанавлибает направление передачи информ ции с выхода блока 6 коммутации в блок 7 и состояния, требуемые заданным алгоритмом измерений, для следующих регистров; регистра 19, регистра 25 маски опроса и входного регистра селектора 16, а также выдает сигнал в анализатор 18, разрешающий его работу. При возникновении любого немаскируемого идентификатора анализатор 18 выдает сигнал в блок 5 управления устройством, по которому информация, присутствующая на линии 15. через селектор 16 и блок 6 коммутации псх тупает в регистр 23 опроса блока 7. Информация, поступившая в регистр 23 опроса , используется в качестве ассоциагтивного признака, над которым выполняется последовательность действий, предписан ных алгоритмом измерений, Р ассм отрим работу устройс тва при вьш олнении некоторых алгоритмов измерений. Измерение длительностей, В этом режиме совместно с сигналом, разрешающим работу анализатора 18, блок 5 управления устройством разрешает поступление импульсов от генератора тактовых импульсов (ГТИ в счетчик 21 по входу 22, тем самым измеряется длительность сигнала на основе счетно-импульсного метода, Для обеспечения различной разрешающей способности при измерении длительностей ГТИ может быть также программируемым При появлении идентификатора блок 5 управления устройством наря.ду с загру; кой регистра 23 опроса производит следуюшие операции; прекращает добавление импульсов в счетчик 21, передает содержимое счетчика 21 в сумматор 2О, сбрасывает счетчик 21, разрешает добавление импульсов в счетчик 21 и выполняет команду ОПРС. Если из индикатора ЗО через блок 6 коммутации в блок 5 управления устройством поступает сигнал РАВНО, то блок5 выполняет ЧТ.ПР, передачу содержимого регистра 33 накопителя через блок 6 коммутации в сумматор 20, сложение, передачу результата через блок 6 коммутации в регистр 33 накопителя, ЗП.ПР и сброс регистра 33 накопителя и сумматора 20. Устройство ожидает появления нового иден тификатора. Если же поступает сигнал НЕ РАВНО то содержимое сумматора 20 через блок6 коммутации передается в регистр 33 накопителя, а содержимое регистра 23 опросав регистр 24 матрицы и выполняется ЗП, ИВ, после которой производится сброс сумматора 20, регистра накопителя и регистра матрицы. Устройство ожидает возникновения нового идентификатра. Данный алгоритм может использоваться для измерения длительностей нахождения про цессора, каналов, периферийных устройств Е возможных для них состояниях. Применяя операцию маскирования можно измерять длИ тельности состояний отдельных компонент и их логических комбинаций, В результате про работки алгоритма в матрице 27 ассоциативных признаков хранятся типы возникших состояний, а в соответствующих ячейках накопителя 32 основной информации-cy марные длительности этих состояний за время индикации. Измерение числа повторений, В этом режиме одновременно с загрузкой регистра 23 опроса производится добавление единицы в счетчик 21, далее передача содержимого счетчика 21 в сумматор 2О, сброс счетчика 21, выполнение ОПРС, При получении из индикатора 30 сигн&ла РАВНО блок 5 управления устройством выполняет ЧТ.ПР, передачу содержимого регистра накопителя в сумматор 20, сложение, передачу результата сложения в регистр накопителя, ЗП, ПР, сброс сумматора 20 и регистра накопители, переход в состояние ожидания нового идентификатора. При поступлении сигнала НЕ РАВНО выполняется следующая последовательность операций: содержимое сумматора 20 передается в регистр 33 накопителя, а содержимое регистра 23 опроса - в регистр матрицы, ЗП. НВ, сброс регистра накопителя, регистра матрицы, сумматора, ожидание нового идентификатора. Алгоритм может использоваться для измерения числа появления таких событий, как адреса команд, адреса данных, коды операций. За время индикации в блоке 7 (8) накапливается гистограмма по измеряемому событию. Измерение длин линейксых участков программ, В этом режиме процессор 10 загружает память команд блока 5 управления устройством не только алгоритмом измерений, но и командами перехода, существующими в системе команд данной ЭВМ. Используя команду ЗП,АДР, блок 3 управения устройством пересылает команды пеехода в матркиу 27 ассоциативных признаов и настраивает селектор 16 и анализатор 18 а выделение соответственно кодов опеаций и строба команды. После появления идентификатора и загрузи регистра 23 опроса, блок управления усройством выполняет команду ОПРС, При получении сигнала НЕ РАВНО из ндикатора 30, в счетчик 21 добавляется диница и устройство переходит в состояние жидания нового идентификатора. Если пришел сигнал РАВНО, то блок правления устройством передает содеримое счетчика 21 через блок 6 коммуации в регистр 23 опроса, сбрасывает счетик 21, выполняет ОПРС. В случае получения сигнала НЕ РАВНО блок управления устройством передает содержимое регистра опроса в регистр 24 ма трицы, выполняет ЗП. НВ, после чего сбрасывает регистр накопителя, регистр матрицы и сумматор. Устройство ожидает возник новения нового идентификатора. При получении сигнала РАВНО блок 5 управления устройством выполняет ЧТ.ПР, передачу содержимого регистра 33 накопителя в сумматор 20, добавление единицы в счетчик 21, передачу содержимого счетчика 2 в сумматор 20, сложение, передачу результата в регистр накопителя, ЗГ1.ПР, сброс счетчика 21, регистра накопителя, сумматора и переходит в состояние ожидания ново го идентификатора. За время индикации для каждой команды перехода накапливается гистрограмма линей ных участков. Поскольку алгоритмы программируемы, то пользователь может легко модифицироват конкретный алгоритм измерений. Например,алгоритм измерения длительностей легко модифицировать так, чтобы получать не только суммарное время по определенному состоянию, но и гистограмму длительностей, По истечении времени индикации, процес сор 10 через блок 9 сопряжения передает в блок 5 управления устройством управляющий сигнал, по которому блок 5, завершив очередной цикл отработки; меняет направление передачи информации с выхода блока 6 коммутации в блок 8 и посылает управляющий сигнал в узел 29 управления блока 7 Узел 29 управления начинает выполнять в цикле команду ЧТ.АДР, модифицируя по входу 28 содержимое регистра 23 опроса. После полной перекачки содержимого блока 7 в память процессора 1О, последний, используя программы визуального вывода, осуществляет индикацию собранной информации на экране блока 12 и при необходимости записывает ее на архивную ленту 14. Описанный цикл работы повторяется до подачи пользователем команды прекращения измерений или до замены старого алгорит ма измерений новым. Для реально существующих ЭВМ устройство позволяет, решать задачу адаптации конфигурации ЭВМ и ее операционной системы к реальной входной нагрузке с целью оптимизации производительности ЭВМ, Формула изобретения 1, Устройство для сбора и анализа дан ных о работе электронной вычислительной машины, содержащее блок управления устройством, блок управления накопителем на магнитной ленте, блок визуального вывода, блок усиления, вход которого через последовательно соединенные коммутатор и блок согласования соединен с входом устройства, отличающееся тем, что, с целью повышения эффективности работы устройства, в него введены блоки коммутации, сопряжения, отбора данных, два ассоциативных запоминающих блока, процессор и блок печати, причем блок отбора данных соединен с блоком управления устройством, выходом блока усиления и через блок коммутации, подключенный к блоку управления устройством, с ассоциативными запоминающими блоками, выходы которых через блок сопряжения, соединенный с блоком управления устройством, подключены к процессору, выходы которого подключены соответственно к блокам визуального вывода и печати, а через блок управления накопителем на магнитной ленте - к накопителю на магнитной ленте, 2.Устройство поп. 1, отличающее с я тем, что в нем блок отбора данных содержит анализатор, регистр маски анализатора, селектор, счетчик и сумматор, первый вход которого соединен с первым выходом счетчика, вход анализатора соединен с выходом регистра маски анализатора, управляющие входы блока подключены соответственно к управляющим входам анализатора,селектора, счетчика, регистра маски анализатора и второму входу сумматора, выходы блока соединены соответственно с выходами селектора, сумма.- тора, анализатора и вторым выходом счетчика, информационные входы анализатора и селектора подключены к входу приема усиленных сигналов, 3.Устройство по пп. 1и 2, отличающееся тем, что в нем ассоциативный запоминающий блок содержит регистр опроса, регистр маски опроса дешифратор адреса, матрицу ассоциативных признаков, регистр матрицы, индикатор, узел адресации, накопитель основной информации, регистр накопителя и узел управления, выход которого подключен к управляющему входу регист ра опроса, один выход которого соединен с первым входом регистра матрицы, другой выход через последовательно соединенные регистр маски опроса и дешифратор адреса подключен к первому входу матрицы ассоциативных признаков, один выход которой через регистр матрицы соединен с вторым входом матрицы ассоциативных признаков.

другой выход которой через последовательно соединенные индикатор и узел адресации иод1шючен к первому входу накопителя остювной информации, выход которого через oeritcrp накопителя соединен со вторым вхс- s дом иакоггктеля основной информации, выходы блока соединены соответственно с выходами регистра матрицы, регистра накопителя и индикатора, входы блока соединены соответственно со входами регистра опроса, управления, регистра маски опроса и регистра накопителя.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для фиксации трассы выполнения программы | 1983 |

|

SU1136170A1 |

| Устройство для отладки программ | 1983 |

|

SU1290334A1 |

| Устройство для отладки программ | 1983 |

|

SU1322290A2 |

| Устройство для сбора информации | 1979 |

|

SU798783A1 |

| Устройство для синтаксического анализа программ | 1980 |

|

SU918950A1 |

| Устройство для сопряжения двух магистралей | 1988 |

|

SU1509915A2 |

| АССОЦИАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1991 |

|

RU2045787C1 |

| Ассоциативное оперативное запоминающее устройство | 1987 |

|

SU1462420A1 |

| Устройство для синтаксически-управляемого перевода | 1982 |

|

SU1062721A1 |

| Устройство для взаимного установления подлинности абонентов | 1986 |

|

SU1442993A1 |

Фиг.1

Фиг:, г

Фиг.З

Авторы

Даты

1976-07-25—Публикация

1974-12-26—Подача