Изобретение относится к, вычислительной технике, в частности к организации отладки программ и контроля функционирования ЭВМ, включенных в состав систем управления, и является усовершенствованием изобретения по аЬт.св. № 1290334,

Целью изобретения является расширение функциональных возможностей уст ройства за счет обеспечения фиксации характеристик вычислительного процесса в системе путем анализа внешних для ЭВМ сигналов.

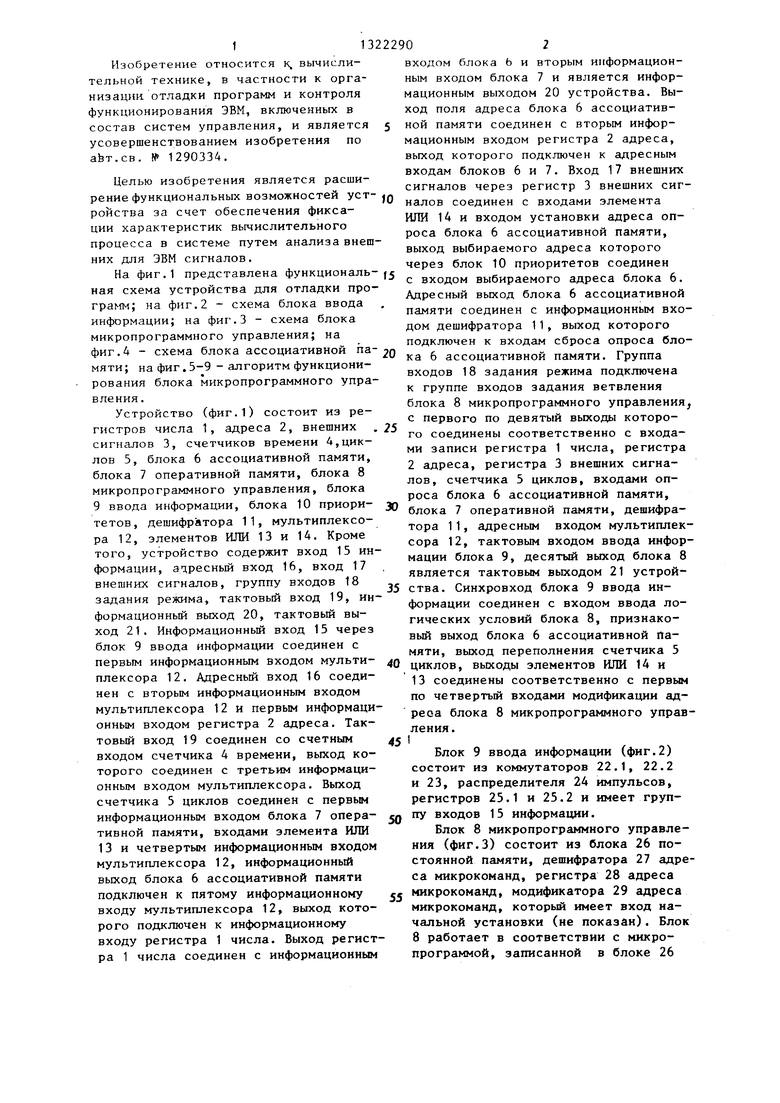

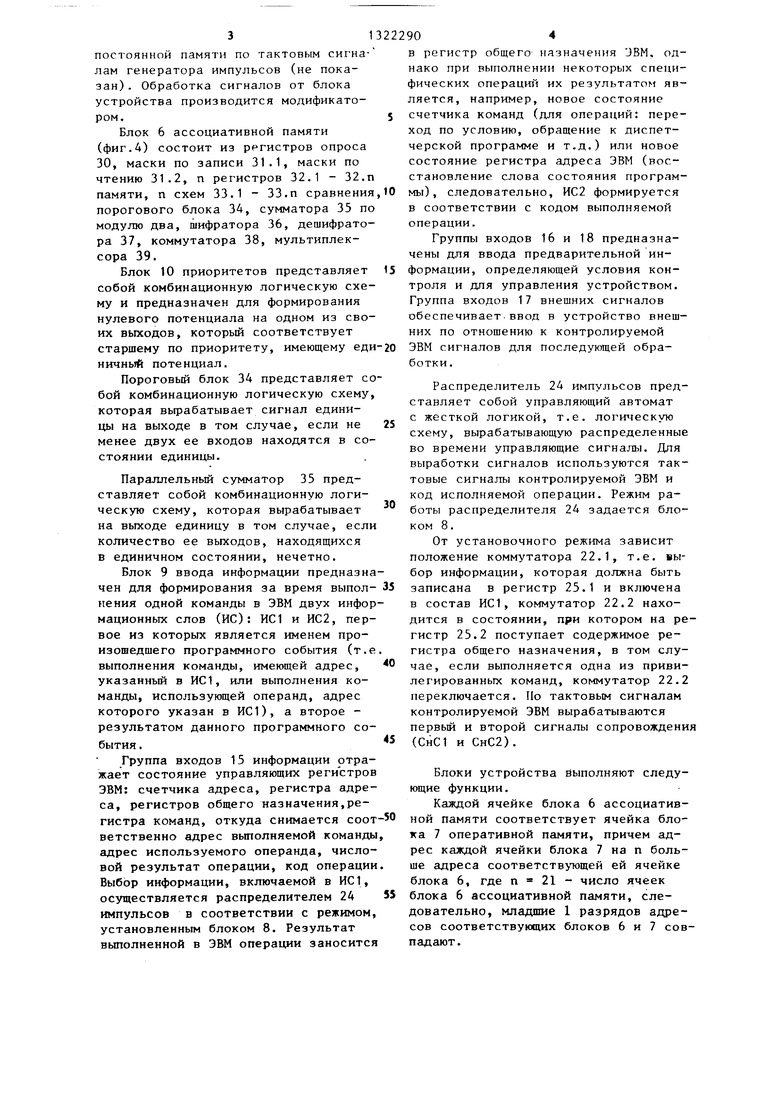

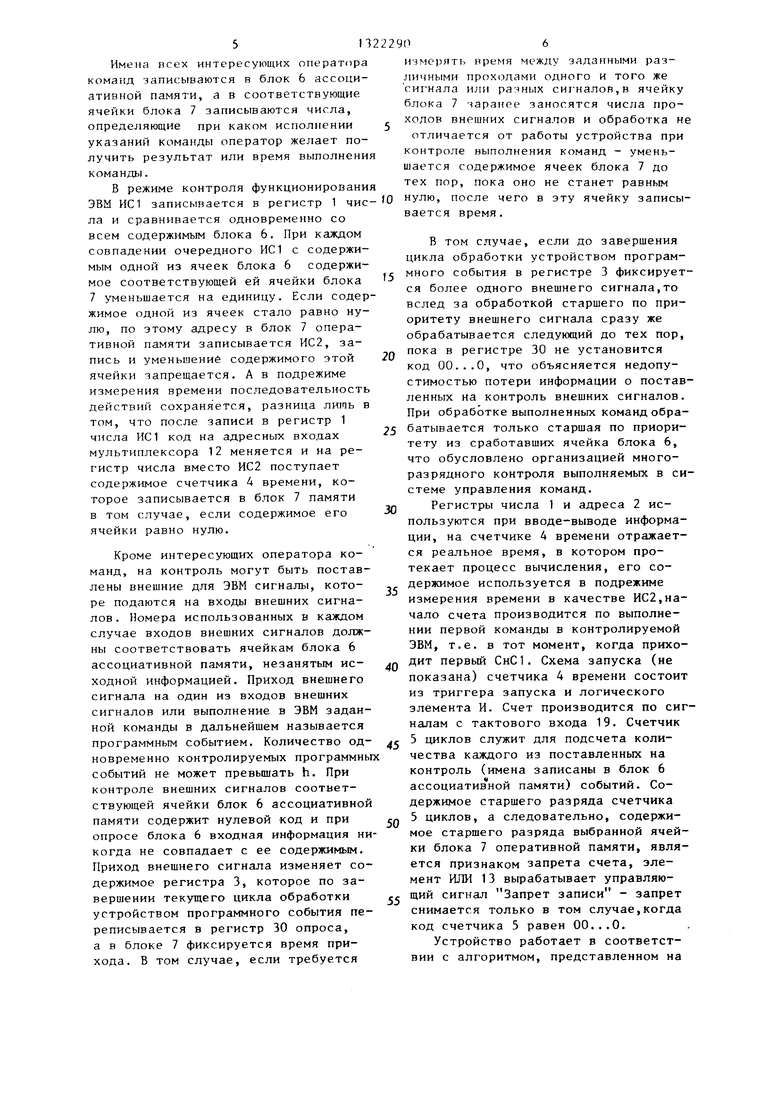

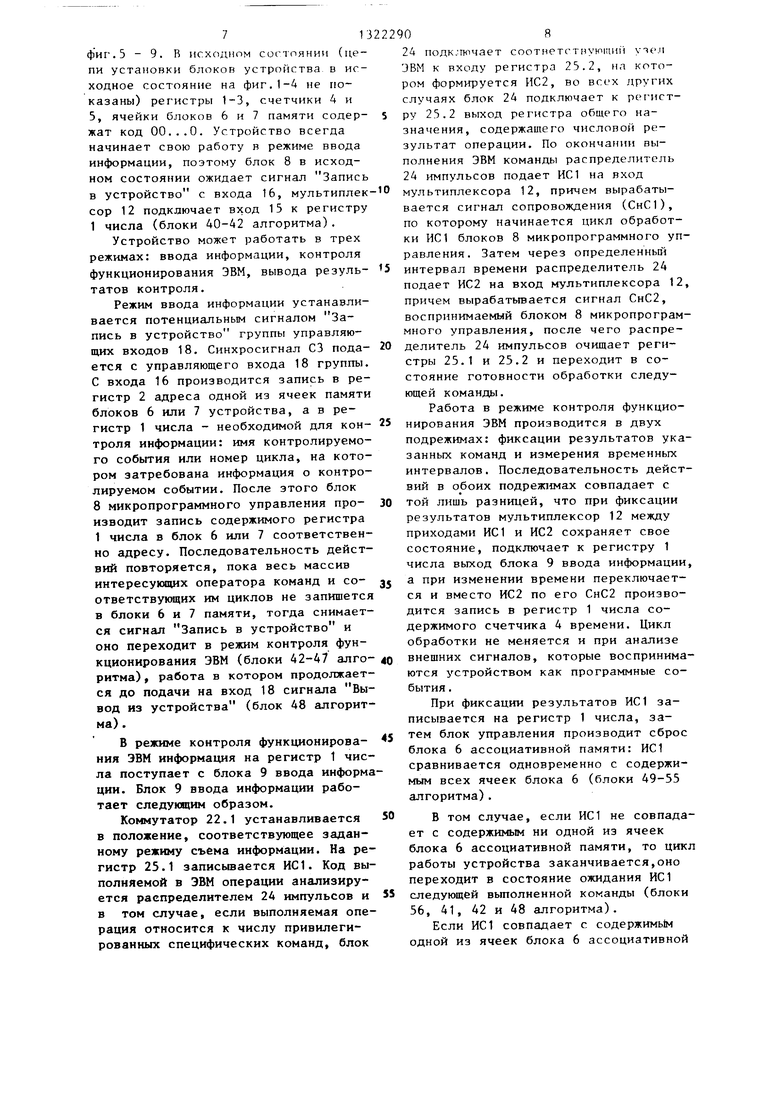

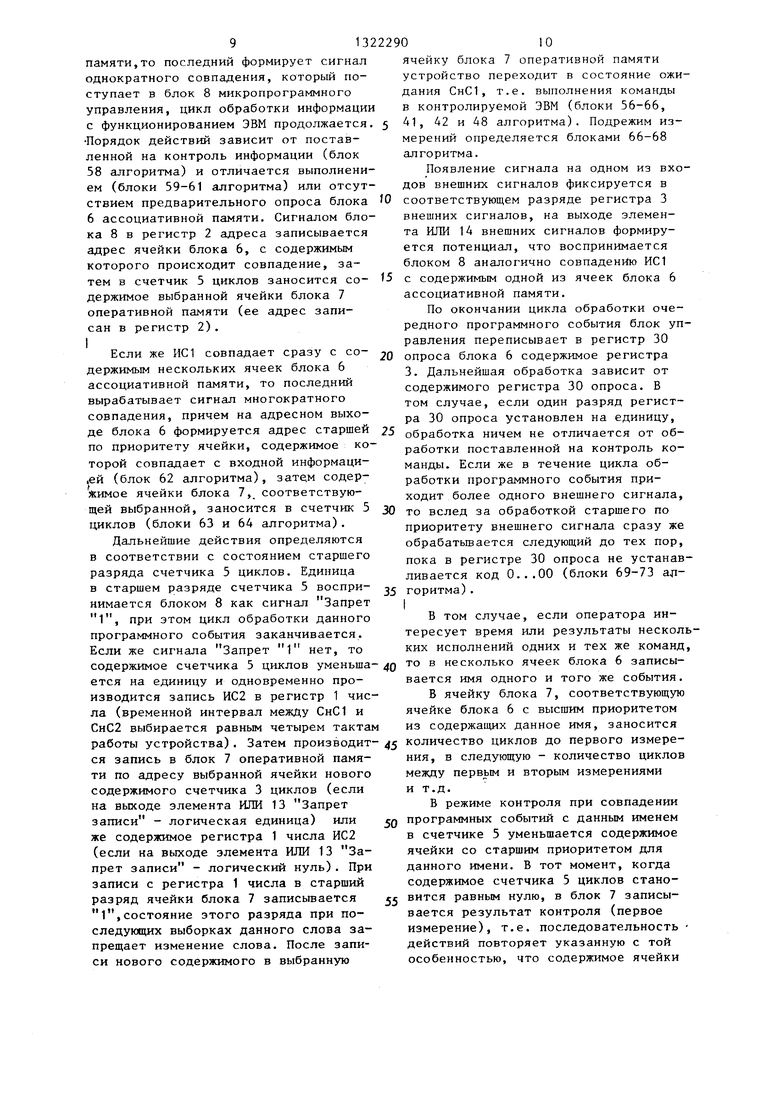

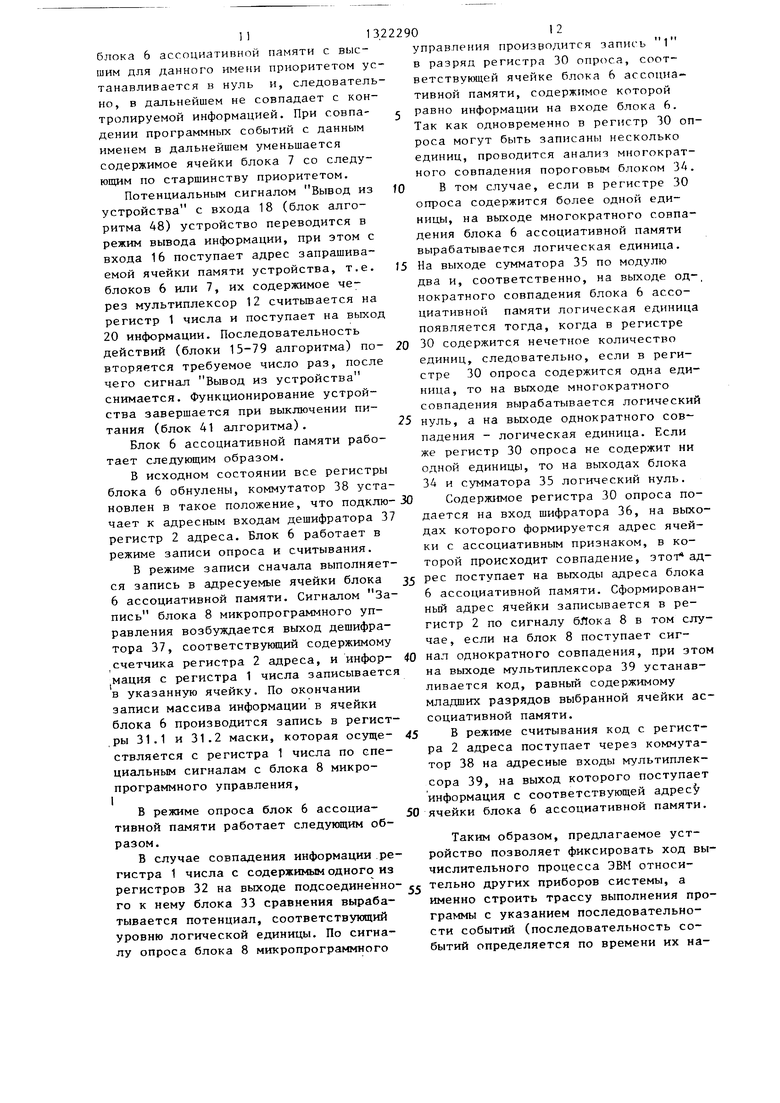

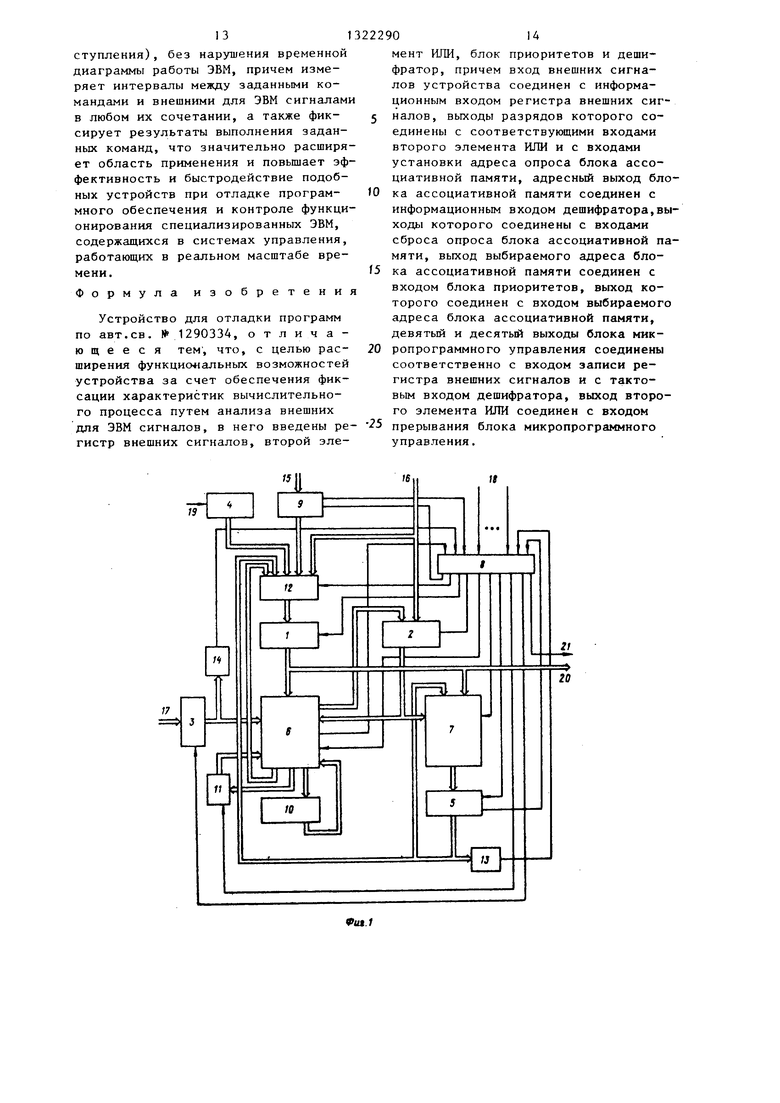

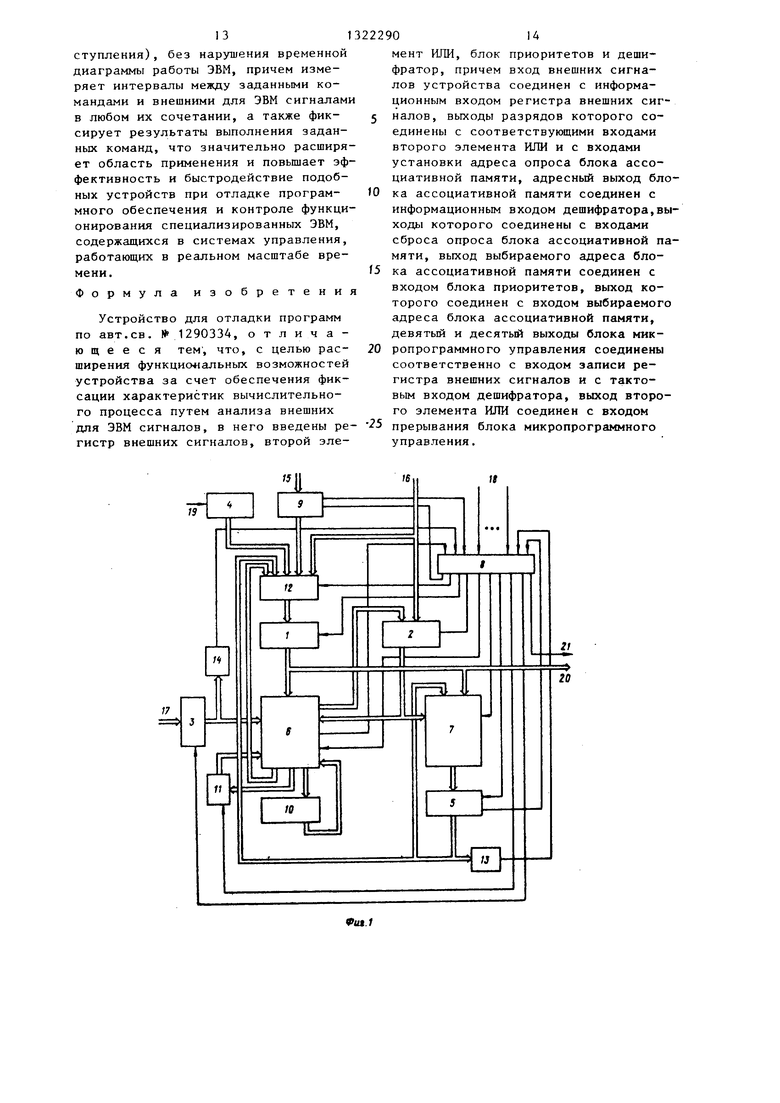

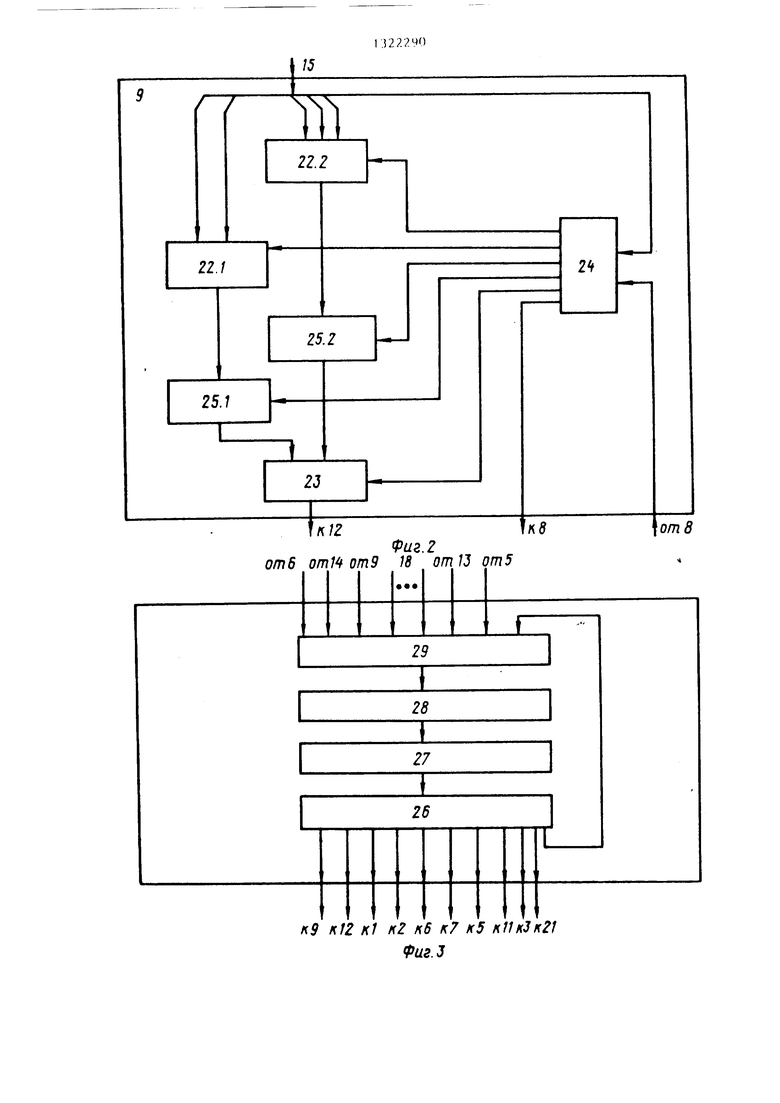

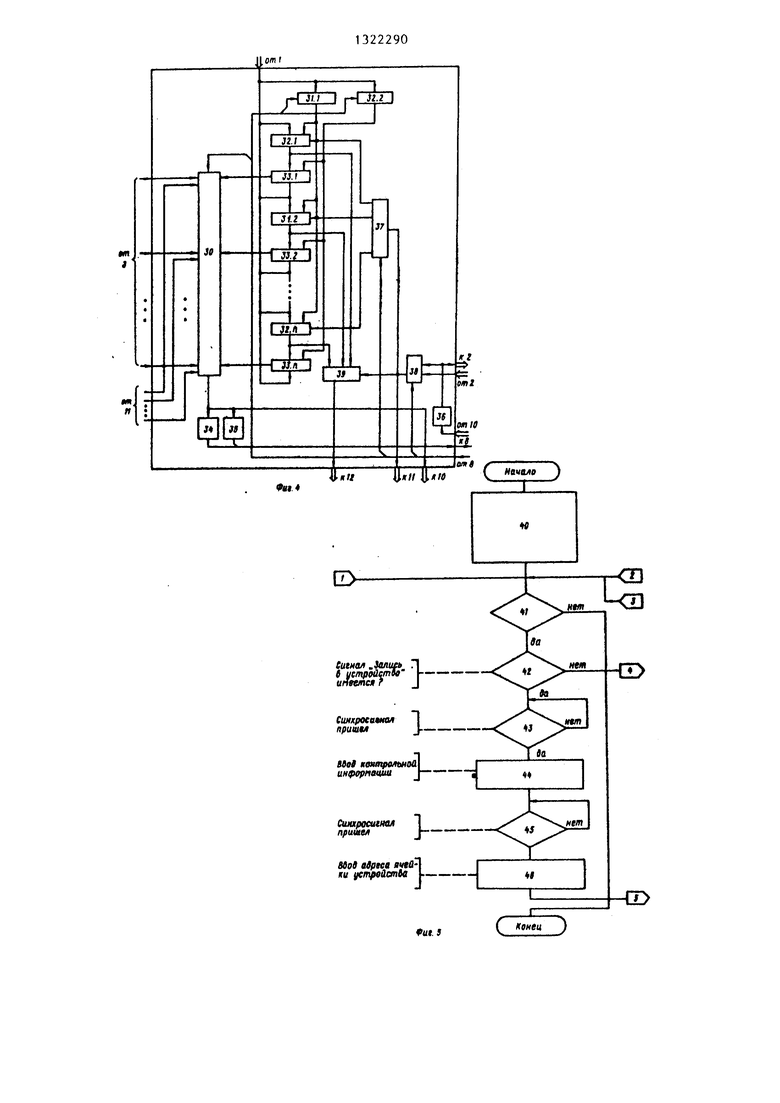

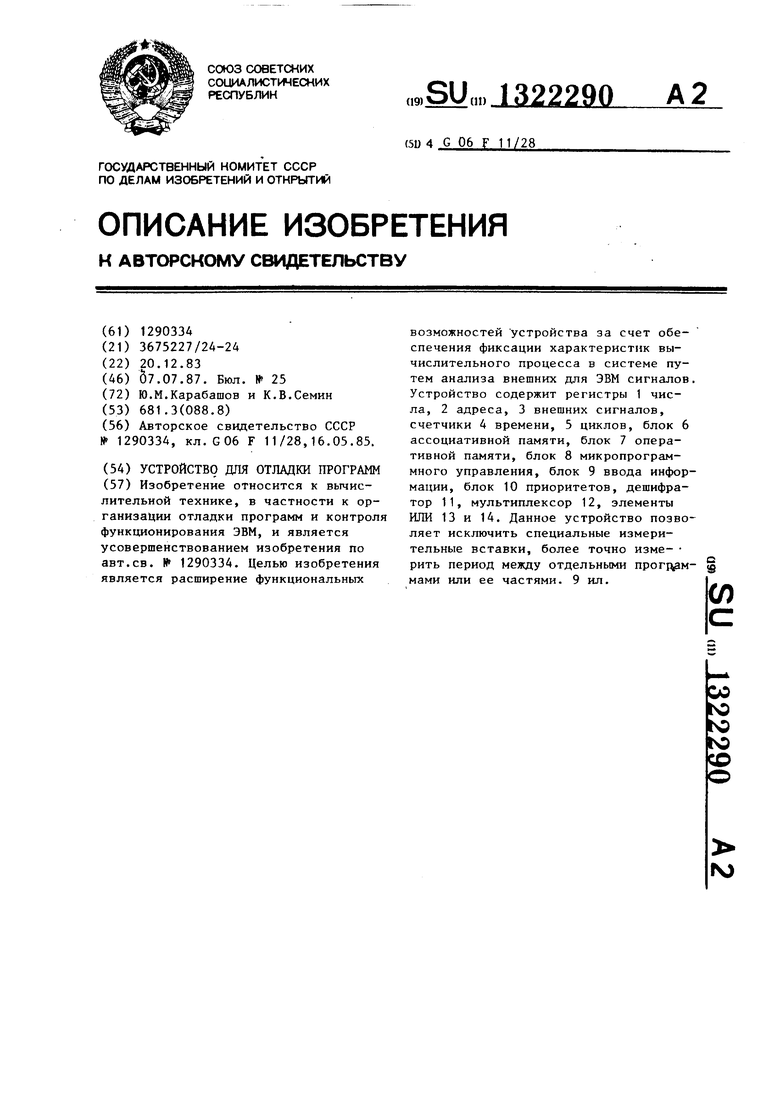

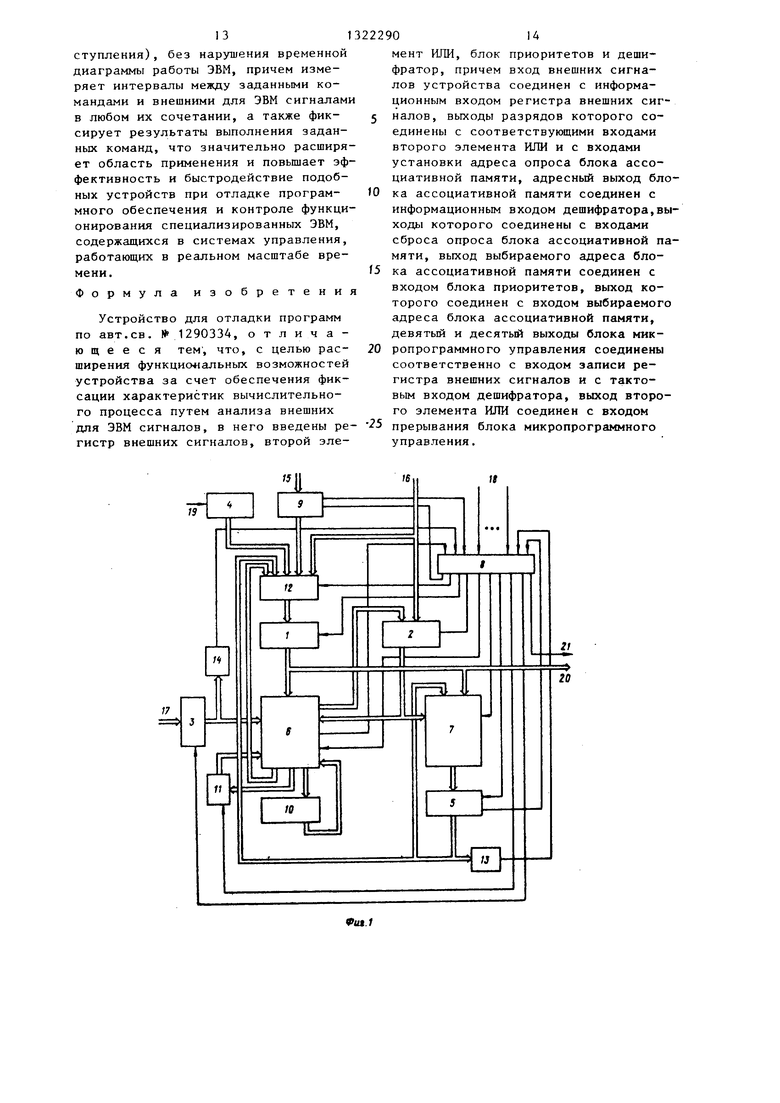

На фиг.1 представлена функциональ мая схема устройства для отладки программ; на фиг.2 - схема блока ввода информации; на фиг.З - схема блока микропрограммного управления; на фиг.4 - схема блока ассоциативной па мяти; на фиг. 5-9 - алгоритм функционирования блока микропрограммного управления.

Устройство (фиг.1) состоит из регистров числа 1, адреса 2, внешних сигналов 3, счетчиков времени 4,циклов 5, блока 6 ассоциативной памяти, блока 7 оперативной памяти, блока 8 микропрограммного управления, блока 9 ввода информации, блока 10 приоритетов, дешифратора 11, мультиплексора 12, элементов ИЛИ 13 и 14. Кроме того, устройство содержит вход 15 информации, адресный вход 16, вход 17 внешних сигналов, группу входов 18 задания режима, тактовый вход 19, информационный выход 20, тактовый выход 21. Информационный вход 15 через блок 9 ввода информации соединен с первым информационным входом мультиплексора 12. Адресный вход 16 соединен с вторым информационным входом мультиплексора 12 и первым информационным входом регистра 2 адреса. Тактовый вход 19 соединен со счетным входом счетчика 4 времени, выход которого соединен с третьим информационным входом мультиплексора. Выход счетчика 5 циклов соединен с первым информационным входом блока 7 оперативной памяти, входами элемента ИЛИ 13 и четвертым информационным входом мультиплексора 12, информационный выход блока 6 ассоциативной памяти подключен к пятому информационному входу мультиплексора 12, выход которого подключен к информационному входу регистра 1 числа. Выход регистра 1 числа соединен с информационным

5

0

5 о

входом блока b и вторым информационным входом блока 7 и является информационным выходом 20 устройства. Выход поля адреса блока 6 ассоциативной памяти соединен с вторым информационным входом регистра 2 адреса, выход которого подключен к адресным входам блоков 6 и 7. Вход 17 внешних сигналов через регистр 3 внешних сигналов соединен с входами элемента ИЛИ 14 и входом установки адреса опроса блока 6 ассоциативной памяти, выход выбираемого адреса которого через блок 10 приоритетов соединен с входом выбираемого адреса блока 6. Адресный выход блока 6 ассоциативной памяти соединен с информационным входом дешифратора 11, выход которого подключен к входам сброса опроса блока 6 ассоциативной памяти. Группа входов 18 задания режима подключена к группе входов задания ветвления блока 8 микропрограммного управления, с первого по девятый выходы которого соединены соответственно с входами записи регистра 1 числа, регистра 2 адреса, регистра 3 внешних сигналов, счетчика 5 циклов, входами опроса блока 6 ассоциативной памяти, блока 7 оперативной памяти, дешифратора 11, адресным входом мультиплексора 12, тактовым входом ввода информации блока 9, десятый выход блока 8 является тактовым выходом 21 устрой- 5 ства. Синхровход блока 9 ввода информации соединен с входом ввода логических условий блока 8, признаковый выход блока 6 ассоциативной Памяти, выход переполнения счетчика 5 циклов, выходы элементов ИЛИ 14 и 13 соединены соответственно с первым по четвертый входами модификации адреса блока В микропрограммного управления.

Q

I

Блок 9 ввода информации (фиг.2)

состоит из коммутаторов 22.1, 22.2 и 23, распределителя 24 импульсов, регистров 25.1 и 25.2 и имеет групну ВХОДОВ 15 информации.

Блок 8 микропрограммного управления (фиг.З) состоит из блока 26 постоянной памяти, дешифратора 27 адреса микрокоманд, регистра 28 адреса

микрокоманд, модификатора 29 адреса микрокоманд, который имеет вход начальной установки (не показан). Блок 8 работает в соответствии с микропрограммой, записанной в блоке 26

постоянной памяти по тактовым сигналам генератора импульсов (не показан) . Обработка сигналов от блока устройства производится модификатором.

Блок 6 ассоциативной памяти (фиг.4) состоит из регистров опроса 30, маски по записи 31.1, маски по чтению 31.2, п регистров 32.1 - 32.п памяти, п схем 33.1 - 33.п сравнения порогового блока 34, сумматора 35 по модулю два, шифратора 36, дешифратора 37, коммутатора 38, мультиплексора 39.

Блок 10 приоритетов представляет собой комбинационную логическую схему и предназначен для формирования нулевого потенциала на одном из своих выходов, который соответствует старшему по приоритету, имеющему еди ничный потенциал.

Пороговый блок 34 представляет собой комбинационную логическую схему, которая вьфабатывает сигнал единицы на выходе в том случае, если не менее двух ее входов находятся в состоянии единицы.

30

Параллельный сумматор 35 представляет собой комбинационную логическую схему, которая вырабатывает на выходе единицу в том случае, если количество ее выходов, находящихся в единичном состоянии, нечетно.

Блок 9 ввода информации предназначен для формирования за время выпол- 35 иения одной команды в ЭВМ двух информационных слов (ИС): ИС1 и ИС2, первое из которых является именем произошедшего программного события (т.е.

выполнения команды, имеющей адрес, указанный в ИС1, или выполнения команды, использующей операнд, адрес которого указан в ИС1), а второе - результатом данного программного со

бытия.

Группа входов 15 информации отражает состояние управляющих регистров ЭВМ: счетчика адреса, регистра адреса, регистров общего назначения,регистра команд, откуда снимается соот ветственно адрес вьшолняемой команды адрес используемого операнда, числовой результат операции, код операции Выбор информации, включаемой в ИС1, осуществляется распределителем 24 импульсов в соответствии с режимом, установленным блоком 8. Результат вьтолненной в ЭВМ операции заносится

5

Ю

15 20

5

0

5

0

5

О 5

в регистр общего назначения ЭВМ. однако при выполнении некоторых специфических операций их результатом является, например, новое состояние счетчика команд (для операций: переход по условию, обращение к диспетчерской программе и т.д.) или новое состояние регистра адреса ЭВМ (восстановление слова состояния программы) , следовательно, ИС2 формируется в соответствии с кодом выполняемой операции.

Группы входов 16 и 18 предназначены для ввода предварительной информации, определяющей условия контроля и для управления устройством. Группа входов 17 внешних сигналов обеспечивает ввод в устройство внешних по отношению к контролируемой ЭВМ сигналов для последующей обработки.

Распределитель 24 импульсов представляет собой управляющий автомат с жесткой логикой, т.е. логическую схему, вырабатывающую распределенные во времени управляющие сигналы. Для выработки сигналов используются тактовые сигналы контролируемой ЭВМ и код исполняемой операции. Режим работы распределителя 24 задается блоком 8.

От установочного режима зависит положение коммутатора 22.1, т.е. выбор информации, которая должна быть записана в регистр 25.1 и включена в состав ИС1, коммутатор 22.2 находится в состоянии, при котором на регистр 25.2 поступает содержимое регистра общего назначения, в том случае, если выполняется одна из привилегированных команд, коммутатор 22.2 переключается. По тактовым сигналам контролируемой ЭВМ вырабатываются первый и второй сигналы сопровождения (СнС1 и СнС2).

Блоки устройства выполняют следующие функции.

Каждой ячейке блока 6 ассоциативной памяти соответствует ячейка блока 7 оперативной памяти, причем адрес каждой ячейки блока 7 на п больше адреса соответствующей ей ячейке блока 6, где п 21 - число ячеек блока 6 ассоциативной памяти, следовательно, младшие 1 разрядов адресов соответствующих блоков 6 и 7 совпадают.

51

Имена псех интересующих оператора команд записываются в блок 6 ассоциативной памяти, а в соответствующие ячейки блока 7 записьшаются числа, определяющие при каком исполнении указаний команды оператор желает получить результат или время выполнени команды.

В режиме контроля функционировани ЭВМ ИС1 записывается в регистр 1 чис ла и сравнивается одновременно со всем содержимым блока 6. При каждом совпадении очередного ИС1 с содержимым одной из ячеек блока 6 содержимое соответствующей ей ячейки блока 7 уменьшается на единицу. Если содержимое одной из ячеек стало равно нулю, по этому адресу в блок 7 оперативной памяти записывается ИС2, запись и уменьшение содержимого этой ячейки запрещается. А в подрежиме измерения времени последовательность действий сохраняется, разница лишь в том, что после записи в регистр 1 числа ИС1 код на адресных входах мультиплексора 12 меняется и на регистр числа вместо ИС2 поступает содержимое счетчика 4 времени, которое записывается в блок 7 памяти в том случае, если содержимое его ячейки равно нулю.

Кроме интересующих оператора команд, на контроль могут быть поставлены внещние для ЭВМ сигналы, кото- ре подаются на входы внешних сигналов. Номера использованных в каждом случае входов внешних сигналов должны соответствовать ячейкам блока 6 ассоциативной памяти, незанятым исходной информацией. Приход внешнего сигнала на один из входов внешних сигналов или выполнение в ЭВМ заданной команды в дальнейшем называется программным событием. Количество одновременно контролируемых программны событий не может превьпиать h. При контроле внешних сигналов соответствующей ячейки блок 6 ассоциативной памяти содержит нулевой код и при опросе блока 6 входная информация никогда не совпадает с ее содержимым. Приход внешнего сигнала изменяет содержимое регистра 3, которое по за- верщении текущего цикла обработки устройством программного события переписывается в регистр 30 опроса, а в блоке 7 фиксируется время прихода. В том случае, если требуется

измерять время между эадаршыми различными проходами одного и того же сигнала или раяных си1 налов,в ячейку блока 7 заранее заносятся числа проходов внешних сигналов и обработка не

отличается от работы устройства при контроле выполнения команд - уменьшается содержимое ячеек блока 7 до тех пор, пока оно не станет равным нулю, после чего в эту ячейку записывается время.

В том случае, если до завершения цикла обработки устройством программного события в регистре 3 фиксируется более одного внешнего сигнала,то вслед за обработкой старшего по приоритету внешнего сигнала сразу же обрабатывается следующий до тех пор, пока в регистре 30 не установится код 00...О, что объясняется недопустимостью потери информации о поставленных на контроль внешних сигналов. При обработке выполненных команд обрабатывается только старшая по приоритету из сработавших ячейка блока 6, что обусловлено организацией многоразрядного контроля выполняемых в системе управления команд.

Регистры числа 1 и адреса 2 используются при вводе-выводе информации, на счетчике А времени отражается реальное время, в котором протекает процесс вычисления, его содержимое используется в подрежиме измерения времени в качестве ИС2,начало счета производится по выполнении первой команды в контролируемой ЭВМ, т.е. в тот момент, когда приходит первый СнС1. Схема запуска (не показана) счетчика 4 времени состоит из триггера запуска и логического элемента И. Счет производится по сигналам с тактового входа 19. Счетчик 5 циклов служит для подсчета количества каждого из поставленных на контроль (имена записаны в блок 6 ассоциативной памяти) событий. Содержимое старшего разряда счетчика 5 циклов, а следовательно, содержимое старшего разряда выбранной ячейки блока 7 оперативной памяти, является признаком запрета счета, элемент ИЛИ 13 вырабатывает управляющий сигнал Запрет записи - запрет снимается только в том случае,когда код счетчика 5 равен 00...0.

Устройство работает в соответствии с алгоритмом, представленном на

фиг.5 - 9. В исходном состоянии (цепи установки блоков устройства в исходное состояние на фиг.1-4 не показаны) регистры 1-3, счетчики 4 и 5, ячейки блоков 6 и 7 памяти содер- жат код 00...0. Устройство всегда начинает свою работу в режиме ввода информации, поэтому блок 8 в исходном состоянии ожидает сигнал Запись в устройство с входа 16, мультиплек сор 12 подключает вход 15 к регистру 1 числа (блоки 40-42 алгоритма).

Устройство может работать в трех режимах: ввода информации, контроля функционирования ЭВМ, вывода резуль- татов контроля.

Режим ввода информации устанавливается потенциальным сигналом Запись в устройство группы управляющих входов 18. Синхросигнал СЗ пода- ется с управляющего входа 18 группы. С входа 16 производится запись в регистр 2 адреса одной из ячеек памяти блоков 6 или 7 устройства, а в регистр 1 числа - необходимой для кон- троля информации: имя контролируемого события или номер цикла, на котором затребована информация о контролируемом событии. После этого блок 8 микропрограммного управления про- изводит запись содержимого регистра 1 числа в блок 6 или 7 соответственно адресу. Последовательность действий повторяется, пока весь массив интересующих оператора команд и со- ответствующих им циклов не запишется в блоки 6 и 7 памяти, тогда снимается сигнал Запись в устройство и оно переходит в режим контроля функционирования ЭВМ (блоки 42-47 алго- ритма), работа в котором продолжается до подачи на вход 18 сигнала Вывод из устройства (блок 48 алгоритма) .

В режиме контроля функционирова- ния ЭВМ информация на регистр 1 числа поступает с блока 9 ввода информации. Блок 9 ввода информации работает следующим образом.

Коммутатор 22.1 устанавливается в положение, соответствующее заданному режиму съема информации. На регистр 25.1 записывается ИС1. Код выполняемой в ЭВМ операции анализируется распределителем 24 импульсов и в том случае, если выполняемая операция относится к числу привилегированных специфических команд, блок

24 подключает соотнетстнуюший учел ЭВМ к входу регистра 25.2, ил котором формируется НС2, во всех других случаях блок 24 подключает к регистру 25.2 выход регистра общего назначения, содержащего числовой результат операции. По окончании выполнения ЭВМ команды распределитель 24 импульсов подает ИС1 на вход мультиплексора 12, причем вырабатывается сигнал сопровождения (СнС1), по которому начинается цикл обработки ИС1 блоков 8 микропрограммного управления. Затем через определенный интервал времени распределитель 24 подает ИС2 на вход мультиплексора 12 причем вырабатывается сигнал СнС2, воспринимаемый блоком 8 микропрограммного управления, после чего распределитель 24 импульсов очищает регистры 25.1 и 25.2 и переходит в состояние готовности обработки следующей команды.

Работа в режиме контроля функционирования ЭВМ производится в двух подрежимах: фиксации результатов указанных команд и измерения временных интервалов. Последовательность действий в обоих подрежимах совпадает с той лишь разницей, что при фиксации результатов мультиплексор 12 между приходами ИС1 и ИС2 сохраняет свое состояние, подключает к регистру 1 числа выход блока 9 ввода информации а при изменении времени переключается и вместо ИС2 по его СнС2 производится запись в регистр 1 числа содержимого счетчика 4 времени. Цикл обработки не меняется и при анализе внещних сигналов, которые воспринимаются устройством как программные события .

При фиксации результатов ИС1 записывается на регистр 1 числа, затем блок управления производит сброс блока 6 ассоциативной памяти: ИС1 сравнивается одновременно с содержимым всех ячеек блока 6 (блоки 49-55 алгоритма).

В том случае, если ИС1 не совпадает с содержимым ни одной из ячеек блока 6 ассоциативной памяти, то цик работы устройства заканчивается,оно переходит в состояние ожидания ИС1 следующей вьшолненной команды (блоки 56, 41, 42 и 48 алгоритма).

Если ИС1 совпадает с содержимь1м одной из ячеек блока 6 ассоциативной

памяти,то последний формирует сигнал однократного совпадения, который поступает в блок 8 микропрограммного управления, цикл обработки информации с функционированием ЭВМ продолжается Порядок действий зависит от поставленной на контроль информации (блок 58 алгоритма) и отличается выполнением (блоки 59-61 алгоритма) или отсутствием предварительного опроса блока 6 ассоциативной памяти. Сигналом блока 8 в регистр 2 адреса записывается адрес ячейки блока 6, с содержимым которого происходит совпадение, затем в счетчик 5 циклов заносится со- держимое выбранной ячейки блока 7 оперативной памяти (ее адрес записан в регистр 2).

Если же ИС1 совпадает сразу с содержимым нескольких ячеек блока 6 ассоциативной памяти, то последний вырабатывает сигнал многократного совпадения, причем на адресном выхоПо окончании цикла обработки очередного программного события блок уп равления переписывает в регистр 30 опроса блока 6 содержимое регистра 3. Дальнейшая обработка зависит от содержимого регистра 30 опроса. В том случае, если один разряд регистра 30 опроса установлен на единицу.

де блока 6 формируется адрес старшей 25 обработка ничем не отличается от об30

по приоритету ячейки, содержимое которой совпадает с входной информаци- ,ей (блок 62 алгоритма), затем содержимое ячейки блока 7, соответствующей выбранной, заносится в счетчик 5 циклов (блоки 63 и 64 алгоритма).

Дальнейшие действия определяются в Соответствии с состоянием старшего разряда счетчика 5 циклов. Единица в старшем разряде счетчика 5 воспринимается блоком 8 как сигнал Запрет 1, при этом цикл обработки данного программного события заканчивается. Если же сигнала Запрет 1 нет, то содержимое счетчика 3 циклов уменьша- о ется на единицу и одновременно производится запись ИС2 в регистр 1 числа (временной интервал между СнС1 и СнС2 выбирается равным четырем тактам

работки поставленной на контроль команды. Если же в течение цикла обработки программного события приходит более одного внешнего сигнала, то вслед за обработкой старшего по приоритету внешнего сигнала сразу же обрабатьтается следующий до тех пор, пока в регистре 30 опроса не устанавливается код 0...00 (блоки 69-73 aji- 35 горитма).

I

В том случае, если оператора интересует время или результаты несколь ких исполнений одних и тех же команд то в несколько ячеек блока 6 записывается имя одного и того же события.

Б ячейку блока 7, соответствующую ячейке блока 6 с высшим приоритетом из содержащих данное имя, заносится

работы устройства). Затем производит- 45 количество циклов до первого измереся запись в блок 7 оперативной памяти по адресу выбранной ячейки нового содержимого счетчика 3 циклов (если на выходе элемента ИЛИ 13 Запрет записи - логическая единица) или же содержимое регистра 1 числа ИС2 (если на выходе элемента ИЛИ 13 Запрет записи - логический нуль). При записи с регистра 1 числа в старший разряд ячейки блока 7 записывается 1,состояние этого разряда при последующих выборках данного слова запрещает изменение слова. После записи нового содержимого в выбранную

ния, в следующую - количество циклов между первым и вторым измерениями и т.д.

В режиме контроля при совпадении Q программных событий с данным именем в счетчике 5 уменьшается содержимое ячейки со старшим приоритетом для данного имени. В тот момент, когда содержимое счетчика 5 циклов становится равным нулю, в блок 7 записывается результат контроля (первое измерение), т.е. последовательность действий повторяет указанную с той особенностью, что содержимое ячейки

55

ячейку блока 7 оперативной памяти устройство переходит в состояние ожидания СнС1, т.е. выполнения команды в контролируемой ЭВМ (блоки 56-66, 41, 42 и 48 алгоритма). Подрежим измерений определяется блоками 66-68 алгоритма.

Появление сигнала на одном из входов внешних сигналов фиксируется в соответствующем разряде регистра 3 внешних сигналов, на выходе элемента ИЛИ 14 внешних сигналов формируется потенциал, что воспринимается блоком 8 аналогично совпадению ИС1 с содержимым одной из ячеек блока 6 ассоциативной памяти.

По окончании цикла обработки очередного программного события блок управления переписывает в регистр 30 опроса блока 6 содержимое регистра 3. Дальнейшая обработка зависит от содержимого регистра 30 опроса. В том случае, если один разряд регистра 30 опроса установлен на единицу.

обработка ничем не отличается от об

работки поставленной на контроль команды. Если же в течение цикла обработки программного события приходит более одного внешнего сигнала, то вслед за обработкой старшего по приоритету внешнего сигнала сразу же обрабатьтается следующий до тех пор, пока в регистре 30 опроса не устанавливается код 0...00 (блоки 69-73 aji- горитма).

I

В том случае, если оператора интересует время или результаты нескольких исполнений одних и тех же команд, то в несколько ячеек блока 6 записывается имя одного и того же события.

Б ячейку блока 7, соответствующую ячейке блока 6 с высшим приоритетом из содержащих данное имя, заносится

ния, в следующую - количество циклов между первым и вторым измерениями и т.д.

В режиме контроля при совпадении Q программных событий с данным именем в счетчике 5 уменьшается содержимое ячейки со старшим приоритетом для данного имени. В тот момент, когда содержимое счетчика 5 циклов становится равным нулю, в блок 7 записывается результат контроля (первое измерение), т.е. последовательность действий повторяет указанную с той особенностью, что содержимое ячейки

5

блока 6 ассоциативной памяти с высшим для данного имени приоритетом устанавливается в нуль и, следовательно, в дальнейшем не совпадает с контролируемой информацией. При совпа- дении программных событий с данным именем в дальнейшем уменьшается содержимое ячейки блока 7 со следующим по старшинству приоритетом.

Потенциальным сигналом Вывод из устройства с входа 18 (блок алгоритма 48) устройство переводится в режим вывода информации, при этом с входа 16 поступает адрес запрашиваемой ячейки памяти устройства, т.е. блоков 6 или 7, их содержимое через мультиплексор 12 считьюается на регистр 1 числа и поступает на выход 20 информации. Последовательность действий (блоки 15-79 алгоритма) по- вторяется требуемое число раз, после чего сигнал Вывод из устройства снимается. Функционирование устройства завершается при выключении питания (блок 41 алгоритма).

Блок 6 ассоциативной памяти работает следующим образом.

В исходном состоянии все регистры блока 6 обнулены, коммутатор 38 установлен в такое положение, что подключает к адресным входам дешифратора 37 регистр 2 адреса. Блок 6 работает в режиме записи опроса и считывания.

В режиме записи сначала выполняется запись в адресуемые ячейки блока 6 ассоциативной памяти. Сигналом Запись блока 8 микропрограммного управления возбуждается выход дешифратора 37, соответствующий содержимому счетчика регистра 2 адреса, и инфор- мация с регистра 1 числа записывается в указанную ячейку. По окончании записи массива информации в ячейки блока 6 производится запись в регистры 31.1 и 31.2 маски, которая осуще- ствляется с регистра 1 числа по специальным сигналам с блока 8 микропрограммного управления.

В режиме опроса блок 6 ассоциа

тивной памяти работает следующим образом.

В случае совпадения информации .регистра 1 числа с содержимым одного из регистров 32 на выходе подсоединенно- го к нему блока 33 сравнения вырабатывается потенциал, соответствующий уровню логической единицы. По сигналу опроса блока 8 микропрограммного

5 0 5

0

5 0 5

0

управления производится запись 1 в разряд регистра 30 опроса, соответствующей ячейке блока 6 ассоциативной памяти, содержимое которой равно информации на входе блока 6. Так как одновременно в регистр 30 опроса могут быть записаны несколько единиц, проводится анализ многократного совпадения пороговым блоком 34.

В том случае, если в регистре 30 опроса содержится более одной единицы, на выходе многократного совпадения блока 6 ассоциативной памяти вырабатывается логическая единица. На выходе сумматора 35 по модулю два и, соответственно, на выходе од-, нократного совпадения блока 6 ассоциативной памяти логическая единица появляется тогда, когда в регистре 30 содержится нечетное количество единиц, следовательно, если в регистре 30 опроса содержится одна единица, то на выходе многократного совпадения вырабатывается логический нуль, а на выходе однократного сов падения - логическая единица. Если же регистр 30 опроса не содержит ни одной единицы, то на выходах блока 34 и сумматора 35 логический нуль.

Содержимое регистра 30 опроса подается на вход шифратора 36, на выходах которого формируется адрес ячейки с ассоциативным признаком, в которой происходит совпадение, этот адрес поступает на выходы адреса блока 6 ассоциативной памяти. Сформированный адрес ячейки записывается в регистр 2 по сигналу бЛока 8 в том случае, если на блок 8 поступает сигнал однократного совпадения, при этом на выходе мультиплексора 39 устанавливается код, равный содержимому младших разрядов выбранной ячейки ассоциативной памяти.

В режиме считывания код с регистра 2 адреса поступает через коммутатор 38 на адресные входы мультиплексора 39, на выход которого поступает информация с соответствующей адрес ячейки блока 6 ассоциативной памяти.

Таким образом, предлагаемое устройство позволяет фиксировать ход вычислительного процесса ЭВМ относительно других приборов системы, а именно строить трассу выполнения программы с указанием последовательности событий (последовательность событий определяется по времени их наступления), без нарушения временной диаграммы работы ЭВМ, причем измеряет интервалы между заданными командами и внешними для ЭВМ сигналами в любом их сочетании, а также фиксирует результаты выполнения заданных команд, что значительно расширяет область применения и повьш1ает эффективность и быстродействие подобных устройств при отладке программного обеспечения и контроле функци- ониравания специализированньп ЭВМ, содержащихся в системах управления, работающих в реальном масштабе времени.

Формула изобретения

Устройство для отладки программ по авт.св. № 1290334, отличающееся тем; что, с целью расширения функциолальных возможностей устройства за счет обеспечения фиксации характеристик вычислительного процесса путем анализа внешних для ЭВМ сигналов, в него введены регистр внешних сигналов, второй эле0

мент ИЛИ, блок приоритетов и дешифратор, причем вход внешних сигналов устройства соединен с информационным входом регистра внешних сигналов, выходы разрядов которого соединены с соответствующими входами второго элемента ИЛИ и с входами установки адреса опроса блока ассоциативной памяти, адресный выход блока ассоциативной памяти соединен с информационным входом дешифратора,выходы которого соединены с входами сброса опроса блока ассоциативной памяти, выход выбираемого адреса блока ассоциативной памяти соединен с входом блока приоритетов, выход которого соединен с входом выбираемого адреса блока ассоциативной памяти, девятый и десятый выходы блока мик0 ропрограммного управления соединены соответственно с входом записи регистра внешних сигналов и с тактовым входом дешифратора, выход второго элемента ИЛИ соединен с входом

прерывания блока микропрограммного управления.

5

22./

л/2к8

Фиг.2 отб oml от9 18 от 13 от5

к9 KlZ к1 к2 Кб к7 к5 к11кЗк21 Фиг. У

2

от 8

от I

90(4

еимал ,3anufb Л

в иипройства

инвется f J

CuHxpocatHM I пришмJ

eeof «оим рб/гшоа UHywpnaiiuu J-

Сшаросшнал пришм

Wof ««ейП iru уепфвйстба I

( Нлулла

.Фиг 5

( Уохец J

У

Синхросигнал npiiuie/i

Запрос ин(рормаиии из устройстба, ббод адреса с. бхода 18 группы

Записи б /Рг 1) информации из бл.о или 6л.7 согласно адреса

Фиг. 9

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для отладки программ | 1983 |

|

SU1290334A1 |

| Устройство для фиксации трассы выполнения программы | 1983 |

|

SU1136170A1 |

| Селекторный канал | 1983 |

|

SU1226477A1 |

| Устройство для контроля программ | 1983 |

|

SU1136172A1 |

| Устройство для сопряжения ЭВМ с периферийной системой | 1989 |

|

SU1635188A1 |

| Микропрограммное устройство для ввода-вывода информации | 1983 |

|

SU1144099A1 |

| Устройство для сопряжения двух магистралей | 1986 |

|

SU1348874A1 |

| Устройство для сопряжения электронно-вычислительной машины с группой внешних устройств | 1989 |

|

SU1734098A1 |

| Устройство для поиска информации в памяти | 1988 |

|

SU1520547A1 |

| Устройство для сопряжения электронно-вычислительной машины с группой внешних устройств | 1985 |

|

SU1278866A1 |

Изобретение относится к вычислительной технике, в частности к организации отладки программ и контроля функционирования ЭВМ, и является усовершенствованием изобретения по авт.св. № 1290334. Целью изобретения является расширение функциональных возможностей устройства за счет обеспечения фиксации характеристик вычислительного процесса в системе путем анализа внешних для ЭВМ сигналов. Устройство содержит регистры 1 числа, 2 адреса, 3 внешних сигналов, счетчики 4 времени, 5 циклов, блок 6 ассоциативной памяти, блок 7 оперативной памяти, блок 8 микропрограммного управления, блок 9 ввода информации, блок 10 приоритетов, дешифратор 11, мультиплексор 12, элементы ИЛИ 13 и 14. Данное устройство позволяет исключить специальные измерительные вставки, более точно изме- рить период между отдельными nporj M- мами или ее частями. 9 ил. (Л N)

Редактор И.Шулла

Составитель И.Сигалов

Техред И.Попович Корректор С.Черни

Заказ 2866/46 Тираж 672Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Рдушская наб., д.4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная,4

| Устройство для отладки программ | 1983 |

|

SU1290334A1 |

Авторы

Даты

1987-07-07—Публикация

1983-12-20—Подача