соответственно с управляющими входами блока формирования команд, блока объединения списков, с вторым управляюиим входом арифметико-логического блока, с управляющими входёши четырех мультиплексоров, счетчика адреса записи и счетчика адреса списка, тринадцатый выход блока управления соединен с выходе готовности устройства..

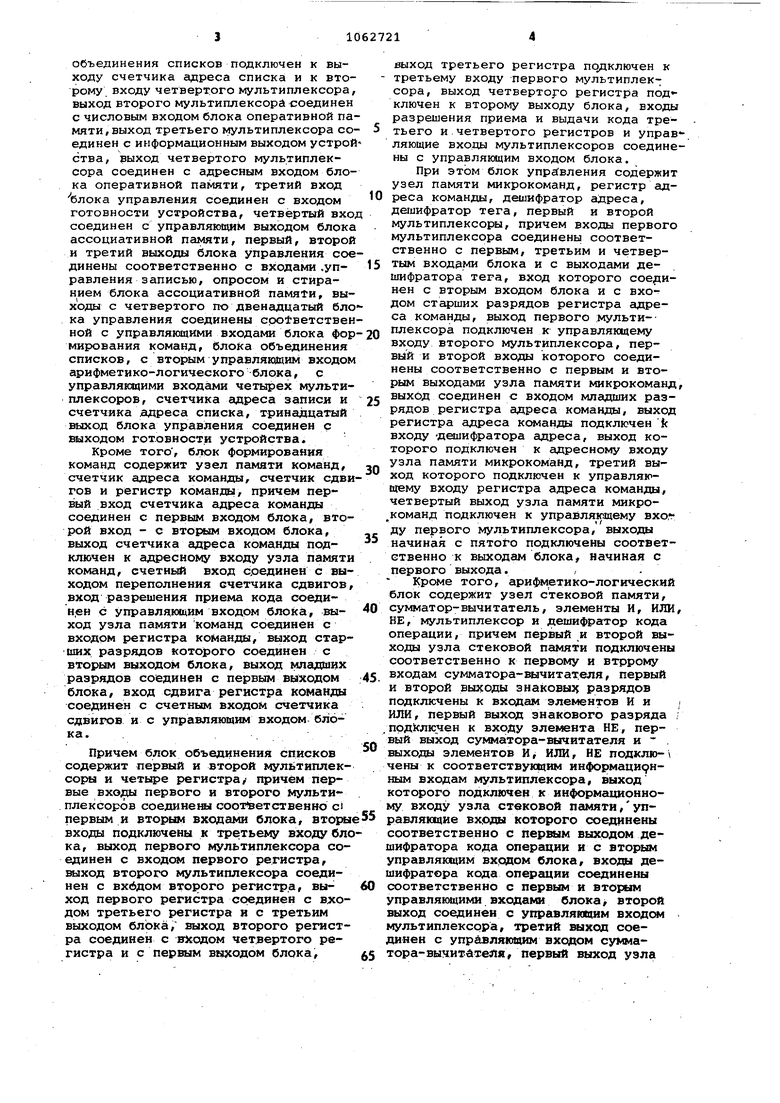

2.Устройство по п. 1, отличающееся тем, что блок форми рования команд содержит узел памятикоманд, счетчик адреса команды,счетчик сдвигов и регистр команды, причем первый вход счетчика адреса команды соединен с первым входом блока, а второй вход - с вторым входом блока, выход счетчика адреса команды подключен к адресному входу узла памяти команд, счетный вход соединен с выходом переполнения счетчика сдвигов, .вход разрешения приема кода соединен с управляющим входом блока, выход узла памяти команд.соединен с входом регистра команды, выход старших разрядов которого соеинен с вторым выходом блока, выход младших разрядов соединен с первым выходом блока, вход сдвига регистра командаа соединен с счетным входом счетчика сдвигов и с управляющим блока.

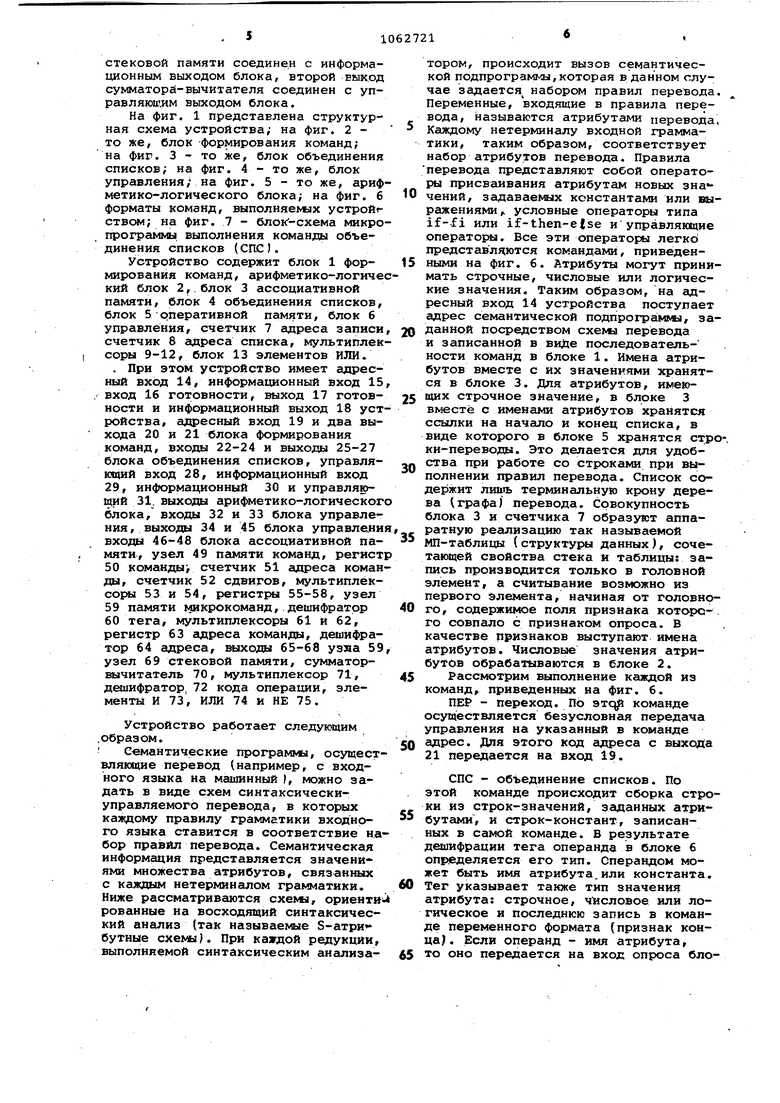

3.Устройство по п. 1, отличающееся тем, ч:то блок объеинения списков содержит первый и второй мультиплексоры и четыре стра, причем первые входы первого

и второго мультиплексоров соединены соответственно с первым и вторым вхоами .блока, вторяле входы подключены ктретьему входу блока, выход первого мультиплексора соединен с вхо ом первого регистра выход второго

мультиплексора соединен с входом второго регистра/ выход первого регистра соединен с входом третьего регистра и с третьим выходом блока, выход второго регистра соединен с

входом четвертого регистра и с перклл выходом блока, выход третьего регистра подключен к третьему входу первого мультиплексора, выход четвертого регистра подкяючеи к второму выходу блока, входы разреаеиия приема и выдачи кода третьего и четвертого регистров и управляктие входы и льтиплекссфов соединены с управляххаим . входом блока.

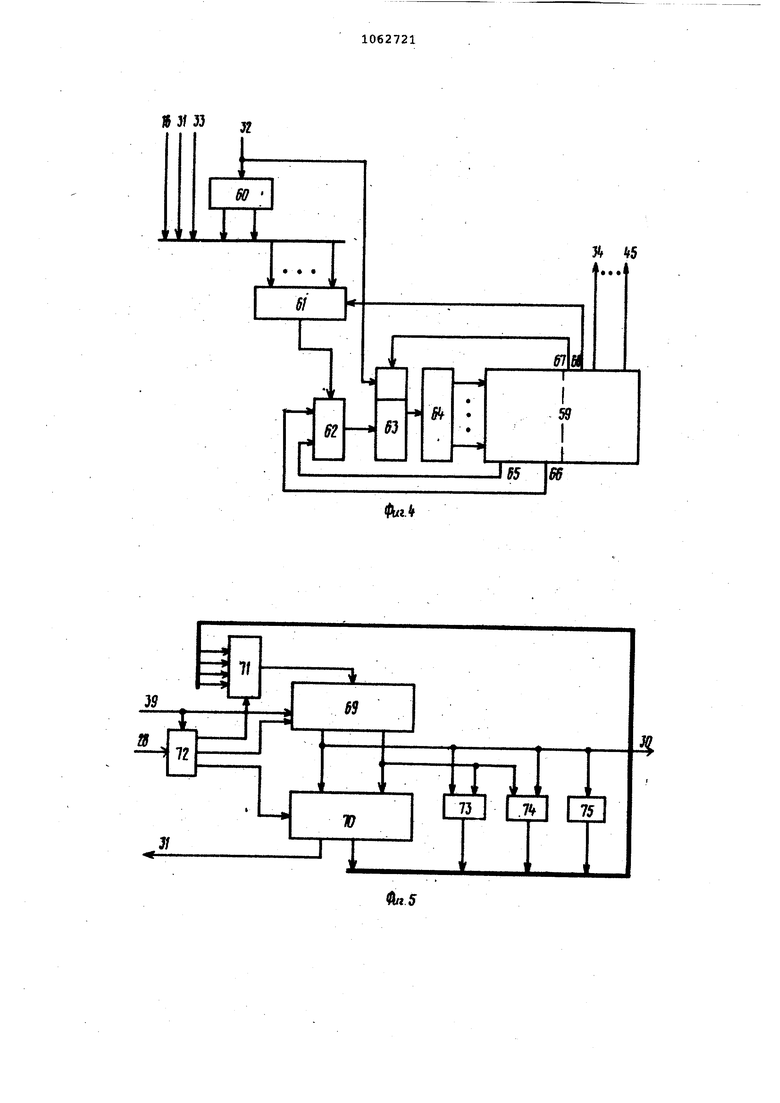

4.Устройство по п. 1, отличающееся тем, что блок управления содержит узел памяти микрокоманд, регистр адреса команды,дешифратор адреса, дешифратор тега,, первый и второй мультиплексоры, причем входы первого мультиплексора соединены соответственно с первым, третьим и четвертым входами блока и с выходами дешифратора тега, вход которого соединен с вторым входом блока и с входом ставших разрядов регистра адреса командщ, выход первого мультиплексора подключен к управлякщему входу второго мультиплексора, первый и второй входы которого соединены соответственно с первым и вторым выходами узла памяти микрокоманд, выход соединен с входсяи младших разрядов регистра адреса команды, выход регистра адреса команды подключен к входу дешифратора адреса выход которого подключен к адресному входу узла памяти микрокоманд, третий выход которого подключен к управляющему входу регистра адреса команды, четвер,тый выход узла памяти микрокоманд подключен к.управляющему входу первого мультиплексора выходы, начиная с пятого, подключены соответственно к выходам блока, начиная с первого выхода.

5. Устройство пр п. 1, отличающееся тем, что арифметикологический блок содержит узел стековой памяти, сумлатор-вычитатель, элементы И, ИЛИ, НЕ, мультиплексор и кода операции, причем первый и второй выходы узла стековой памятиподключены соответственно к первому и второму входам румматоравычитателя, первый и второй шлходы знаковых разрядов подключены к входам элементов И и ИЛИ, первый выход знакового разряда прцк;дочен к входу элемента НЕ, первый выход сумматора- вычитателя и клходы элементов И, ИЛИ, НЕ подключены к соответствующим информационным входам мультиплексора, выход которого, подключен к информационнсмду входу узла стековой Памяти, управляющие входы которого соединены соответственно с первым выходом дешифратора кода операции и с вторым управляющим входом блока, входы даиифратора кода операции соединены соответственно с п рвым и вторым управляющими входами блока, второй выход соединен с управляющим входом мультиплексора, третий выход соединен с управляющим входом сумматора-вычитателя, первый выход узла стековой памяти соединен с информационным выходом блока, второй ВЫХ.ОД сумматора-вычитателя соединен с управляющим выходом блока Изобретение относится к вычислительной технике и может быть исполь зовано в специализированных процессорах-трансляторах, осуществляющих перевод с алгоритмических языков высокого уровня на машинный язык. Известно устройство для обработки выражений языков программирования, содержащее арифметический блок блок управления, два триггера занятости, блок стековой памяти операндов, регистры операндов, блок формирования адресов и операндов, блок стековой памяти управляющих символо счетчик управляющих символов, блок анализа управляющих символов, индикаторы нуля, счетчик индексных позиций и регистр номера массива. С использованием данного., устройства может быть осуществлен синтаксический анализ выполняемой программы. В основе его работы лежит обыч ный алгоритм грак матического разбора с использованием стека операций, стека операндов и отношений пред.шествования между символами операций 13.; Однако в устройстве не предусмот рены средства перепрограммирования для выполнения различных схем перевода. Наиболее близким по технической СУ1Р.НОСТИ к изобретению является система для трансляции с проблемноориентированного языка, содержащая илчислительное устройство, оператив ное запоминаки1,ее устройство, символ ный анализатор, операторный анализа тор, модификаторы адреса: символов, макрокоманд, полуобъектных команд, объектных команд и меток, блоки nep кодировки чисел и обработки ошибок и устройство управления. Данная система предназначена для трансляции алгебраических выражений языков программирования типа АЛГОЛа и ФОРТРАНа в объектные коды электронной вычислительной машины (ЭВМ) Трансляция осуществляется с помощь двух стеков: стека уровней и стека невыполненных операций. При э.том выражение разделяется на уровни в зависимости от вложенности скобок, а уровни делятся на подуровни в зависимости от старшинства операций.. Таким образом, система выполняет лексический анализ: чтение символов выражения и распознавание лексических единиц, синтаксический анализразбор выражения с помощью стеков и генерацию кода посредством усовер шенствованного метода перевода выражений в инверсную польскую запись С23. Недостатком данной системы являю ся ее узкие функциональные возможности, ограниченные переводом тольк алгебраических выражений в машинный код, и невозможность реализации других, более сложных схем перевода на той же- аппаратуре без ее переделки, т.е. невозможность перепрограммирования системы. Целью изобретения является расширение функциональных возможностей перевода за счет увеличения класса выполняемых переводов, описываемых схемами перевода, и обеспечения перепрограммирования устройства. Поставленная цель достигается тем, что в устройство, содержащее арифметико-логический блок, блок управления и блок оперативной памяти, причем управляющий выход арифметико-логического блока соединен с первым входом блока управления, введены блок формирования команд, блок ассоциативной памяти, 6J4OK объединения списков, четыре мультиплексора, блок элементов ИЛИ, счетчик a ;peca записи и счетчик адреса списка, причем первый вход блока формирования команд соединен с адресным входом устройства, второй вход блока формирования команд соединен с первым илходом с входом опроса блока ассоциативной памяти, с первыми входами первого, второго и третьего мультиплексоров, и с первым входом блока элементов ИЛИ, второй выход блока формирования команд соединен с вторым входом блока управления и первым управляющим входом арифметико-логического блока, информационный вход которого соединен с выходом блока элементов ИЛИ, информационный выход арифметико-логического блока соединен с вторым входом первого мультиплексора, третий вход которого соединен с информационным входом устройства, выход первого мультиплексора соединен с первым информационным входом блока ассоциативной памяти, адресный вход записи которого соединен с выходом счетчика адреса записи, даторой информационный вход блока ассоциативной памяти соединен с первым выходом блока объединения списков, первый информационный выход - соединен с первым входом блока объединения списков , с вторыми входами второго и третьего мультиплексоров, с вторым входом блока элементов ИЛИ, второй ,информационный выход блока ассоци ативной Памяти соединен с вторым входом блока объединения списков и с третьим входом второго мультиплексора, второй выход блока объединения списков подключен к четвертому входу второго мультиплексора, третий выход подключен к третьему информационному входу блока ассоциативной памяти и к первому входу четвертого мультиплексора, третий вход блока

объединения списков подключен к выходу счетчика адреса списка и к второму входу четвертого мультиплексора, выход второго мультиплексора соединен с числовым входом блока оперативной памяти , выход третьего мультиплексора соединен с информационным выходом устрой ства, выход четвертого мультиплексора соединен с адресным входом блока оперативной памяти, третий вход блока управления соединен с входом готовности устройства, четвертый вход соединен с управляющим выходом блока ассоциативной памяти, первый, второй и третий выходы блока управления соединены соответственно с входами .управления записью, опросом и стиранием блока ассоциативной памяти, выходы с четвертого по двенадцатый блока управления соединены сро±ветственной с управляющими входами блока фор мирования команд, блока объединения списков, с вторым управляющим входом арифметико-логического блока, с управляющими входами четырех мультиплексоров, счетчика адреса записи и счетчика адреса списка, тринадцатый выход блока управления соединен с выходом готовности устройства.

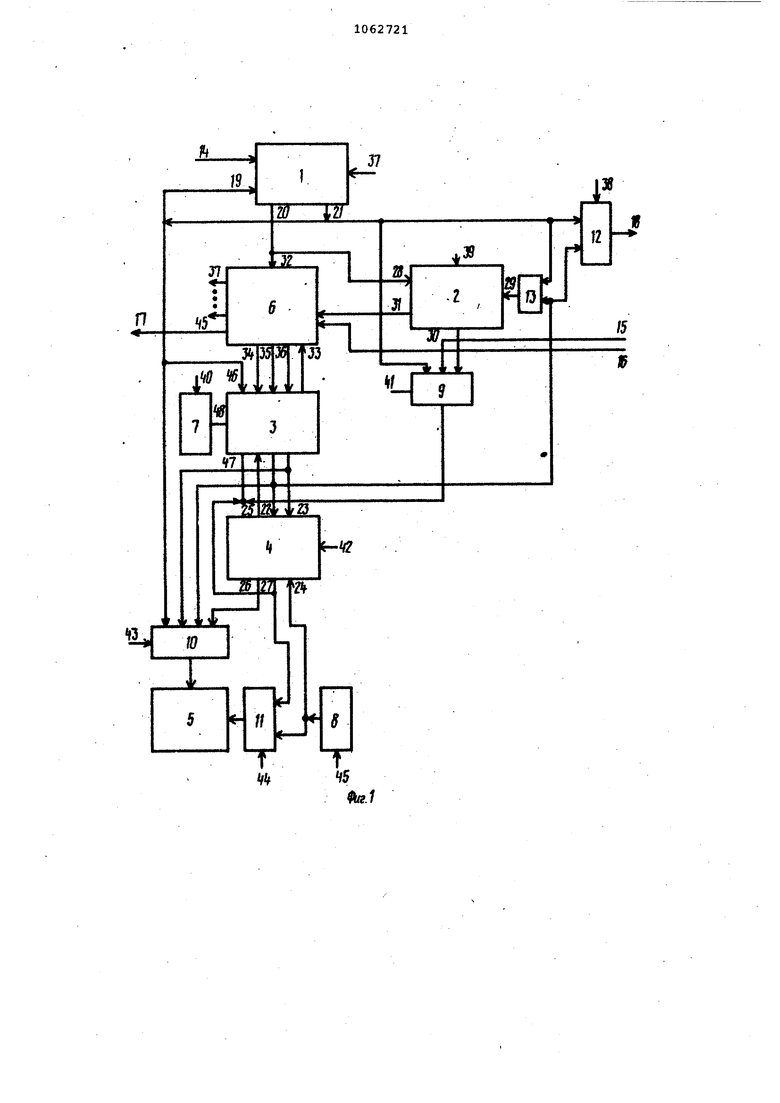

Кроме того, блок формирования команд содержит узел памяти команд, счетчик адреса команды, счетчик сдвигов и регистр команды, причем первый вход счетчика адреса команды соединен с первым входом блока, второй вход - с ВТ01Ж1М входом блока, выход счетчика адреса команды подключен к адресному входу узла памяти команд, счетный вход соединен с выходом переполнения счетчика сдвигов, вход разрешения приема кода соедин,ен с управляющим входрм блока, выход узла памяти команд соединен с входом регистра команды, выход старших разрядов KoTojporo соединен с вторым выходом блока, выход младших разрядов соединен с первым выходом блока, вход сдвига регистра команды соединен с счетным входом счетчика сдвигов и с управляющим входом блока.

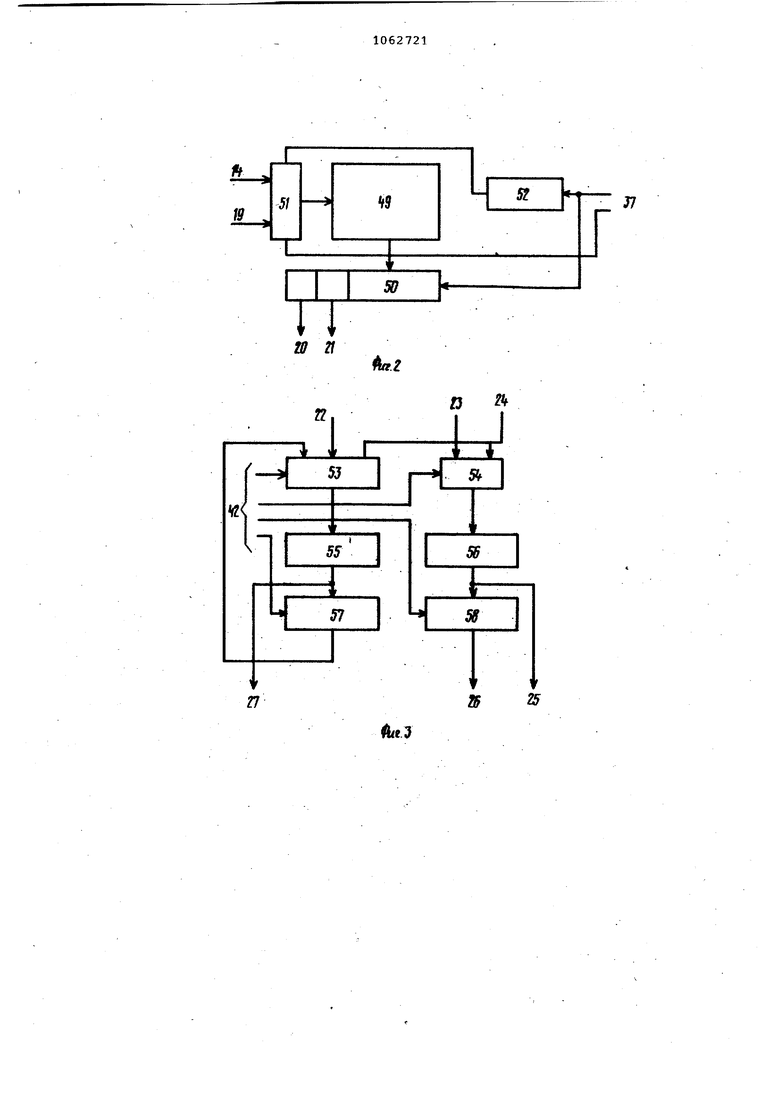

Причем блок объединения списков содержит первый и второй мультиплексоры и четыре регистра/ гфичём первые входы первого и второго мультиплексоров соединены соответственно ci первым и вторым входами блока, входы подключены к третьему входу блока, выход первого мультиплексора соединен с входом первого регистра, выход второго мультиплексора соединен с вхйдом второго регистра, выход первого регистра срединен с входом третьего регистра и с третьим выходом блока, выход второго регистра соединен с входом четвертого регистра и с первым выходом блока,

выход третьего регистра подключен к третьему входу первого мультиплексора, выход четвертого регистра под ключен к второму выходу блока, входы разрешения приема и выдачи кода третьего и.четвертого регистров и управляющие входы мультиплексоров соединены с управляющим входом блока.

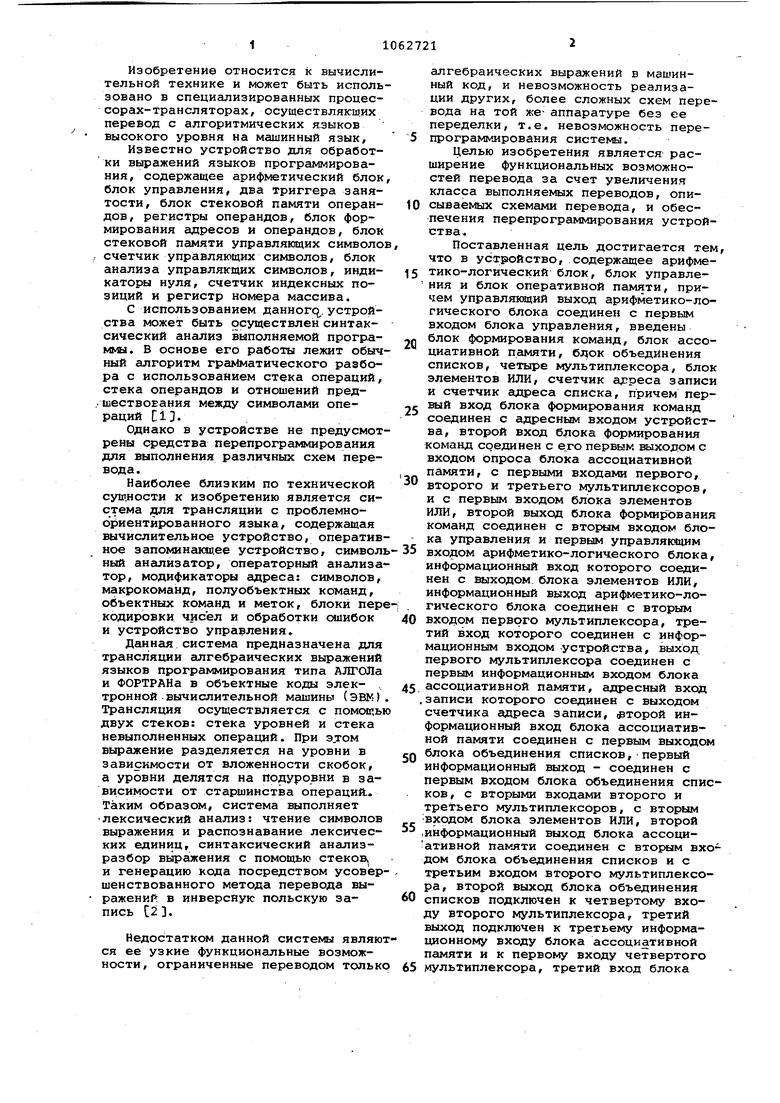

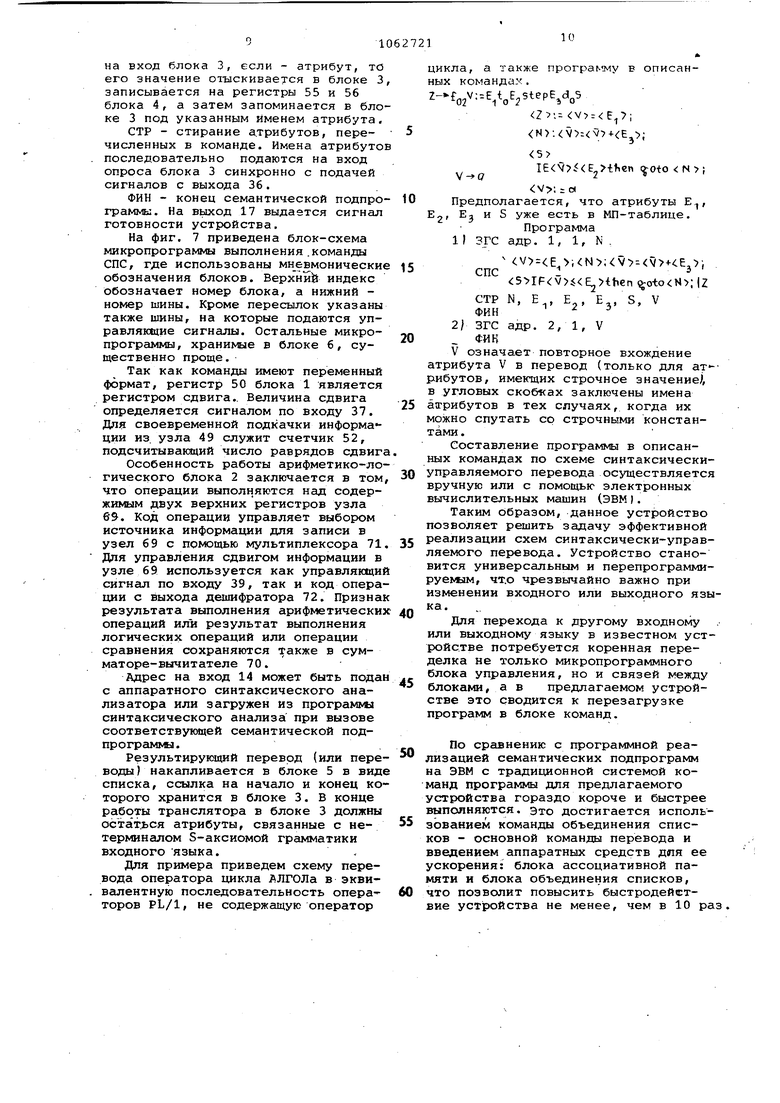

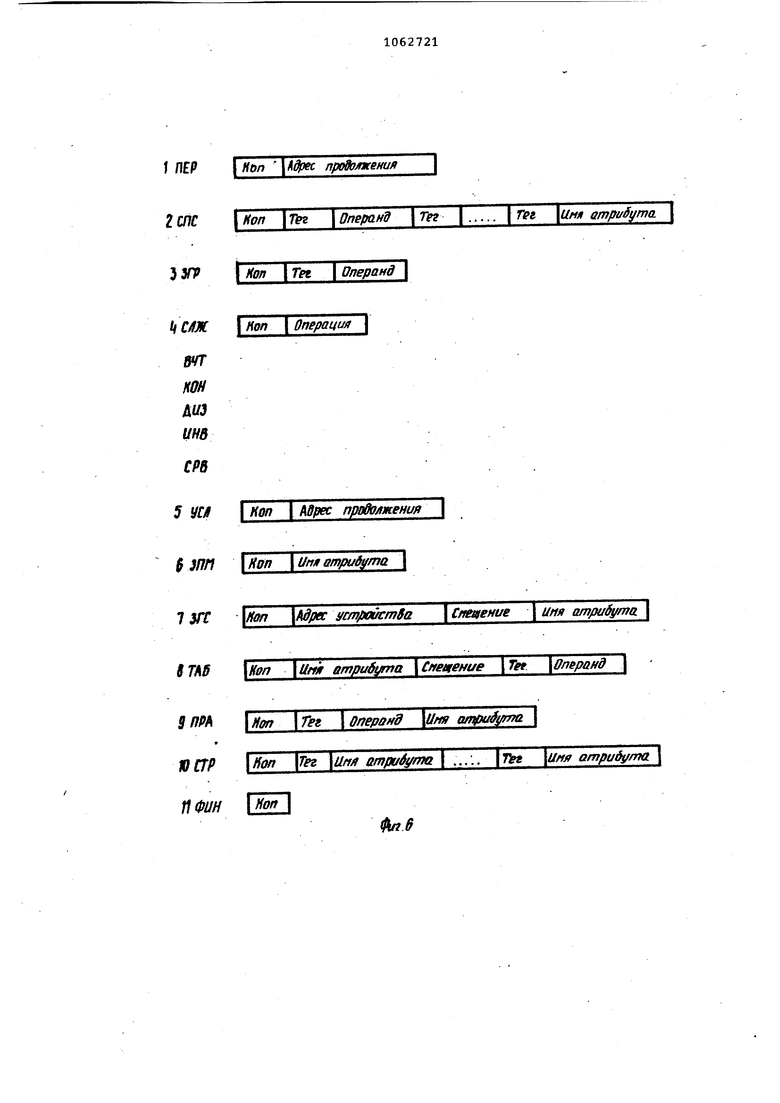

При этом блок управления содержит узел памяти микрокоманд, регистр адреса команды, дешифратор адреса, дешифратор тега, первый и второй мультиплексоры, причем входы первого мультиплексора соединень соответственно с первым, третьим и четвертым входами блока и с выходами дешифратора тега, вход которого соединен с вторым входом блока и с вхо-дом стад)ших разрядов регистра адреса команды, выход первого :мульти-плексора подключен к управляющему входу второго мультиплексора, первый и второй входы которого соединены соответственно с первым и вторым выходами узла Пс1мяти микрокоманд выхбд соединен с входом младших разрядов регистра адреса команды, выход регистра адреса команды подключен k входу -деиифратора адреса, выход которого подключен к адресному входу узла памяти микрокоманд, третий выход которого подключен к управляющему входу регистра адреса команды, четвертый выход узла памяти микро команд подключен к управляющему вхог ду первого мультиплексора, выходы начиная с пятого подключены соответственно к выходам блока, начиная с первого выхода. , Кроме того, арифметико-логический блок содержит узел стековой памяти, сумматор-вычитатель, элементы И, ИЛИ НЕ, мультиплексор и дешифратор кода опергщии, причем первый и второй выходы узла стековой памяти подключены соответственно к первому и втррому входам сумматора-илчитателя, первый и второй выходы знаковы: разрядов подключены к входам элементов И и ИЛИ, первый выход знакового разряда прдХлючен к входу элемента НЕ, первый выход cyMMaiTopa-вычитателя и . каходы элементов И, ИЛИ, НЕ подклю- чены к соответствующим информацирнным входам мультиплексора, выход которого подключен к информещиониому входу узла стековой памяти,управляющие вхрды которого соединены соответственно с первым выхрдом дешифратора кода опергщии и с вторым управляющим входом блока, входы дешифратора кода операции соединеиы соответственно с первым и вторым управляющими входами блока второй выход соединеи с управляющим входом мультиплексрра, третий выход соединен с управляющим входом сумматора- вычитйтеяя, первый выход узла стековой памяти соединен с информациоиньдм выходом блока, второй выход сумматора-вычитателя соединен с управляющим выходом блока. На фиг. 1 представлена структурная схема устройства; на фиг. 2 то же, блок формирования команд; на фиг. 3 - то же, блок объединения списков; на фиг. 4 - то же, блок управления,- на фиг. 5 - то же, ариф метико-логического блока; на фиг. б форматы команд, выполняекых устрой ством; на фиг. 7 - блок-схема микро программы выполнения команды объединения списков (СПС). Устройство содержит блок 1 формирования команд, арифметико-логиче кий блок 2,.блок 3 ассоциативной памяти, блок 4 объединения списков, блок 5 оперативной памяти, блок 6 управления, счетчик 7 адреса записи счетчик 8 адреса списка, мультиплек соры 9-12, блок 13 элементов ИЛИ. , При этом устройство имеет адресный вход 14, информационный вход 15 вход 16 готовности, выход 17 готовности и информационный выход 18 уст ройства, адресный вход 19 и два выхода 20 и 21 блока формирования команд, входаз 22-24 и выходы 25-27 блока объединения списков, управляющий вход 28, информационный вход 29, информационный 30 и управляющий 31. выходы арифметико-логическог блока, входы 32 и 33 блока управления, выходы 34 и 45 блока управлени входы 46-48 блока ассоциативной памяти, узел 49 памяти команд, регист 50 команды, счетчик 51 адреса коман ды, счетчик 52 сдвигов, мультиплексоры 53 и 54, регистры 55-58, узел 59памяти микрокоманд, дешифратор 60тега, мультиплексоры 61 и 62, регистр 63 адреса команды, дешифратор 64 адреса, выходы 65-68 узла 59 узел 69 стековой памяти, сумматорвычитатель 70, мультиплексор 71, детиифратор, 72 кода операции, злементы И 73, ИЛИ 74 и НЕ 75. Устройство работает следующим .образом. Семантические программы, осущест вляющие перевод (например, с входного языка на машинный I, можно задать в виде схем синтаксическиуправляемого перевода, в которых каждому правилу грамматики входного языка ставится в соответствие на бор перевода. Семантическая информация представляется значениями множества атрибутов, связанных с каждым нетерминалом грамматики. Ниже рассматриваются схемы, ориенти рованные на восходящий синтаксический анализ (так называе1 &:1е З-атри бутные схемы). При каждой редукции, выполняемой синтаксическим анализатором, происходит вызов семантической под программа, которая в данном случае задается набором правил перевода. Переменные, входящие в правила перевода, называются атрибутами перевода. Каждому нетерминалу входной грамматики, таким образом, соответствует набор атрибутов перевода. Правила перевода представляют собой операторы присваивания атрибутам новых зна чений, задаваемых константами или выражениями , условные операторы типа if-fi или if-then-ejse и управлякадие операторы. Все эти операторы легко представляются командами, приведенными на фиг. 6. Атрибуты могут принимать строчные, числовые или логические значения. Таким образом, на адресный вход 14 устройства поступает адрес семантической подпрограмма, заданной посредством схели перевода и записанной в виде последовательности команд в блоке 1. Имена атрибутов вместе с их значениями хранятся в блоке 3. Для атрибутов, имеющих строчное значение, в бЛ|Оке 3 вместе с именами атрибутов хранятся ссылки на начало и конец списка, в виде которого в блоке 5 хранятся стро-. ки-переводы. Это делается для удобства при работе со строками при выполнении правил перевода. Список содержит липъ терминальную крону дерева (графа) перевода. Совокупность блока 3 и счетчика 7 образуют аппаратную реализацию так называемой МП-таблицы (структуры данных), сочетающей свойства стека и таблицы: запись производится только в головной элемент, а считывание возможно из первого элемента, начиная от головного, содержимое поля признака которс-. го совпало с признаком опроса. В качестве признаков выступают имена атрибутов. Числовые значения атрибутов обрабатваются в блоке 2. Рассмотрим выполнение каждой из команд, приведенных на фиг. 6. ПЕР - переход. По STqp команде осуществляется безусловная передача управления на указанный в команде адрес. Для этого код адреса с выхода 21 передается на вход 19. СПС - объединение списков. По этой команде происходит сборка строки из строк-значений, заданных атрибутами, и строк-констант, записанных в самой команде. В результате дешифрации тега операнда в блоке 6 определяется его тип. Операндом может быть имя атрибута.или константа. Тег указывает также тип значения атрибута: строчное, числовое или логическое и последнюю запись в команде переменного формата (признак конца). Если операнд - имя атрибута, то оно передается на вход опроса блока 3, далее происходит поиск данног узла в блоке ассоциативной памяти, считывание соответствукшей ему информйции И передача ее на 22 и 23 блока 4. Информация эта представляет собой ссылки (адреса) на начало и конец списка, содержащего строчное значение данного атрибута. В блоке 4 адреса записываются на регистры 55 и 56. Далее производитс считывание следующего операнда. Есл операнд - имя атрибута, то повторяются описанные действия, адреса первого (предыдущего ) списка переписываются на регистры 57 и 58 блока 4, далее производится объединени списков, для чего адрес конца первого списка записывается в головной элемент второго списка. Для этого содержимое регистра 58 передается н вход мультиплексора 10, а содержимо регистра 55 - на вход мультиплексор 11. Адреса начала и конца,результирующего, списка записаны в регистрах 55 и 56. Если операнд - строка - ко станта, го для нее формируется элементарный список, ссылки на начало и конец которого записываются в регистры блока 4. При этом строка посимвольно передается из блока 1 на один из входов мультиплексора 10, а на адресный вход блока 5 через му типлексор 11 подается содержимое счетчика 8, которое увеличивается н единицу при записи каждого нового слова в блок 5. Содержимое счетчика 8 до и после записи символа строки передается на вход 24 и записывается в регистри 55 и 56 блока 4 для дальнейшего объединения списков. Если в команде встречается имя атри бута, имеющего нестрочное значение, то оно преобразуется в строку, и дл нее генерируется.элементарный списо как для строки-константы. Если тег указывает, что имя атрибута появляе ся в правиле повторно, то в блок 5 записывается элементарный списокуказатель на начало и конец повто.ряемого участка результирукадего спи ка. Для этого указанный в команде атрибут отыскивается в блоке 4, и, соответствукщие ему ссылки записываются в блок 5 по адресу, задаваемому счетчиком 8. Содержимое счетчика 8 также заносится в регистры блока 4 для дальве4)шего объединения списков. Ссылки на полученный в конце выполнения команды результирующий список записываются в блок 3 под именем атрибута, указанного в команде. ЗГР - загрузка значения операнда в блок 2. Операндом может быть или имя атрибута, -тогда загружается зна чение ( числовое. )атрибута или целая константа. Если операнд - имя атриб та, то оно отыскивается в блоке 3, значение передается с входа 22 через элемент ИЛИ 13 на вход 29 блока 2, где заноситсяв узел 69. Если операнд - константа, то ее значение поступает в блок 2 из блока 1 f выход 21 ). Арифметические и логические команды. Как показывает опыт построения схем перевода, минимальный набор арифметико-логических команд должен содержа.ть операции сложения (СЛЖ), вычитания(ВЧТ/, конъюкции (кон), дизъюнкции (ДИЗ), инферсии 1ИНВ), Этот набор может быть расширен в целях повышения эффективности реализации схем перевода. При выполнении этих команд с выхода 20 блока 1 на вход 28 блока 2 передается код операции. Результат выполнения операции остается в блоке 2. СРВ - сравнение. При выполнении этой команды происходит сравнение двух операндов, хранящихся в узле 69 блока 2. Над операндами выполняется операция отношения, указанная в команде. Результатом этой команды может быть значение Истина, если отношение выполняется, или Ложь, если не выполняется. Результат также остается в узле 69. УСЛ - условный переход. Если рез ультат выполнения предыдущей команды - Ложь (сигнсш на выходе 31, то выполняется переход по указанному адресу, если - Истина, то выполняется следующая команда. ЗПМ - запись результата выполнения операции из блока 2 в блок 3 под именем атрибута, указанного в команде. Для этого кодс выхода 30 через мультиплексор 9 передается на информационный вход 47 блока 3. зге - загрузка значения атрибута извне. Для внешнего оборудования указывается адрес устройства и смещение. Адрес и смещение последовательно передаются на выход 18 через мультиплексор 12, а информация, принимаемая на вход 16, поступает затем в блок 3. Внешним источником информации может быть, например, таблица символов. Признаком готовности внешнего оборудования служит сигнал на входе 16. ТАБ - запись информации в таблицу символов. На выход 18 сначала передается адрес элемента таблицы символов, хранимый под именем атрибута в блоке 3, затем смещение из блока I, затем значение операндаатрибута или константы. Далее устройство переходит в режим ожида1ния сигнала готовности по входу 16. ПРА - присваивание значения атрибута. Если операнд - константа, то она передается с выхода 21 блока 1

на вход блока 3, если - атрибут, то его значение отыскивается в блоке 3 записывается на регистры 55 и 56 блока 4f а затем запоминается в блоке 3 под указанным именем атрибута.

СТР - стирание атрибутов, перечисленных в команде. Имена атрибутов последовательно подаются на вход опроса блока 3 синхронно с подачей сигналов с выхода 36.

ФИН - конец семантической подпрограммы. На выход 17 выдается сигнал готовности устройства.

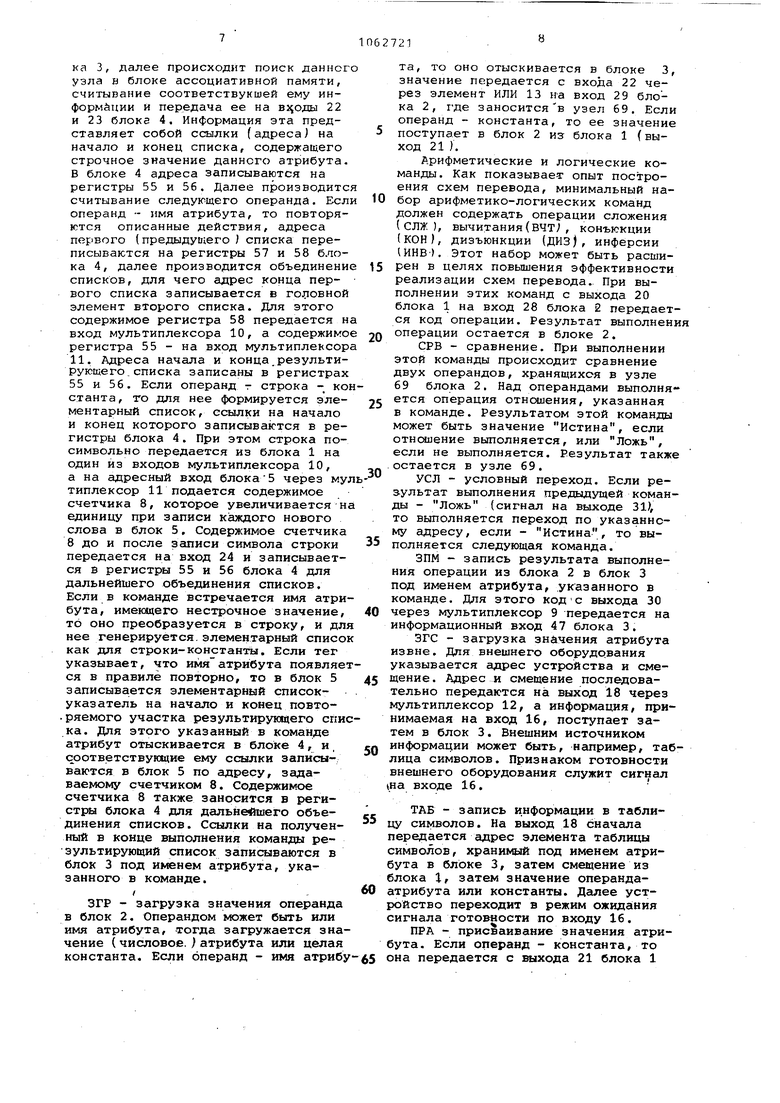

На фиг. 7 приведена блок-схема микропрограммы выполнения.команды СПС, где использованы мн евмоническне обозначения блоков. Верхний индекс обозначает номер блока, а нижний номер шины. Кроме пересылок указаны также шины, на которые подаются управляющие сигналы. Остальные микропрограммы, храни1 ие в блоке б, существенно проще.

Так как команды имеют переменный формат, регистр 50 блока 1 является регистром сдвига.. Величина сдвига определяется сигналом по входу 37. Для своевременной подкачки информа ции из. узла 49 служит счетчик 52, подсчитывающий число разрядов сдвига

Особенность работы арифметико-логического блока 2 заключается в том, что операции выполняются над содержиьвлм двух верхних регистров узла в9. Код операции управляет выбором источника информации для записи в узел 69 с помощью мультиплексора 71. Для управления сдвигом информации в узле 69 используется как управляющий сигнал по входу 39, так и код операции с выхода дешифратора 72. Признак результата выполнения арифметических операций или результат выполнения логических операций или операции сравнения сохраняются также в сумматоре-вычитателе 70.

Адрес на вход 14 может быть подан с аппаратного синтаксического анализатора или загружен из программа синтаксического анализа при вызове соответствующей семантической подпрограмьвл.

Результирующий перевод (или переводы) накапливается в блоке 5 в виде списка, ссылка на начало и конец которого хранится в блоке 3. В конце работы транслятора в блоке 3 должны остагг.ься атрибуты, связанные с нетерминалом S-аксиомой грамматики входного языка.

Для примера приведем схему перевода оператора цикла АЛГОЛа в эквивалентную последовательность операторов PL/1, не содержащую оператор

цикла, а также программу в описанных командах.

.

5

V ;:C3i

0

Предполагается, что атрибуты E, 2г Ej и S уже есть в МП-таблице.

Программа 1 I зге адр. 1, 1, N.

V E ,i

5 СПС 1

СТР N, Е Е , Е S, V ФИН

2} зге адр. 2, 1, V

0 ФИК

V означает повторное вхождение атрибута V в перевод (только для атрибутов, имеющих строчное значение), в угловых скобках заключены имена

5 атрибутов в тех случаях, когда их можно спутать со строчными константами.

Составление программы в описанных командах по схеме синтаксическиуправляемого перевода осуществляется

0 вручную или с помощью электронных вычислительных машин (ЭВМ).

Таким образом, данное устройство позволяет решить задачу эффективной реализации схем синтаксически-управ5ляемого перевода. Ус-тройство становится универсальным и перепрограммируемлм, чт.о чрезвычайно важно при изменении входного или выходного языка. ,.

0

Для перехода к другому входному или выходному языку в известном устройстве потребуется коренная переделка не только микропрограммного блока управления, но и связей между

5 блоками, а в предлагаемом устройстве это сводится к перезагрузке программ в блоке команд.

По сравнению с программной реа0лизацией семантических подпрограмм на ЭВМ с традиционной системой команд программы для предлагаемого устройства гораздо короче и быстрее выполняются. Это достигается исполь5зованием команды объединения списков - основной команды перевода и введением аппаратных средств для ее ускорения: блока ассоциативной памяти и блока объединения списков,

0 что позволит повысить быстродействие устройства не менее, чем в 10 раз

ft

J/

w

IT

W 21

.1

i

5J

W

55

U57

L

5

-

Л

Г

Z

fj Й

|Ч:р

5

58

| название | год | авторы | номер документа |

|---|---|---|---|

| ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 1989 |

|

RU2028663C1 |

| КОНВЕЙЕРНЫЙ ПРОЦЕССОР | 1992 |

|

RU2032215C1 |

| Ассоциативный матричный процессор | 1981 |

|

SU1005065A1 |

| Устройство для управления параллельным выполнением команд в электронной вычислительной машине | 1982 |

|

SU1078429A1 |

| Вычислительная система | 1989 |

|

SU1777148A1 |

| Центральный процессор | 1991 |

|

SU1804645A3 |

| Стековое запоминающее устройство | 1987 |

|

SU1737456A1 |

| Устройство для обработки структур данных | 1990 |

|

SU1698891A1 |

| Вычислительное устройство для реализации логических функций | 1983 |

|

SU1269130A1 |

| Микропроцессор | 1985 |

|

SU1330634A1 |

1. УСТРОЙСТВО ДЛЯ СИНТАКСИЧЕСКИ-УПРАВЛЯЕМОГО ПЕРЕВОДА, СОдержсицее арифметико-логический блок, блок управления и блок оперативной памяти, причем управляющий выход арифметико-логического блока соединен с первым входом блока управления, отличающееся тем, что, с цельй расширения функциональных возможностей путем увеличения класса выполняеких переводов и обеслечения перепрогрё1м« ирования, в него введены блок формирования команд, блок ассоциативной памяти, блок объединения списков, четыре мультиплексора, блок элементов ИЛИ, счетчик адреса записи и счетчик адреса списка, причем первый вход. блока формирования команд соединен с адресным входом устройства, второй вход блока формирования команд соединен с его первым выходом, с входом опроса блока ассоциативной памяти, с первыми входами первого, второго и третьего мультиплексоров и с первым входом блока элементов ИЛИ, второй выход блока формирования команд соединен с вторяз1м входом блока управления и первым управляющим входом арифметико-логического блока, информационный вход которого соединен с выходом блока элементов ИЛИ, информационный выход арифметико-логического блока соединен с .вторым входом первого мультиплексора, третий вход которого соединен с информационным входом устройства, выход первого мультиплексора соединен с первым информационным входом блока ассоциативной памяти, адресный вход записи которого соединен с выходом счетчика адреса записи, второй информационный вход блока ассоциативной памяти соединен с первым выходом блока объединения -списков, первый информационный выход соединен с первым входом блока объединения списков, с вторымивходами второго и третьего мультиплексоров, с вторым входом блока элементов ИЛИ, второй информационный выход блока ассоциативной памяти соединен с вторым входом блока объединения списков О и с третьим входом второго мульти.плексора, .второй выход блока объеС динения списков подключен к четвертому входу второго мультиплексб-г ра, третий выход подключен к третьему информационному входу блока ассоциативной памяти и к первому входу четвертого мультиплексора, третий вход блока объединения списков подключен к выходу счетчика адреса списка и к второму входу четвертого мультиплексора, выход второго мультиплек-j сора соединен с числовым входом блока оперативной памяти, выход третьего мультиплексора соединен с информационным выходом устройства, выход четвертого мультиплексора соединен С адресным входом блока оперативной памяти, третий вход блока управления соединен с входом готовности устройства, четвертая вход соединен с управляющим выходом блока ассоциативной памяти, первый, второй и третий выходы блока управления соединены соответственно с входа ми управления записью, опросом и стиранием блока ассоциативной памя;Ти, выходы с четвертого по двенадцатый блока управления соединены

27

№Z5

}f J3

л

n

62

% 45

5 I

L

Jff5

66

i ПЕР проОолженцй ZUIC Koft |7&г bneftaffd Тег ..... ЗУ) I Ноп Тп I Операнд }

Коп Операция

5 уел Коп {Мрес п №0олжения

$ )ЛП Ноп UniiBmpu6yma | 7 1ЛГ SТЛб 3 ПРА ЮСТР ПФиИ ycmflOKmSa Спещение иня атрибуте. атрибута Cfreifение Tft ffnfpQffd Операнд иня ад йафтяг I /foft Тег ипА атрибуггю .... | Тег ина атри6 //па ffOfTI 7Трг инл ernpvtfyrna.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для обработки выражений языков программирования | 1974 |

|

SU519715A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Система для трансляции с проблемноориентированного языка | 1976 |

|

SU674028A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Видоизменение прибора для получения стереоскопических впечатлений от двух изображений различного масштаба | 1919 |

|

SU54A1 |

Авторы

Даты

1983-12-23—Публикация

1982-06-07—Подача