Изобретение относится к области вычислительной техники, в частности к организации контроля .и отладки программ.

Известно устройство для контроля программ, содержащее счетчик команд, который подсчитывает выполненные последовательно команды, регистр для хранения содержимого счетчика команд в том случае, когда выполняется команда перехода, при этом содержимое регистра в случае ошибки выдается на выход устройства, элементы И, ИЛИ, блок вывода 1.

Известно устройство для фиксации последних адресов реализуемых команд перехода, содержащее блок памяти стекового типа со средствами индикации, управляемую счетчиком количества команд перехода, регистр адреса команд, регистр исполнительного адреса, схему прерывания ЭВМ, основную память 2.

Недостаток устройств заключается в их низкой производительности, что является следствием формирования последовательности программных событий с указанием количества циклов их выполнения, т. е. трассы выполнения программы после ее прогона в ЭВМ.

Наиболее близким по технической сущности к предлагаемому является устройство для контроля хода программ, содержащее регистр адреса, регистр предыдущего адреса, счетчик циклов, блок сравнения, блок памяти, блок управления, причем выход регистра адреса соединен с информационным входом регистра предыдущего адреса и первым информационным входом блока сравнения, второй информационный вход которого соединен с выходом регистра предыдущего адреса, первый выход - со счетным входом счетчика циклов, а второй - с первым входом блока управления, первый, второй, третий, четвертый и пятый выходы которого связаны соответственно с управляющими входами регистра адреса, регистра предыдущего адреса, счетчика циклов, блока сравнения и блока памяти 3.

Недостатком известного устройства также является низкая производительность, что является следствием формирования трассы программы после ее выполнения.

Цель изобретения - повышение производительности устройства посредством автоматического формирования трассы программы в ходе ее выполнения.

Поставленная цель достигается тем, что в устройство для фиксации трассы выполнения программы, содержащее регистр адреса, регистр предыдущего адреса, первый счетчик, блок сравнения, блок памяти, блок микропрограммного управления, коммутатор и элемент ИЛИ, причем выход регистра адреса соединен с входом регистра предыду1цего адреса и первым информационным входом блока сравнения, выход регистра предыдущего адреса соединен с вторым входом блока

сравнения, выходы равенства и неравенства которого соединены соответственно со счетным входом первого счетчика и первым адресным входом блока микропрограммного управления, первый, второй, третий, четвертый и пятый выходы блока микропрограммного управления соединены соответственно с входом записи регистра адреса, входом записи регистра предыдущего адреса, входом начальной установки первого счетчиi a, входом разрешения сравнения блока сравнения и входом записи блока памяти, информационный вход коммутатора соединен с информационным входом устройства, информационный выход первого счетчика

5 соединен с первым информационным входом блока памяти, введены регистр числа, счетчик строк, второй счетчик, блок ассоциативной памяти, причем шестой, седьмой, восьмой, девятый, десятый и одиннадцатый выходы блока микропрограммного управления

0 соединены соответственно со счетным входом счетчика строк, управляющим входом коммутатора, входом записи регистра числа, входом обращения к блоку ассоциативной памяти, с выходом останова по переполнению устройства и с выходом останова по неисправности устройства, вход задания режимов устройства соединен с первым входом ветвления блока микропрограммного управления, выход коммутатора соединен с информационным входом регистра числа,

0 выход .регистра числа соединен с информационным входом блока ассоциативной памяти и информационным выходом устройства, выход счетчиков строк соединен с входом элемента ИЛИ и со старшими информационными разрядами блока ассоциативной памяти, информационный выход которого соединен с адресным входом строк блока памяти и с первым информационным входом счетчика строк, выход кода количества ячеек и выход кода адреса зон соединены

0 соответственно с вторым входом ветвления блока микропрограммного управления и с первым информационным входом регистра адреса, вход адреса устройства соединен с вторым информационным входом регистра адреса, выход которого соединен с входом

адреса зоны блока памяти и с адресным входом блока ассоциативной памяти, выход неравенства блока сравнения соединен со счетным входом второго счетчика, выход которого соединен с вторым информационQ ным входом блока памяти, информационный выход блока памяти соединен с вторым информационным входом счетчика строк и коммутатора, выход элемента ИЛИ соединен с входом признака переполнения блока микропрограммного управления.

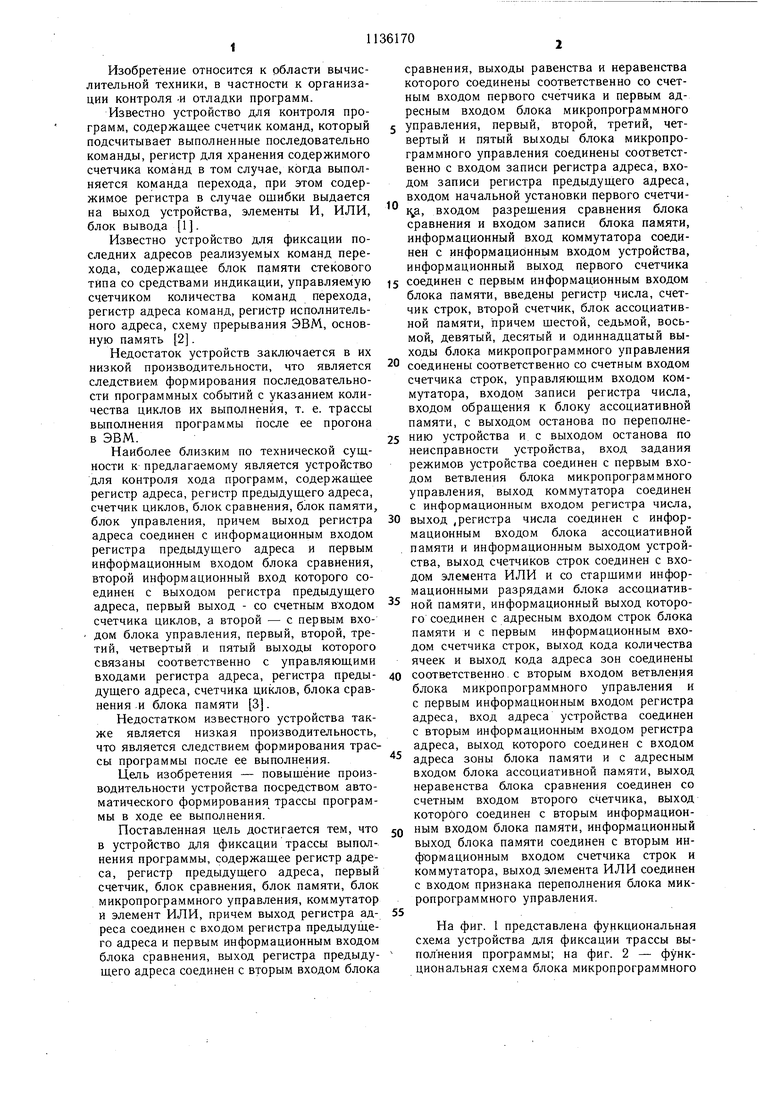

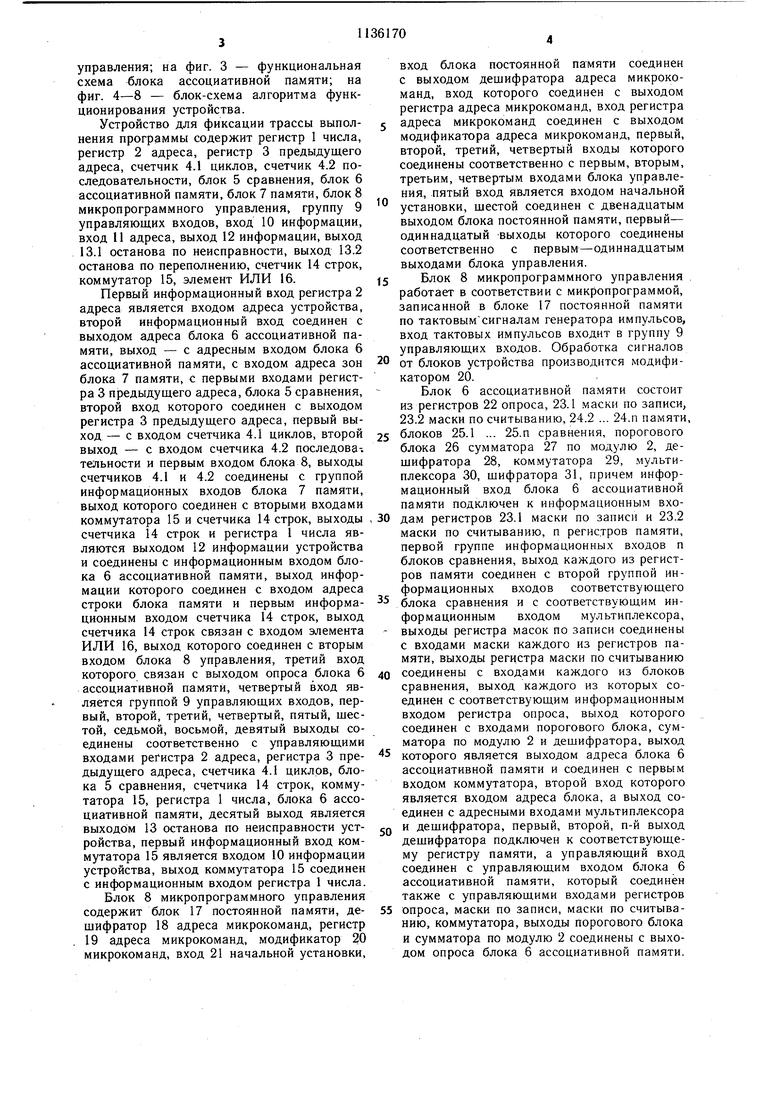

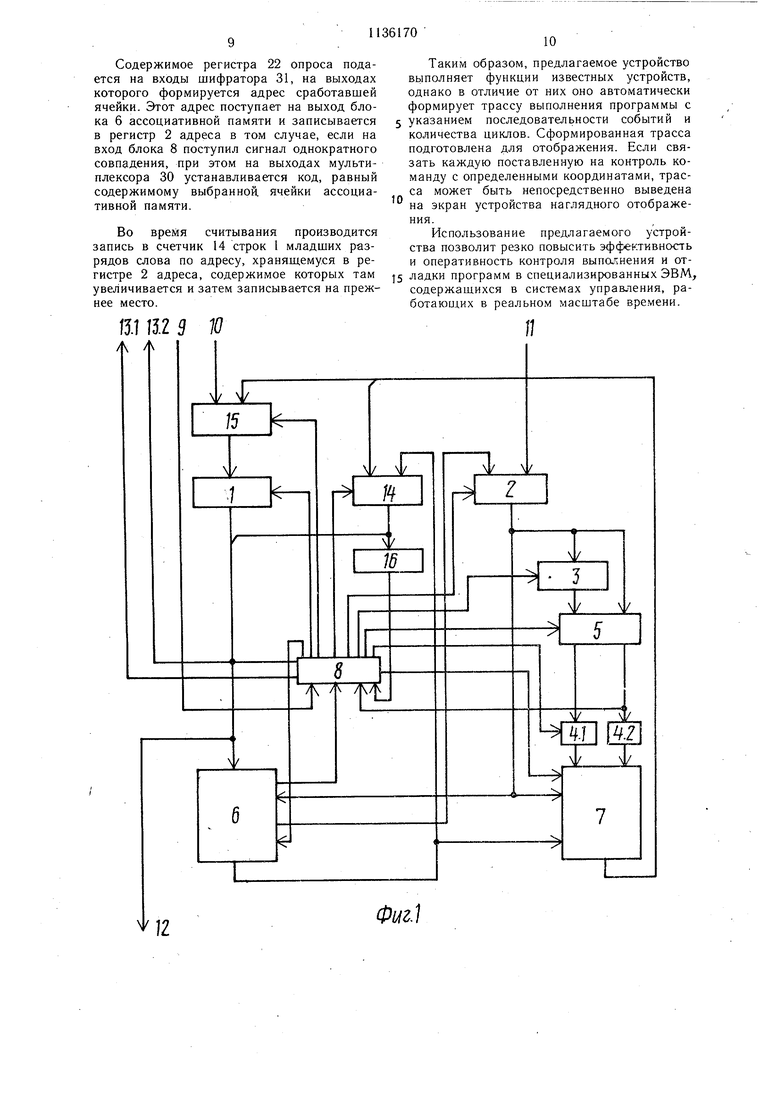

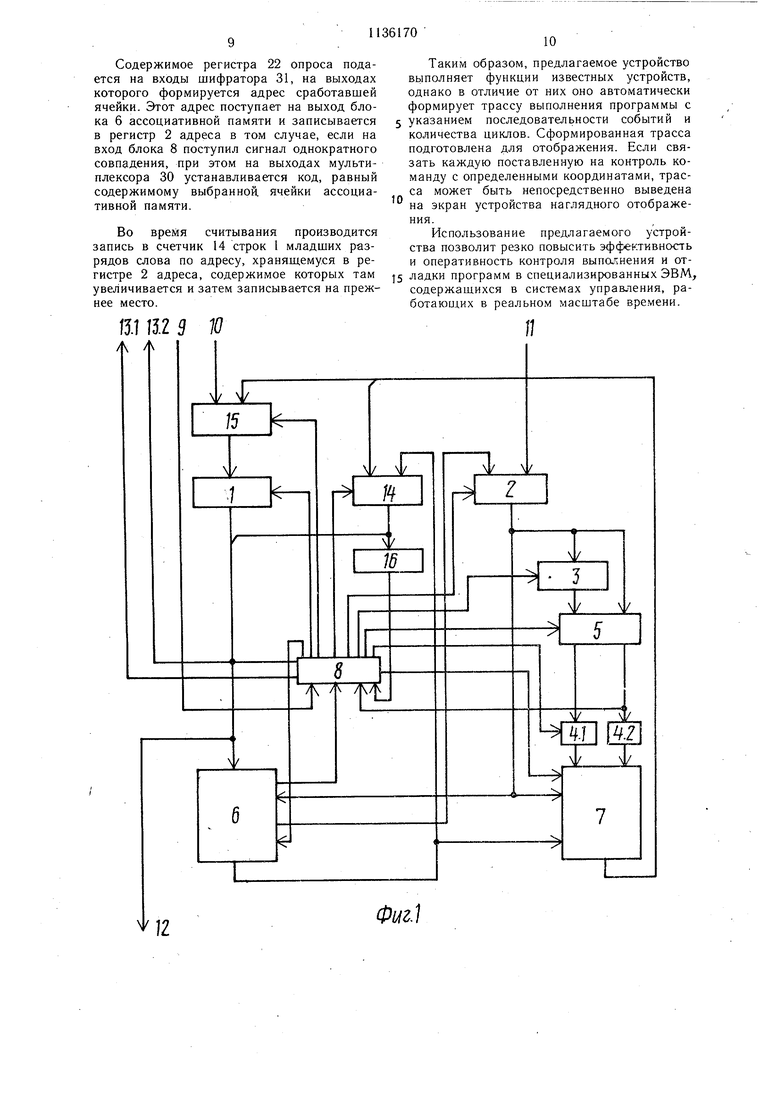

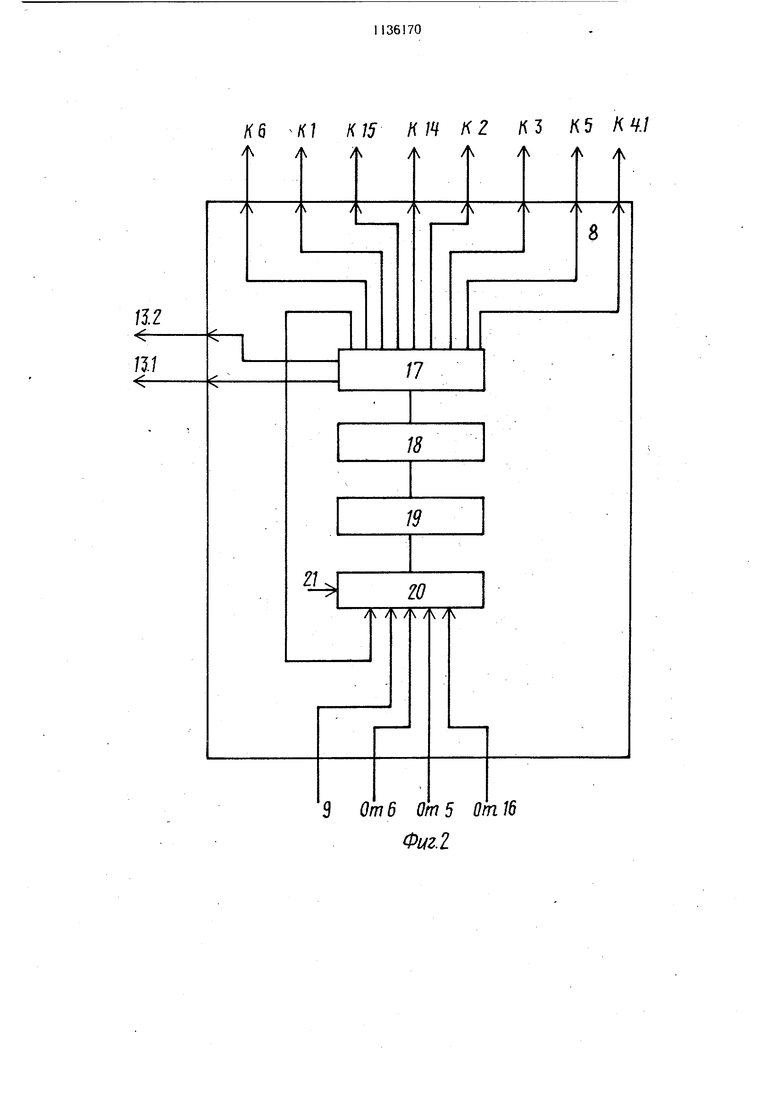

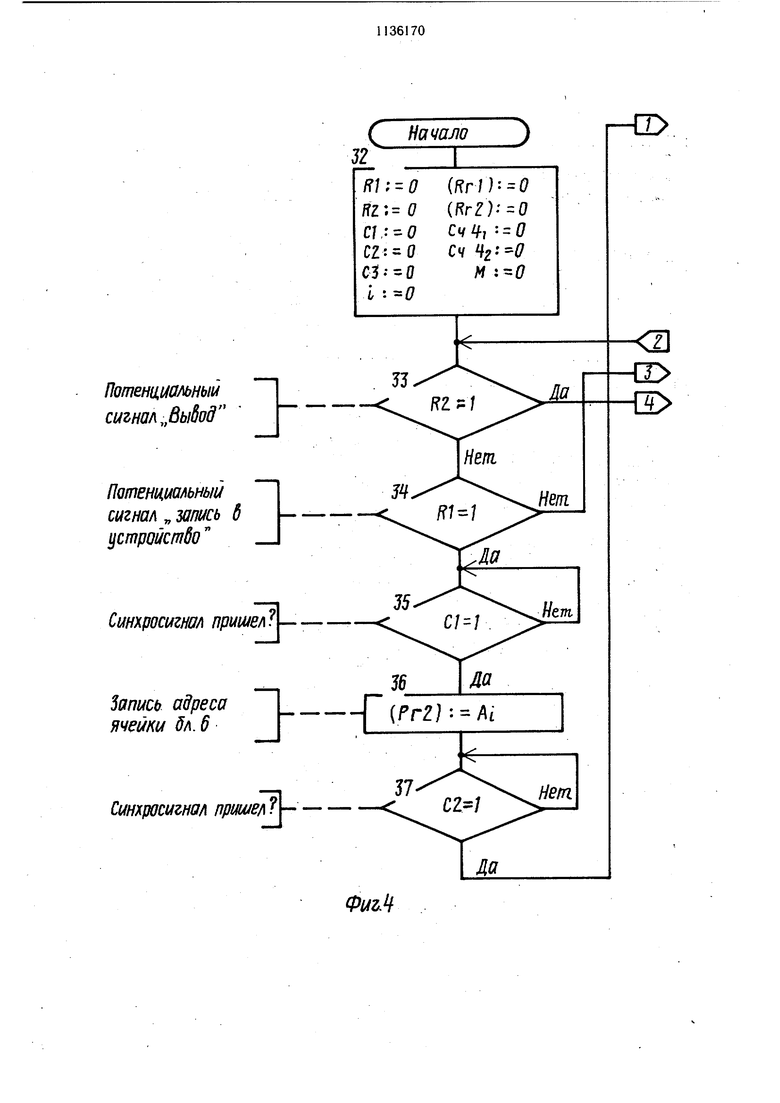

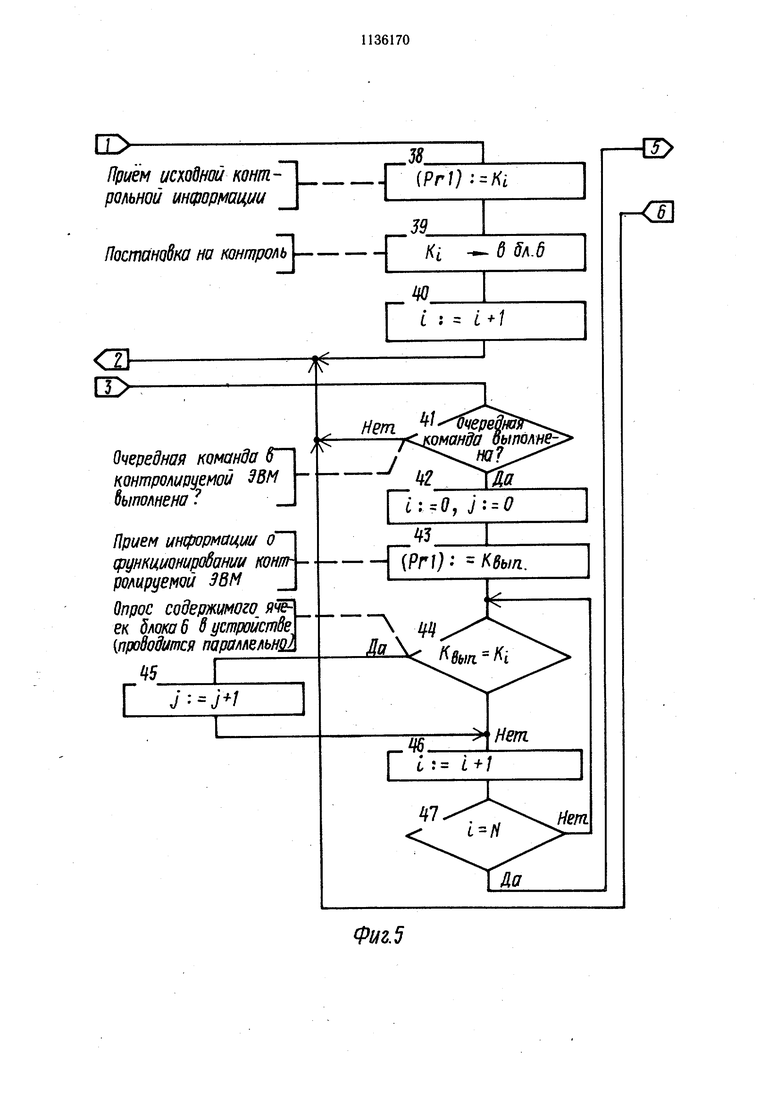

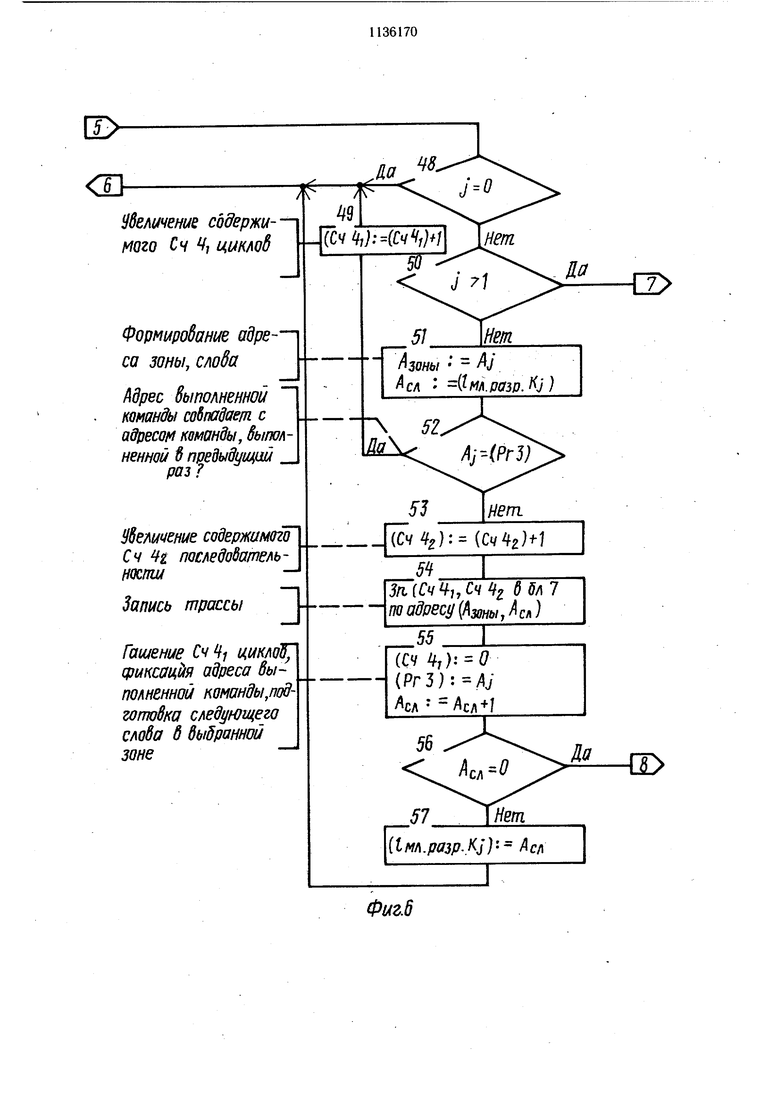

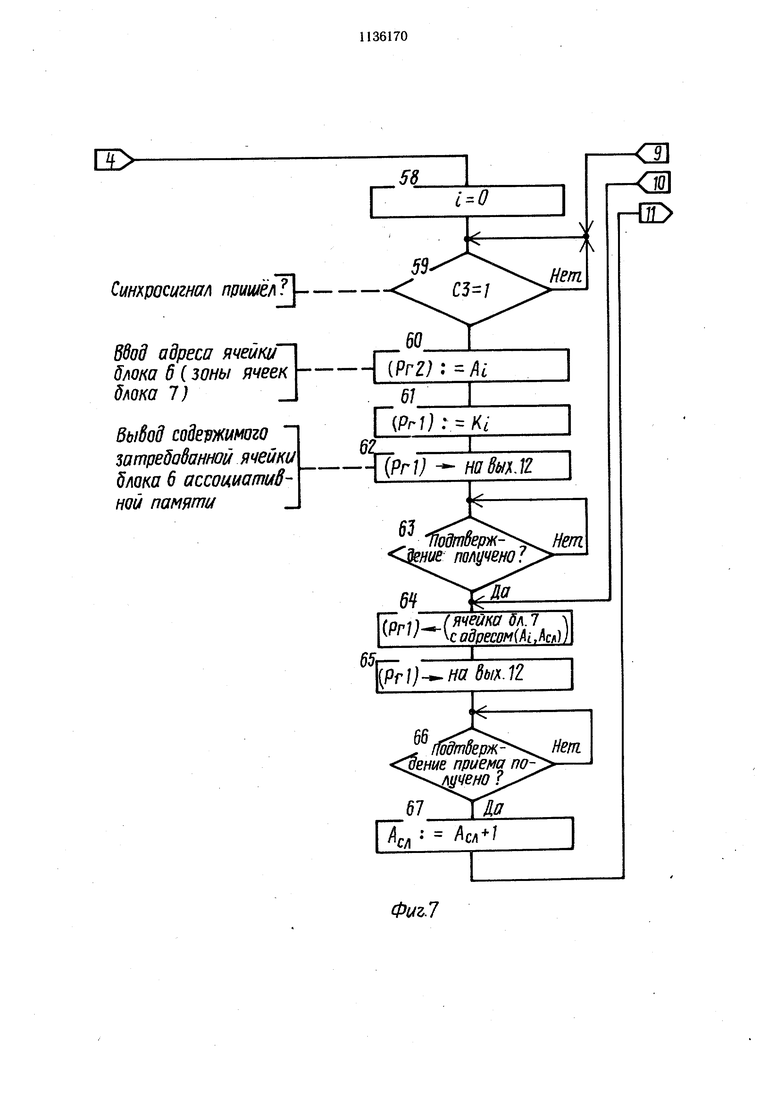

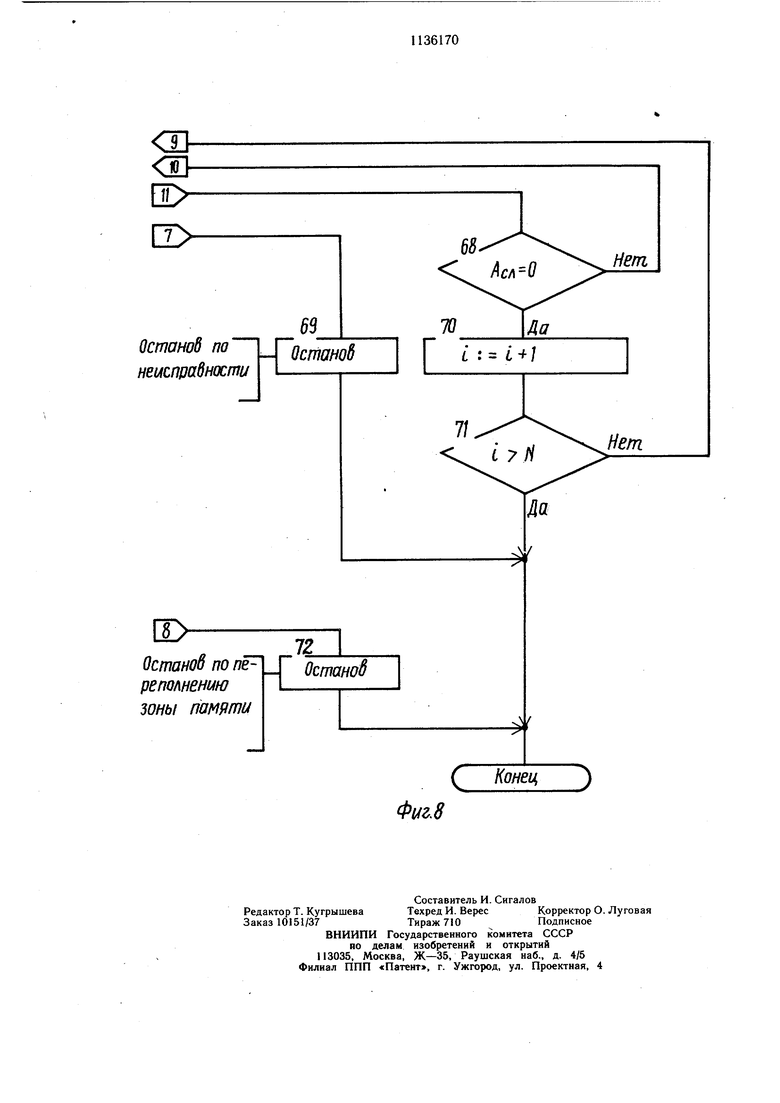

На фиг. 1 представлена функциональная схема устройства для фиксации трассы выполнения программы; на фиг. 2 - функциональная схема блока микропрограммного

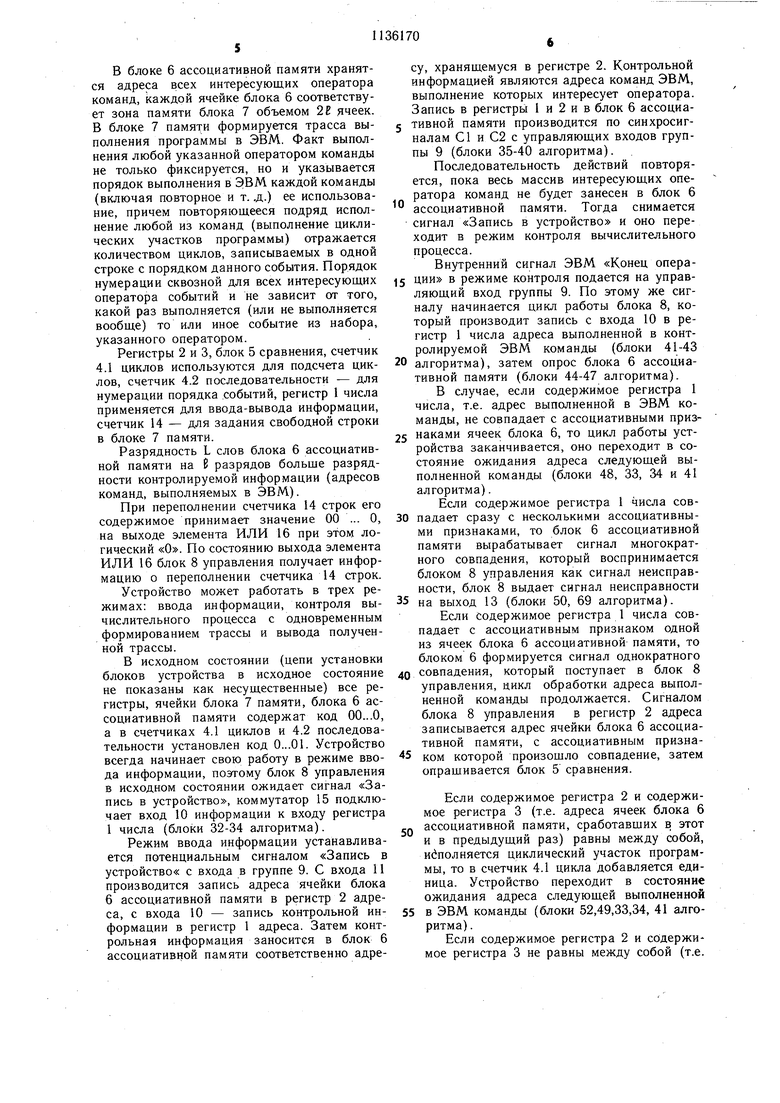

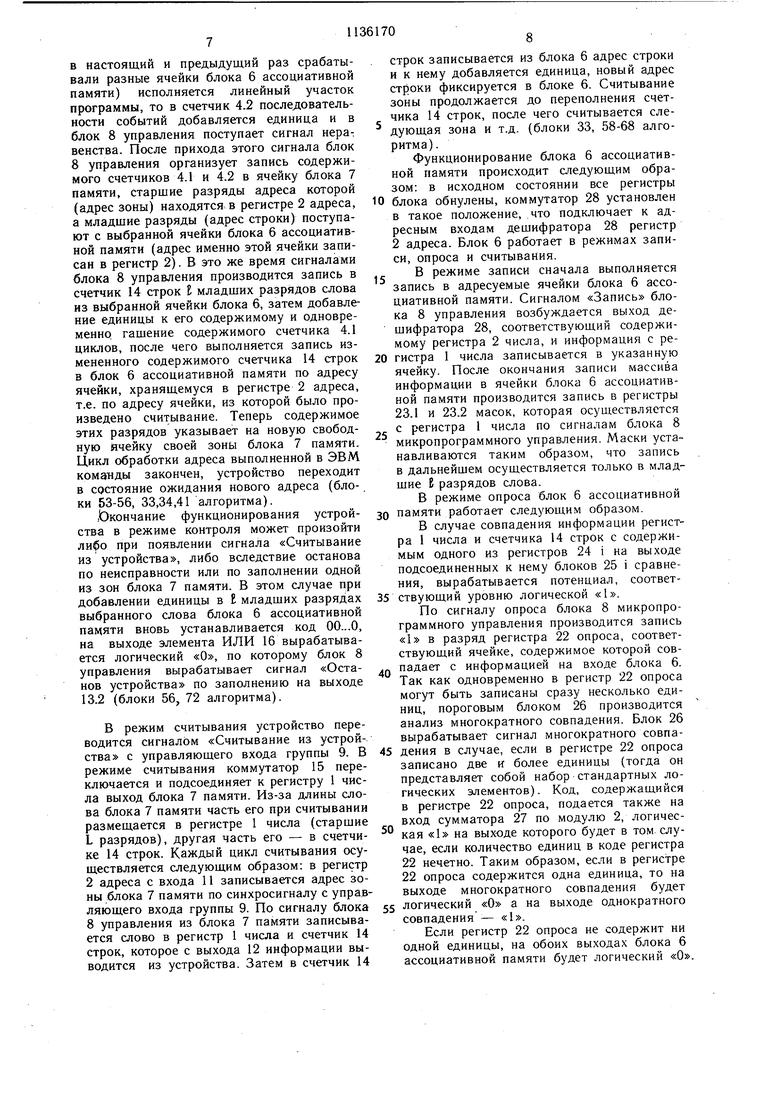

управления; на фиг. 3 - функциональная схема блока ассоциативной памяти; на фиг. 4-8 - блок-схема алгоритма функционирования устройства.

Устройство для фиксации трассы выполнения программы содержит регистр 1 числа, регистр 2 адреса, регистр 3 предыдущего адреса, счетчик 4.1 циклов, счетчик 4.2 последовательности, блок 5 сравнения, блок 6 ассоциативной памяти, блок 7 памяти, блок 8 микропрограммного управления, группу 9 управляющих входов, вход 10 информации, вход 11 адреса, выход 12 информации, выход 13.1 останова по неисправности, выход 13.2 останова по переполнению, счетчик 14 строк, коммутатор 15, элемент ИЛИ 16.

Первый информационный вход регистра 2 адреса является входом адреса устройства, второй информационный вход соединен с выходом адреса блока 6 ассоциативной памяти, выход - с адресным входом блока 6 ассоциативной памяти, с входом адреса зон блока 7 памяти, с первыми входами регистра 3 предыдущего адреса, блока 5 сравнения, второй вход которого соединен с выходом регистра 3 предыдущего адреса, первый выход- с входом счетчика 4.1 циклов, второй выход - с входом счетчика 4.2 последова-. тепьности и первым входом блока 8, выходы счетчиков 4.1 и 4.2 соединены с группой информационных входов блока 7 памяти, выход которого соединен с вторыми входами коммутатора 15 и счетчика 14 строк, выходы счетчика 14 строк и регистра 1 числа являются выходом 12 информации устройства и соединены с информационным входом блока 6 ассоциативной памяти, выход информации которого соединен с входом адреса строки блока памяти и первым информационным входом счетчика 14 строк, выход счетчика 14 строк связан с входом элемента ИЛИ 16, выход которого соединен с вторым входом блока 8 управления, третий вход которого связан с выходом опроса блока 6 ассоциативной памяти, четвертый вход является группой 9 управляющих входов, первый, второй, третий, четвертый, пятый, шестой, седьмой, восьмой, девятый выходы соединены соответственно с управляющими входами регистра 2 адреса, регистра 3 предыдущего адреса, счетчика 4.1 циклов, блока 5 сравнения, счетчика 14 строк, коммутатора 15, регистра 1 числа, блока 6 ассоциативной памяти, десятый выход является выходом 13 останова по неисправности устройства, первый информационный вход коммутатора 15 является входом 10 информации устройства, выход коммутатора 15 соединен с информационным входом регистра 1 числа.

Блок 8 микропрограммного управления содержит блок 17 постоянной памяти, дещифратор 18 адреса микрокоманд, регистр 19 адреса микрокоманд, модификатор 20 микрокоманд, вход 21 начальной установки.

вход блока постоянной памяти соединен с выходом дешифратора адреса микрокоманд, вход которого соединен с выходом регистра адреса микрокоманд, вход регистра 5 адреса микрокоманд соединен с выходом модификатора адреса микрокоманд, первый, второй, третий, четвертый входы которого соединены соответственно с первым, вторым, третьим, четвертым входами блока управления, .пятый вход является входом начальной

установки, щестой соединен с двенадцатым выходом блока постоянной памяти, первый- одиннадцатый выходы которого соединены соответственно с первым-одиннадцатым выходами блока управления.

5 Блок 8 микропрограммного управления работает в соответствии с микропрограммой, записанной в блоке 17 постоянной памяти по тактовым сигналам генератора импульсов, вход тактовых импульсов входит в группу 9 управляющих входов. Обработка сигналов

0 от блоков устройства производится модификатором 20.

Блок 6 ассоциативной памяти состоит из регистров 22 опроса, 23.1 маски по записи, 23.2 маски по считыванию, 24.2 ... 24.п памяти,

5 блоков 25.1 ... 25.П сравнения, порогового блока 26 сумматора 27 по модулю 2, дещифратора 28, коммутатора 29, мультиплексора 30, шифратора 31, причем информационный вход блока 6 ассоциативной памяти подключен к информационным входам регистров 23.1 маски по записи и 23.2 маски по считыванию, п регистров памяти, первой группе информационных входов п блоков сравнения, выход каждого из регистров памяти соединен с второй группой информационных входов соответствующего

блока сравнения и с соответствующим информационным входом мультиплексора, - выходы регистра масок по записи соединены с входами маски каждого из регистров памяти, выходы регистра маски по считыванию

соединены с входами каждого из блоков сравнения, выход каждого из которых соединен с соответствующим информационным входом регистра опроса, выход которого соединен с входами порогового блока, сумматора по модулю 2 и дешифратора, выход

5 которого является выходом адреса блока 6 ассоциативной памяти и соединен с первым входом коммутатора, второй вход которого является входом адреса блока, а выход соединен с адресными входами мультиплексора

Q и дешифратора, первый, второй, п-й выход дешифратора подключен к соответствующему регистру памяти, а управляющий вход соединен с управляющим входом блока 6 ассоциативной памяти, который соединен также с управляющими входами регистров

5 опроса, маски по записи, маски по считыванию, коммутатора, выходы порогового блока и сумматора по модулю 2 соединены с выходом опроса блока 6 ассоциативной памяти.

В блоке б ассоциативной памяти хранятся адреса всех интересующих оператора команд, каждой ячейке блока б соответствует зона памяти блока 7 объемом 2 ячеек. В блоке 7 памяти формируется трасса выполнения программы в ЭВМ. Факт выполнения любой указанной оператором команды не только фиксируется, но и указывается порядок выполнения в ЭВМ каждой команды (включая повторное и т. .д.) ее использование, причем повторяющееся подряд исполнение любой из команд (выполнение циклических участков программы) отражается количеством циклов, записываемых в одной строке с порядком данного события. Порядок нумерации сквозной для всех интересующих оператора событий и не зависит от того, какой раз выполняется (или не выполняется вообще) то или иное событие из набора, указанного оператором.

Регистры 2 и 3, блок 5 сравнения, счетчик 4.1 циклов используются для подсчета циклов, счетчик 4.2 последовательности - для нумерации порядка событий, регистр 1 числа применяется для ввода-вывода информации, счетчик 14 - для задания свободной строки в блоке 7 памяти.

Разрядность L слов блока 6 ассоциативной памяти на 6 разрядов больше разрядности контролируемой информации (адресов команд, выполняемых в ЭВМ).

При переполнении счетчика 14 строк его содержимое принимает значение 00 ... О, на выходе элемента ИЛИ 16 при этом логический «О. По состоянию выхода элемента ИЛИ 16 блок 8 управления получает информацию о переполнении счетчика 14 строк. Устройство может работать в трех режимах: ввода информации, контроля вычислительного процесса с одновременным формированием трассы и вывода полученной трассы.

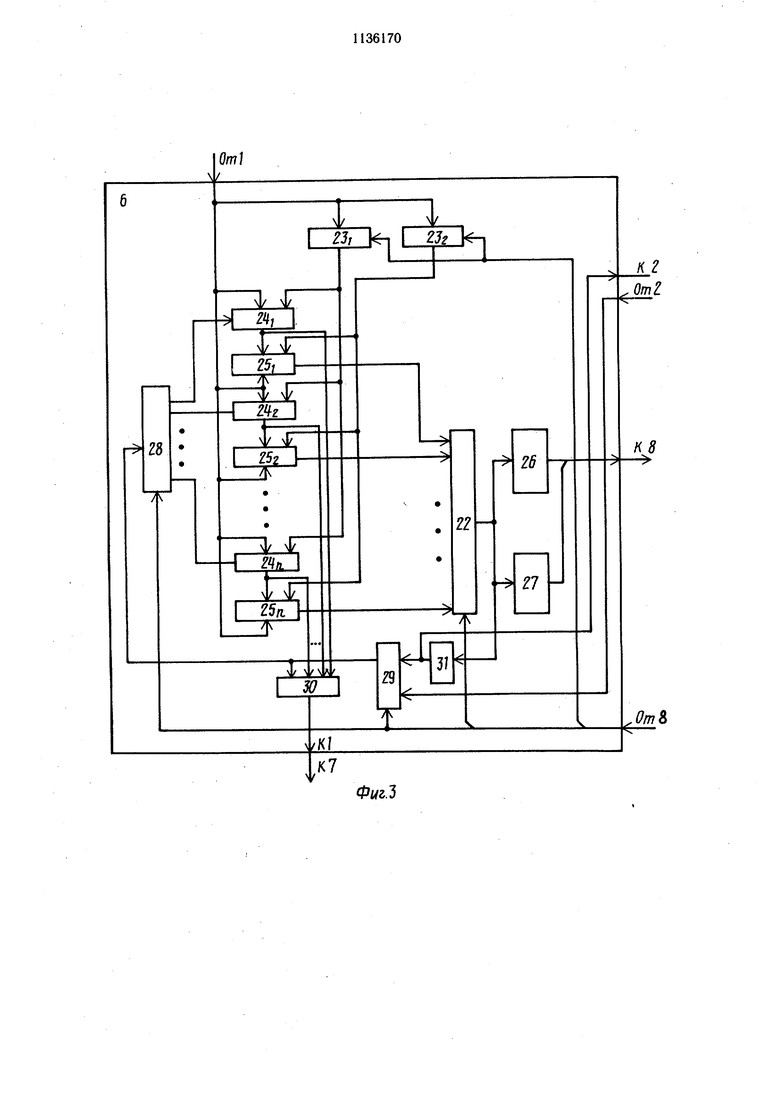

В исходном состоянии (цепи установки блоков устройства в исходное состояние не показаны как несущественные) все регистры, ячейки блока 7 памяти, блока 6 ассоциативной памяти содержат код 00...О, а в счетчиках 4.1 циклов и 4.2 последовательности установлен код 0...01. Устройство всегда начинает свою работу в режиме ввода информации, поэтому блок 8 управления в исходном состоянии ожидает сигнал «Запись в устройство, коммутатор 15 подключает вход 10 информации к входу регистра 1 числа (блоки 32-34 алгоритма).

Режим ввода информации устанавливается потенциальным сигналом «Запись в устройство с входа в группе 9. С входа 11 производится запись адреса ячейки блока 6 ассоциативной памяти в регистр 2 адреса, с входа 10 - запись контрольной информации в регистр 1 адреса. Затем контрольная информация заносится в блок б ассоциативной памяти соответственно адресу, хранящемуся в регистре 2. Контрольной информацией являются адреса команд ЭВМ, выполнение которых интересует оператора. Запись в регистрь 1 и 2 и в блок 6 ассоциативной памяти производится по синхросигналам С1 и С2 с управляющих входов группы 9 (блоки 35-40 алгоритма).

Последовательность действий повторяется, пока весь массив интересующих оператора команд не будет занесен в блок 6 ассоциативной памяти. Тогда снимается сигнал «Запись в устройство и оно переходит в режим контроля вычислительного процесса.

Внутренний сигнал ЭВМ «Конец операции в режиме контроля подается на управляющий вход группы 9. По этому же сигналу начинается цикл работы блока 8, который производит запись с входа 10 в регистр 1 числа адреса выполненной в контролируемой ЭВМ команды (блоки 41-43

алгоритма), затем опрос блока 6 ассоциативной памяти (блоки 44-47 алгоритма).

В случае, если содержимое регистра 1 числа, т.е. адрес выполненной в ЭВМ команды, не совпадает с ассоциативными признаками ячеек блока 6, то цикл работы устройства заканчивается, оно переходит в состояние ожидания адреса следующей выполненной команды (блоки 48, 33, 34 и 41 алгоритма).

Если содержимое регистра 1 числа совпадает сразу с несколькими ассоциативными признаками, то блок 6 ассоциативной памяти вырабатывает сигнал многократного совпадения, который воспринимается блоком 8 управления как сигнал неисправности, блок 8 выдает сигнал неисправности

на выход 13 (блоки 50, 69 алгоритма).

Если содержимое регистра 1 числа совпадает с ассоциативным признаком одной из ячеек блока б ассоциативной памяти, то блоком б формируется сигнал однократного

совпадения, который поступает в блок 8 управления, цикл обработки адреса выполненной команды продолжается. Сигналом блока 8 управления в регистр 2 адреса записывается адрес ячейки блока 6 ассоциативной памяти, с ассоциативным признаком которой произошло совпадение, затем опрашивается блок 5 сравнения.

Если содержимое регистра 2 и содержимое регистра 3 (т.е. адреса ячеек блока 6 ассоциативной памяти, сработавших в этот и в предыдущий раз) равны между собой, исполняется циклический участок программы, то в счетчик 4.1 цикла добавляется единица. Устройство переходит в состояние ожидания адреса следующей выполненной в ЭВМ команды (блоки 52,49,33,34, 41 алгоритма) .

Если содержимое регистра 2 и содержимое регистра 3 не равны между собой (т.е. в настоящий и предыдущий раз срабатывали разные ячейки блока 6 ассоциативной памяти) исполняется линейный участок программы, то в счетчик 4.2 последовательности событий добавляется единица и в блок 8 управления поступает сигнал нера венства. После прихода этого сигнала блок 8 управления организует запись содержимого счетчиков 4.1 и 4.2 в ячейку блока 7 памяти, старщие разряды адреса которой (адрес зоны) находятся в регистре 2 адреса, а младшие разряды (адрес строки) поступают с выбранной ячейки блока 6 ассоциативной памяти (адрес именно этой ячейки записан в регистр 2). В это же время сигналами блока 8 управления производится запись в счетчик 14 строк младщих разрядов слова из выбранной ячейки блока 6, затем добавление единицы к его содержимому и одновременно гащение содержимого счетчика 4.1 циклов, после чего выполняется запись измененного содержимого счетчика 14 строк в блок б ассоциативной памяти по адресу ячейки, хранящемуся в регистре 2 адреса, т.е. по адресу ячейки, из которой было произведено считывание. Теперь содержимое этих разрядов указывает на новую свободную ячейку своей зоны блока 7 памяти. Цикл обработки адреса выполненной в ЭВМ команды закончен, устройство переходит в состояние ожидания нового адреса (блоки 53-56, 33,34,41 алгоритма). .Окончание функционирования устройства в режиме контроля может произойти ЛИ0О при появлении сигнала «Считывание из устройства, либо вследствие останова по неисправности или по заполнении одной из зон блока 7 памяти. В этом случае при добавлении единицы в младщих разрядах выбранного слова блока 6 ассоциативной памяти вновь устанавливается код 00...0, на выходе элемента ИЛИ 16 вырабатывается логический «О, по которому блок 8 управления вырабатывает сигнал «Останов устройства по заполнению на выходе 13.2 (блоки 56, 72 алгоритма). В режим считывания устройство переводится сигналом «Считывание из устройства с управляющего входа группы 9. В режиме считывания коммутатор 15 переключается и подсоединяет к регистру 1 числа выход блока 7 памяти. Из-за длины слова блока 7 памяти часть его при считывании размещается в регистре 1 числа (старщие L разрядов), другая часть его - в счетчике 14 строк. Каждый цикл считывания осуществляегся следующим образом: в регистр 2 адреса с входа 11 записывается адрес зоны блока 7 памяти по синхросигналу с управляющего входа группы 9. По сигналу блока 8 управления из блока 7 памяти записывается слово в регистр 1 числа и счетчик 14 строк, которое с выхода 12 информации выводится из устройства. Затем в счетчик 14 строк записывается из блока 6 адрес строки и к нему добавляется единица, новый адрес строки фиксируется в блоке 6. Считывание зоны продолжается до переполнения счетчика 14 строк, после чего считывается следующая зона и т.д. (блоки 33, 58-68 алгоритма). Функционирование блока 6 ассоциативной памяти происходит следующим образом: в исходном состоянии все регистры блока обнулены, коммутатор 28 установлен в такое положение, что подключает к адресным входам дешифратора 28 регистр 2 адреса. Блок 6 работает в режимах записи, опроса и считывания. В режиме записи сначала выполняется запись в адресуемые ячейки блока 6 ассоциативной памяти. Сигналом «Запись блока 8 управления возбуждается выход дещифратора 28, соответствующий содержимому регистра 2 числа, и информация с регистра 1 числа записывается в указанную ячейку. После окончания записи массива информации в ячейки блока 6 ассоциативной памяти производится запись в регистры 23.1 и 23.2 масок, которая осуществляется с регистра 1 числа по сигналам блока 8 микропрограммного управления. Маски устанавливаются таким образом, что запись в дальнейщем осуществляется только в младщие Е разрядов слова. В режиме опроса блок 6 ассоциативной памяти работает следующим образом. В случае совпадения информации регистра 1 числа и счетчика 14 строк с содержимым одного из регистров 24 i на выходе подсоединенных к нему блоков 25 i сравнения, вырабатывается потенциал, соответствующий уровню логической «1. По сигналу опроса блока 8 микропрограммного управления производится запись «1 в разряд регистра 22 опроса, соответствующий ячейке, содержимое которой совпадает с информацией на входе блока 6. Так как одновременно в регистр 22 опроса могут быть записаны сразу несколько единиц, пороговым блоком 26 производится анализ многократного совпадения. Блок 26 вырабатывает сигнал многократного совпадения в случае, если в регистре 22 опроса записано две и более единицы (тогда он представляет собой набор стандартных логических элементов). Код, содержащийся в регистре 22 опроса, подается также на вход сумматора 27 по модулю 2, логическая «1 на выходе которого будет в том случае, если количество единиц в коде регистра 22 нечетно. Таким образом, если в регистре 22 опроса содержится одна единица, то на выходе многократного совпадения будет логический «О а на выходе однократного совпадения - «1. Если регистр 22 опроса не содержит ни одной единицы, на обоих выходах блока 6 ассоциативной памяти будет логический «О. Содержимое регистра 22 опроса подается на входы шифратора 31, на выходах которого формируется адрес сработавшей ячейки. Этот адрес поступает на выход блока 6 ассоциативной памяти и записывается в регистр 2 адреса в том случае, если на вход блока 8 поступил сигнал однократного совпадения, при этом на выходах мультиплексора 30 устанавливается код, равный содержимому выбранной, ячейки ассоциативной памяти. Во время считывания производится запись в счетчик 14 строк 1 младших разрядов слова по адресу, хранящемуся в регистре 2 адреса, содержимое которых там увеличивается и затем записывается на прежнее место. Ш 13.2 3 10 Таким образом, предлагаемое устройство вьшолняет функции известных устройств, однако в отличие от них оно автоматически формирует трассу выполнения программы с указанием последовательности событий и количества циклов. Сформированная трасса подготовлена для отображения. Если связать каждую поставленную на контроль команду с определенными координатами, трасса может быть непосредственно выведена на экран устройства наглядного отображения. Использование предлагаемого устройства позволит резко повысить эффективность и оперативность контроля выполнения и отладки программ в специализированных ЭВМ, содержащихся в системах управления, работающих в реальном масштабе вре.мени.

А /Ь А 4 -1

/ч

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для отладки программ | 1983 |

|

SU1290334A1 |

| Устройство для отладки программ | 1983 |

|

SU1322290A2 |

| Устройство для контроля программ | 1983 |

|

SU1136172A1 |

| Имитатор абонентов | 1983 |

|

SU1291987A1 |

| Система для обмена данными между информационными процессорами | 1980 |

|

SU1001070A1 |

| Микропрограммное устройство для анализа программ | 1980 |

|

SU943729A1 |

| Устройство для синтаксически-управляемого перевода | 1982 |

|

SU1062721A1 |

| Имитатор абонентов | 1986 |

|

SU1325490A2 |

| Устройство для контроля выполнения программ (его варианты) | 1985 |

|

SU1315981A1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1984 |

|

SU1254495A1 |

УСТРОЙСТВО ДЛЯ ФИКСАЦИИ ТРАССЫ ВЫПОЛНЕНИЯ ПРОГРАММЫ, содержащее регистр адреса, регистр предыдущего адреса, первый счетчик, блок сравнения, блок памяти, блок микропрограммного управления, коммутатор и элемент ИЛИ, причем выход регистра адреса соединен с входом регистра предыдущего адреса и первым информационным входом блока сравнения, выход регистра предыдущего адреса соединен с вторым входом блока сравнения, выходы равенства и неравенства которого соединены соответственно со счетным входом первого счетчика и адресным входом блока микропрограммного управления, первый, второй, третий, четвертый и пятый выходы блока микропрограммного управления соединены соответственно с входом записи регистра адреса, входом записи регистра предыдущего адреса, входом начальной установки первого счетчика, входом разрещения сравнения блока сравнения и входом записи блока памяти, информационный вход коммутатора соединен с информационным входом устройства, информационный выход первого счетчика соединен с первым информационным входом блока памяти, отличающееся тем, что, с целью повышения быстродействия при отладке программ, в него введены регистр числа, счетчик строк, второй счетчик, блок ассоциативной памяти, причем шестой, седьмой, восьмой, девятый, десятый и одиннадцатый выходы блока микропрограммного управления соединены сответственно со счетным входом счетчика строк, управляющим входом коммутатора, входом записи регистра числа, входом обращения к блоку ассоциативной памяти, с вы.ходом останова по переполнению устройства, и с выходом останова по неисправности устройства, вход задания режимов устройства соединен с первым входом ветвления блока микропрограммного управления, выход коммутатора соединен с информационным входом регистра числа, выход регистра числа i соединен с информационным входом блока ассоциативной памяти и информационным (Л выходом устройства, выход счетчиков строк соединен с входом элемента ИЛИ и со старшими информационными разрядами блока ассоциативной памяти, информационный выход которого соединен с адресным входом строк блока памяти и с первым информационным входом счетчика строк, выход кода количества выбранных ячеек и выход кода оо а адреса зон соединены соответственно с вторым входом ветвления блока микропрограммного управления и с первым информационным входом регистра адреса, вход адреса устройства соединен с вторым информационным . входом регистра адреса, выход которого соединен с входом адреса зоны блока памяти и с адресным входом блока ассоциативной памяти, выход неравенства блока сравнения соединен со счетным входом второго счетчика, выход которого соединен с вторым информационным входом блока памяти, информационный выход блока памяти соединен с вторым информационным входом счетчика строк и коммутатора, выход элемента ИЛИ соединен с входом признака переполнения блока микропрограммного управления.

Ш

е

Ш

/

3 (тб (7/775 ОтЮ

/v7

/

/7

f

/ч / w / / Фиг.1 Потени, сигнал,,вы6од ПотенкшАьный сигнал „ зш/гб устройство Синхросигнал прии/е/Л -- Запись адреса 1 (PrZ ячейки бл.6

С j

i

(КгП 0

(

СчЦ-1 - 0

СЧ

M : г-Ч1

Синхросигнал пришел -

Фul.

Пг- I

flpueM исходной конт-р {PrM.Ki рольной информации

Фиг, 5 9 Ибеличение содержк|(Cv,; мого Сч 1 циккод Формирование адре-- са зоны, слова Мрес быполненной команды совпадает с адресом команды, §ыпол ненной в предыдшаИ раз f/SeAi ijeHue содержамт Сч 4i nocAedoSamsAbноспшП Запись трассы

Гашение Сч Ц цимоЗ фиксаи, адреса выполненной коман ы,лод огтюбка следующего САода 6 дыбранной зоне .

55

(CV 4j): 0 (Pr3): /ljЛсл Лсл+1

57 Т Нет {tMA.pa3p., Acfl

Фиг-б (CvW 1 АЗОНЫ - J А ел (MA.pa3p.J) Л иет. )-()7 3n(C44-j, д бл7 поадрес1/{/ зоны,АсА) Синхросигнал я/7шё/ГП adpecff блока 6 (зоны ячеек блока 7) ВьМ содвтимого затредобанно ячейки |(РгУ; ша 6 ассоииатибHQU памяти (рг11 i

(pf)Ha 6df}i.l2

66

Фиг7 - на8ы)(М (ячРйка бл.7 cadoecoM(kM

1Z

Останов

( Коней, 3

Фиг.8

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для устранения мешающего действия зажигательной электрической системы двигателей внутреннего сгорания на радиоприем | 1922 |

|

SU52A1 |

| Бесколесный шариковый ход для железнодорожных вагонов | 1917 |

|

SU97A1 |

Авторы

Даты

1985-01-23—Публикация

1983-01-17—Подача