ского элемента ИЛИ, выход которого подключен к третьим входам m логических элементов ИЛИ, выходы которых соединены соответственно со входами разрядов преобразователя «код-напряжение, первый выход схемы сравнения подключен к первому входу преобразователя «код-напряжение, к первому входу логического элемента ИЛИ и через первый элемент задержки ко вторым входам логических элементов И схемы инверсного съема кода, второй выход схемы сравнения подключен ко второму входу преобразователя «код-напряжение, ко второму входу логического элемента ИЛИ и через второй элемент задержки ко вторым входам логических элементов И схемы прямого съема кода, выход логического элемента ИЛИ соединен со вторым входом триггера и с третьим входом преобразователя «код-напряжение.

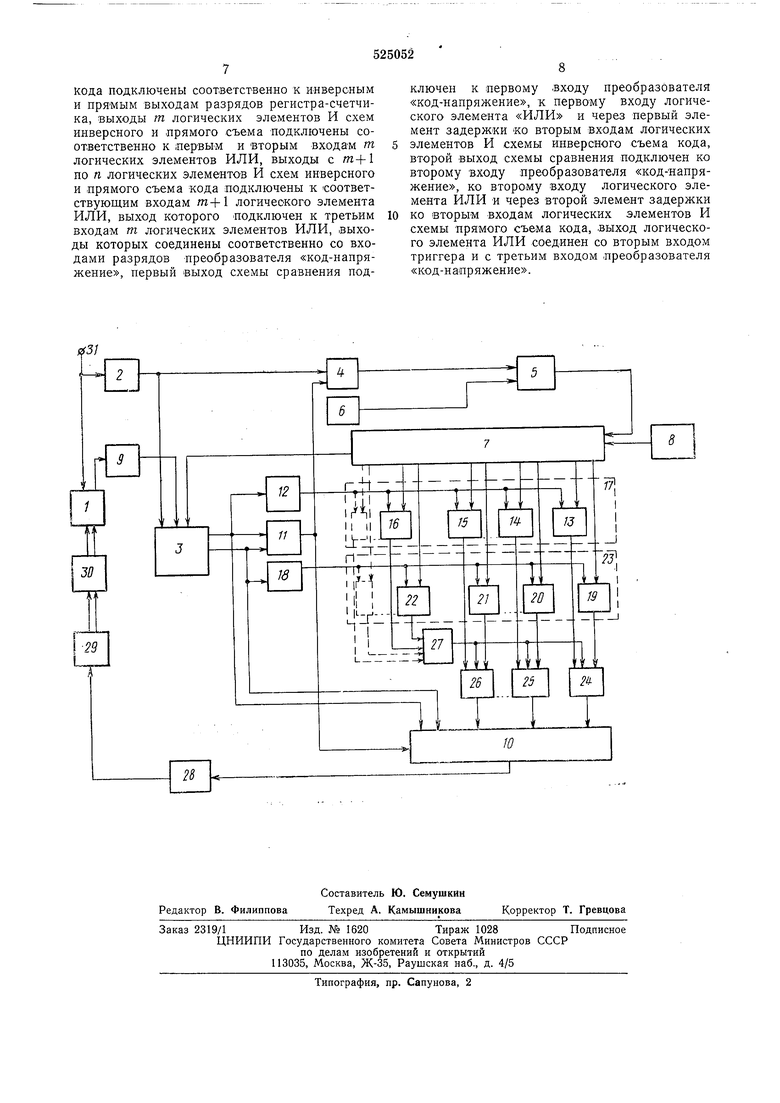

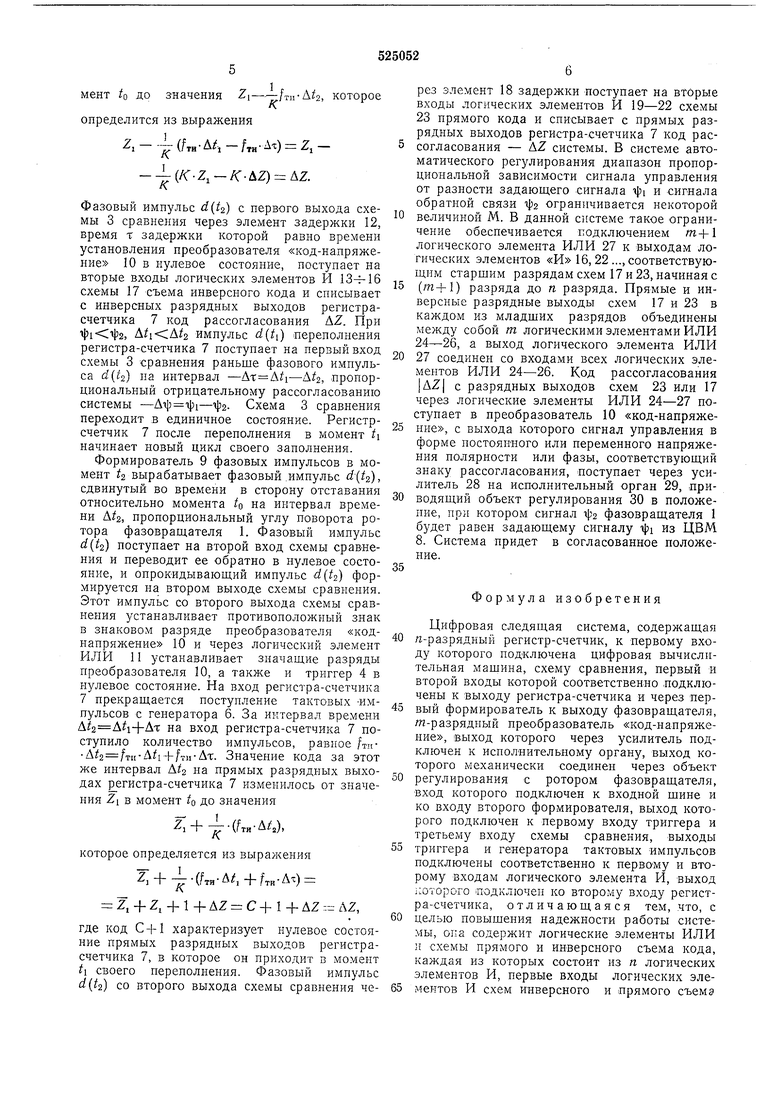

На чертеже представлена структурная схема цифровой следящей системы.

Она содержит фазовращатель 1, формирователь 2, схему 3 сравнения, триггер 4, логический элемент И 5, генератор 6 тактовых импульсов, регистр-счетчик 7, цифровую вычислительную мащину (ЦВМ) 8, формирователь 9, разрядный преобразователь 10 «код-напряжение, логический элемент 11, элемент задержки 12, логические элементы И, первый, второй, т и т+1 соответственно 13, 14, 15 и 16, схему 17 инверсного кода, элемент 18 задержки, логические элементы «И первый, второй, т и т+1 соответственно 19, 20, 21 и 22 схемы 23 прямого кода, логический элемент ИЛИ первый, второй, т, т+ соответственно 24, 25, 26 и 27, усилитель 28, исполнительный орган 29, объект регулирования 30, входную шину 31.

Система работает следующим образом.

На входы фазовращателя 1 и формирователя 2 поступает синусоидальное напряжение t/on по щине 31.

Формирователь 2 вырабатывает узкие импульсы начальной установки в моменты о перехода через нуль этого напряжения. Импульсы начальной установки с выхода формирователя 2 поступают на обнуляющие третий вход схемы 3 сравнения и первый вход триггера 4 и устанавливают их в исходное состояние. Выходной сигнал триггера 4 поступает на первый вход логического элемента И 5, который начинает пропускать тактовые импульсы генератора 6, следующие с частотой /тп, на счетный вход регистра-стетчика 7, в котором записан обратный код Zi задаваемого угла из ЦВМ 8. Регистр-счетчик 7 заполняется от значения кода Z в момент о до Значения кода С-:- в момент t, т. е. до его асреполнения, где С-полная емкость регистРа-счетчика 7. Время заполнения регистра-счетчика 7 пропорционально задаваемому коду Zi, так как в системе выполняется условие синхронизации: /ти-Топ-1 /С-С 2 -1, где п-разрядность кода; К,-коэффициент

пропорциональности, определяющий двоичнокодовую комбинацию разрядных выходов регистра-счетчика 7; Гоп-период опорного напряжения фазовращателя 1. На инверсных 5 разрядных выходах регистра-счетчика 7 за это же время код уменьщился от значения Zi -С-Z в момент io до нуля в момент

t-i-- . Момент переполнения ti регистра10 -

счетчика 7 является моментом перехода всех

его инверсных разрядных выходов из нулевого состояния в единичное. В момент t регистр-счетчик 7 вырабатывает импульс d()

,g своего переполнения, который поступает на первый вход схемы 3 сравнения, представляющей собой схему счетного триггера с двумя параллельно включенными счетными входами. Формирователь 9 фазовых импульсов в

Q момент 2 перехода выходного напряжения фазовращателя f/вых через нуль вырабатывает узкий импульс d(t2), сдвинутый во времени в сторону отставания относительно момента 0 на интервал , пропорциональный углу

2 поворота ротора фазовращателя 1. Этот фазовый импульс d(2) поступает на второй вход схемы 3 сравнения. ПриT|)i -a|52, и импульс d(t2) поступает на второй вход схемы 3 сравнения раньще импульса d(t) на

Q интервал времени Ат пропорциональный рассогласованию системы Ая|) 1- -1|з2. Схема 3 сравнения переходит в единичпое состояние, а опрокидывающий нечетный импульс d(t2) с первого выхода ее поступает

g на первый вход знакового разряда преобразователя 10 «код-напряжение и через логический элемент ИЛИ 11-на обнуляющие третий вход преобразователя 10 и второй вход триггера 4. Значащие разряды преобразоватеQ ля 10 устанавливаются в нулевые состояния, а выходной сигнал триггера 4 устанавливает логический элемент И 5 в состояние занрета, которое прекращает пропускать тактовые импульсы генератора 6 на вход регистра-счет5 чика 7. За интервал времени Af2 на вход регистра-счетчика 7 поступило количество импульсов

f Т„ А/2 - f ТИ Д 1 - /ТИ

0 Значение кода за этот же интервал на прямых разрядных выходах регистрач;четчика 7 увеличилось от значения кода Zj в момент to до значения

5Z,+ -.(/,„.А,)

/

в момент tz и при выполнении условия сиихропизацни определяется значением

(f,«.A,-f,«.AT)zr

А

:-. z; -f С - Z, - AZ С - AZ - AZ.

На инверсных же разрядных выходах значенке кода уменьшилось от значения Zi в момент до Значения i--/ти-А 2, которое

К

определится из выражения

2,--(/TH-A,-/TH-A) 2iл

--(/r-Z,-/r-AZ)AZ.

А

Фазовый импульс d(t-i) с первого выхода схемы 3 сравнения через элемент задержки 12, время т задержки которой равно времени установления преобразователя «код-напряжение 10 в нулевое состояние, поступает на вторые входы логических элементов И 13-f-16 схемы 17 съема инверсного кода и списывает с инверсных разрядных выходов регистрасчетчика 7 код рассогласования Д2. При , импульс d(t переполнения регистра-счетчика 7 поступает на первый вход схемы 3 сравнения раньше фазового импульса d(t2) на интервал -Дт А 1-Аг 2, пропорциональный отрицательному рассогласованию системы -All; 11)1-ч152. Схема 3 сравнения переходит в единичное состояние. Регистрсчетчик 7 после переполнения в момент t начинает новый цикл своего заполнения.

Формирователь 9 фазовых импульсов в момент tz вырабатывает фазовый .импульс d(t2), сдвинутый во времени в сторону отставания относительно момента IQ на интервал времени А/2, пропорциональный углу поворота ротора фазовращателя 1. Фазовый импульс d(t2} поступает на второй вход схемы сравнения и переводит ее обратно в нулевое состояние, и опрокидывающий импульс d(tz формируется на втором выходе схемы сравнения. Этот импульс со второго выхода схемы сравнения устанавливает противоположный знак в знаковом разряде преобразователя «коднапряжение 10 и через логический элемент ИЛИ 11 устанавливает значащие разряды преобразователя 10, а также и триггер 4 в нулевое состояние. На вход регистра-счетчика 7 прекращается поступление тактовых -импульсов с генератора 6. За интервал времени на вход регистра-счетчика 7 поступило количество импульсов, равное /тнА 2 /ти-А 1 + /тц-AT. Значение кода за этот же интервал А/г на прямых разрядных выходах э егистра-счетчика 7 изменилось от значения Zi в момент 0 до значения

(fTH-Ag,

л

которое определяется из выражения

(Гти-Л,+Г™-А.):

А

Z, + Z, + 1 + AZ с + 1 + AZ .--- AZ,

где код С + 1 характеризует нулевое состояние прямых разрядных выходов регистрасчетчика 7, в которое он приходит в момент ti своего переполнения. Фазовый импульс d(t2 со второго выхода схемы сравнения через элемент 18 задержки поступает на вторые входы логических элементов И 19-22 схемы 23 прямого кода и списывает с прямых разрядных выходов регистра-счетчика 7 код рассогласования - AZ системы. В системе автоматического регулирования диапазон пропорциональной зависимости сигнала управления от разности задающего сигнала ч) и сигнала обратной связи TJJ2 ограничивается некоторой

величиной М. В данной системе такое ограничение обеспечивается подключением логического элемента ИЛИ 27 к выходам логических элементов «И 16, 22 ..., соответствующим старшим разрядам схем 17 и 23, начиная с

(/п+1) разряда до п разряда. Прямые и инверсные разрядные выходы схем 17 и 23 в каждом из младших разрядов объединены между собой т логическими элементами ИЛИ 24-26, а выход логического элемента ИЛИ

27 соединен со входами всех логических элементов ИЛИ 24-26. Код рассогласования |AZ| с разрядных выходов схем 23 или 17 через логические элементы ИЛИ 24-27 поступает в преобразователь 10 «код-напряжение, с выхода которого сигнал управления в форме постоянного или переменного напряжения полярности или фазы, соответствующий знаку рассогласования, поступает через усилитель 28 на исполнительный орган 29, приводящий объект регулирования 30 в положение, при котором сигнал фазовращателя 1 будет равен задающему сигналу i из ЦВМ 8. Система придет в согласованное положение.

Формула изобретения

Цифровая следящая система, содержащая

«-разрядный регистр-счетчик, к первому входу которого подключена цифровая вычислительная машина, схему сравнения, первый и второй входы которой соответственно подключены к выходу регистра-счетчика и через первый формирователь к выходу фазовращателя, /п-разрядный преобразователь «код-нанряжение, выход которого через усилитель нодключен к исполнительному органу, выход которого механически соединен через объект

регулирования с ротором фазовращателя, вход которого подключен к входной шине и ко входу второго формирователя, выход которого подключен к первому входу триггера и третьему входу схемы сравнения, выходы

триггера и генератора тактовых импульсов подключены соответственно к первому и второму входам логического элемента И, выход iioToporo подключен ко второму входу регистра-счетчика, отличающаяся тем, что, с

целью повышения надежности работы системы, она содержит логические элементы ИЛИ и схемы прямого и инверсного съема кода, каждая из которых состоит из п логических элементов И, первые входы логических элементов И схем инверсного и прямого съемэ

кода подключены соответственно к инверсным и прямым выходам разрядов регистра-счетчика, выходы т логических элементов И схем инверсного и прямого съема подключены соответственно к первым и вторым входам т логических элементов ИЛИ, выходы с т+1 по п логических элементов И схем инверсного и прямого съема кода подключены к соответствующим входам т+1 логического элемента ИЛИ, выход которого подключен к третьим входам т логических элементов ИЛИ, выходы которых соединены соответственно со входами разрядов преобразователя «код-напряжение, первый выход схемы сравнения подключен к первому .входу преобразователя «код-напряжение, к первому входу логического элемента «ИЛИ и через первый элемент задержки ко вторым входам логических

элементов И схемы инверсного съема кода, второй выход схемы сравнения подключен ко второму входу преобразователя «код-напряжение, ко второму входу логического элемента ИЛИ и через второй элемент задержки

ко вторым входам логических элементов И схемы прямого съема кода, .выход логического элемента ИЛИ соединен со вторым входом триггера и с третьим входом .преобразователя «код-напряжение.

| название | год | авторы | номер документа |

|---|---|---|---|

| Дифференцирующее устройство | 1973 |

|

SU478334A1 |

| Преобразователь угла поворота вала в код | 1975 |

|

SU526934A1 |

| Преобразователь угла поворота вала в код | 1986 |

|

SU1387198A1 |

| Дифференцирующее устройство | 1974 |

|

SU516063A1 |

| Преобразователь угла поворота вала в код | 1975 |

|

SU634337A1 |

| Цифровой фазометр | 1982 |

|

SU1061062A1 |

| Преобразователь угол-код | 1984 |

|

SU1226669A1 |

| АДАПТИВНЫЙ ЦИФРОВОЙ ЧАСТОТНЫЙ ДИСКРИМИНАТОР | 2000 |

|

RU2166773C1 |

| Устройство для вычисления показателя экспоненциальной функции | 1983 |

|

SU1129611A1 |

| Многоканальный преобразователь угла поворота вала в код | 1975 |

|

SU537371A1 |

Авторы

Даты

1976-08-15—Публикация

1973-05-15—Подача