первых входов сумматора подключены к соответствующим разрядным выходам регистра сдвига, другие разряды первых входов - к (выходам блока памяти константы, вторые входы сумматора соедииены с выходами блока памяти, все информационные входы которого подключены к выходам сумматора, кроме старшего разряда, выходы двух старших разрядов сумматора - соответственно с двумя входами управления блока инвертирования кода, информационные входы которого, кроме выхода старшего разряда, связаны с црямыми и инверсными выходами блока памяти, а вход разрешения за.пиои блока -памяти- с инверсным выходом генератора тактовых импульсов.

Введение указанных блоков обеспечивает моделирование процесса случайного блуждания по детерминированной траектории между отражающими экранами, благодаря чему образуется последовательность равномерно распределенных чисел с полосовым спектром, основная частота которого зависит от «периода детерминированной траектории.

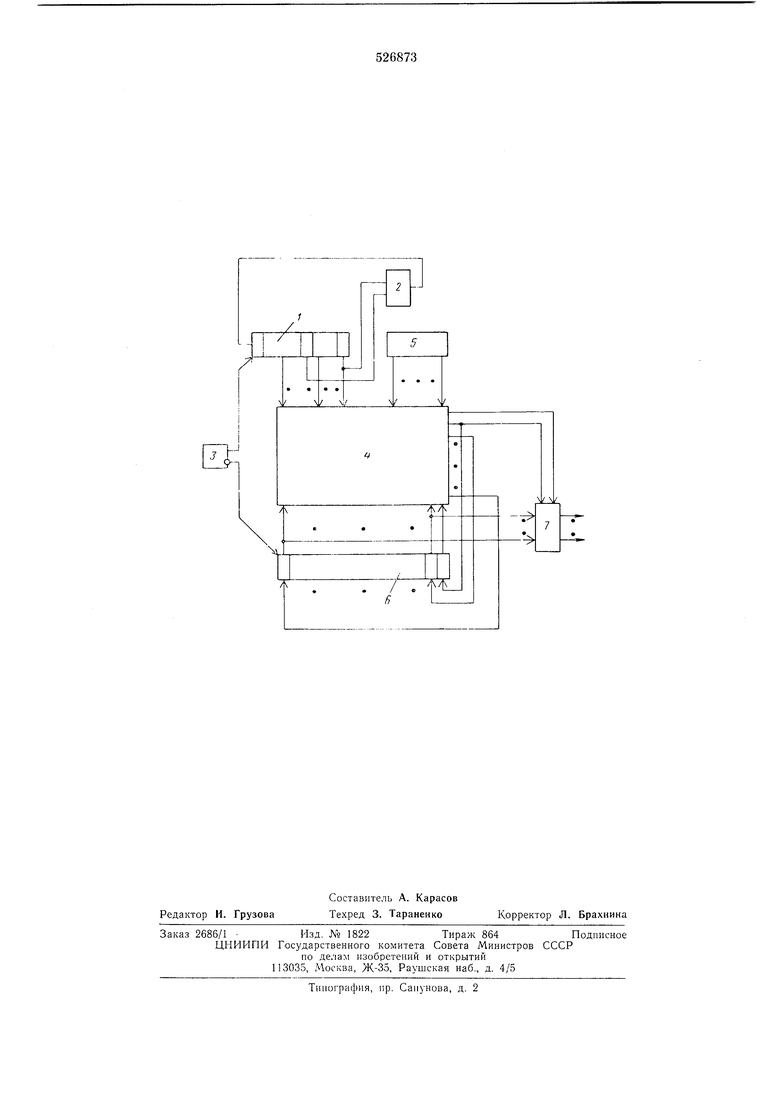

Блок-схема генератора приведена на чертеже.

Генератор псевдослучайных чисел содержит регистр 1 сдвига, выходы последнего и одного промежуточного разрядов которого соединены с входами сумматора 2 ло модулю 2, а выход сумматора-с информационным входом (Первого разряда регистра сдвига. К тактовому входу регистра сдвига подключен прямой выход генератора 3 тактовых импульсов, некоторые выходы регистра сдвига - к младшим разрядам первых входов сумматора 4 (количество и порядок подключения выходов регистра сдвига « сумматору 4 определяются конкретными условиями, накладываемыми па характеристики генерируемой последовательности чисел). Другие разряды первых входов сумматора 4 соединены с выходами блока 5 памяти константы, вторые входы сумматора 4 -с выходами блока 6 памяти, все информационные входы которого подключены к выходам сумматора 4, кроме выхода старшего (/п+1)-го разряда. Выходы двух старших (/n+l)-ro и т-го разрядов сумматора 4 соединены соответственно с двумя входами управления блока 7 инвертирования кода, информационные входы последнего подключены к лрямым и инверсным выходам, кроме выхода старшего т-го разряда, блока 6 памяти, вход разрешения записи .блока памяти- к инверсному выходу генератора 3 тактовых импульсов.

Работает генератор следующим образом.

Импульсы с прямого выхода генератора 3 тактовых импульсов, поступая на тактовый вход регистра 1, сдвигают содержимое каждого предыдущего двоичного разряда в последующии, при этом в первый разряд заносится значение, равное

где ai -двоичная цифра, записываемая в

первый разряд на /-м такте;

/ п

, а/ 1-содержимое i-ro и п-го разрядов регистра сдвига на (/-1)-м такте.

Таким образом, регистр сдвига выполняет функцию хранения и сдвига предшествующих п двоичпых цифр последовательности

,.., , а сумматор 2 в цепи обратной связи производит вычисление последующего значения первого разряда в соответст1вии с

приведенным выражением. На выходах регистра сдвига, подключенных к части первых входов сумматора 4, при выполнении известного требования (подключение входов сумматора 2 к выходам соответствующих разрядов) формируется последовательность равномерно распределенных псевдослучайных г-разрядных чисел с периодом повторения 2, причем . При последовательность

/--разрядных чисел близка по своих характеристикам последовательности независимых случайных чисел, распределенных равномерно. С выхода блока 5 на первые входы сумматора 4 подается двоичный код значения

параметра, определяющего постоянную часть текущего значения операнда на первых входах сумматора 4. Изменением величины параметра можно изменить вид спектральной характеристики формируемой последователькости чисел, т. е. осуществлять управление спектром.

Вторым слагаемым на каждом такте образования выходного числа, подаваемым на сумматор 4, являются значения промежуточных сумм на предыдущих тактах. С этой целью выходной код сумматора 4 после окончания каждого сложения при появлении разрешающего импульса на инверсном выходе генератора 3 тактовых импульсов (это соответствует паузе между тактовыми импульсами на входе регистра 1 сдвига) заносится в блок 6 памяти. Прямые выходы всех разрядов блока памяти соединены с вторыми входами сумматора 4, благодаря чему на выходах сумматора 4 образуется так называемый процесс восстанавленИЯ текущих значений операнда, поступающего на первые входы сумматора 4. Сумматор 4 содержит на два разряда больше, чем разрядность генерируемых чисел, и на один разряд больше блока б памяти для образования процесса блуждания

по детермиинрозаннои траектории со случайным шагом между отражающими экранами. Индикатором достижения случайным процессом одной из отражающих границ служит появление значащей единицы в т-и или (т+1)-м разряде сумматора 4. Продолжение суммирования после появления значащей единицы в /п-.м разряде и инвертирование кода (т-1)-разрядной промежуточной суммы идентично операции суммирования до момента достижения случайной -величиной промежуточных сумм значения и операции вычитания исходной случайной величины, определяющей щаг блуждания и подаваемой на первые входы сумматора 4, из предыдущих значений промежуточных сумм до момента достижения значения 0. Таким образом осуП1ествляется моделирование .процесса случайного блуждания по детерминированной траектории между отражающими границами О и 2 --1. Как показали проведенные аналитическое исследование и моделирование на ЭВМ, такой процесс обеспечивает получение равномерно распределенных псевдослучайных последовательностей чисел с заданным полосовым спектром.

Использование предлагаемого генератора псевдослучайных чисел с заданным полосовым спектром в устройствах определения характеристик детерминированных и случайных сигналов позволяет получить ощибку квантования исследуемого сигнала, спектр которой не перекрывается со спектром самого сигнала. Дальнейщая цифровая фильтрация результатов квантования дает возможность эффективно уменьщить ощибку квантования, а тем самым повысить точность определения характеристик сигналов.

Формула изобретения

Генератор псевдослучайных чисел, содержащий регистр сдвига с сумматором по модулю 2 в цепи обратной связи, генератор тактовых импульсов, прямой выход которого подключен К тактовому входу регистра сдвига, отличающийся тем, что, с целью расщирения области применения, в него введены

сумматор, блок памяти, блок памяти константы и блок инвертирования кода, причем младщие разряды первых входов сумматора соединены с соответствующими разрядными выходами регистра сдвига, другие разряды первых входов подключены к выходам блока памяти константы, вторые входы сумматора соединены с выходами блока памяти, все информационные входы которого подключены -к выходам сумматора, кроме старщего разряда,

выходы двух старщих разрядов сумматора соединены соответственно с двумя входами управления блока инвертирования кода, информационные входы которого, кроме выхода старщего разряда, подключены к прямым и

инверсным выходам блока памяти, вход разрешения записи которого соединен с инверсным выходом генератора тактовых импульсов.

Источники информации, принятые во внимание при экспертизе:

I. Патент США № 3700869, кл. 235-152, 1972.

2. Яковлев В. В., Федоров Р. Ф. Стохастические вычислительные мащины. - «Машиностроение, Л., 1974, с. 253. 3. Авт. ов. № 391556, кл. G 06F 1/02, 1973.

| название | год | авторы | номер документа |

|---|---|---|---|

| Конвейерное устройство для вычисления тригонометрических функций | 1984 |

|

SU1168931A1 |

| Преобразователь код-вероятность | 1973 |

|

SU450153A1 |

| Генератор псевдослучайных испытательных последовательностей | 1986 |

|

SU1354401A2 |

| Устройство генерации равномерно распределенных псевдослучайных чисел | 2024 |

|

RU2840424C1 |

| Устройство для сглаживания сигналов | 1987 |

|

SU1437877A1 |

| Устройство для контроля логических блоков | 1985 |

|

SU1269141A1 |

| Генератор случайных чисел | 1990 |

|

SU1817094A1 |

| Генератор псевдослучайных сигналов | 1977 |

|

SU744684A1 |

| Генератор случайного процесса | 1986 |

|

SU1429113A1 |

| Устройство для контроля оперативной памяти | 1982 |

|

SU1091227A1 |

Авторы

Даты

1976-08-30—Публикация

1975-06-23—Подача