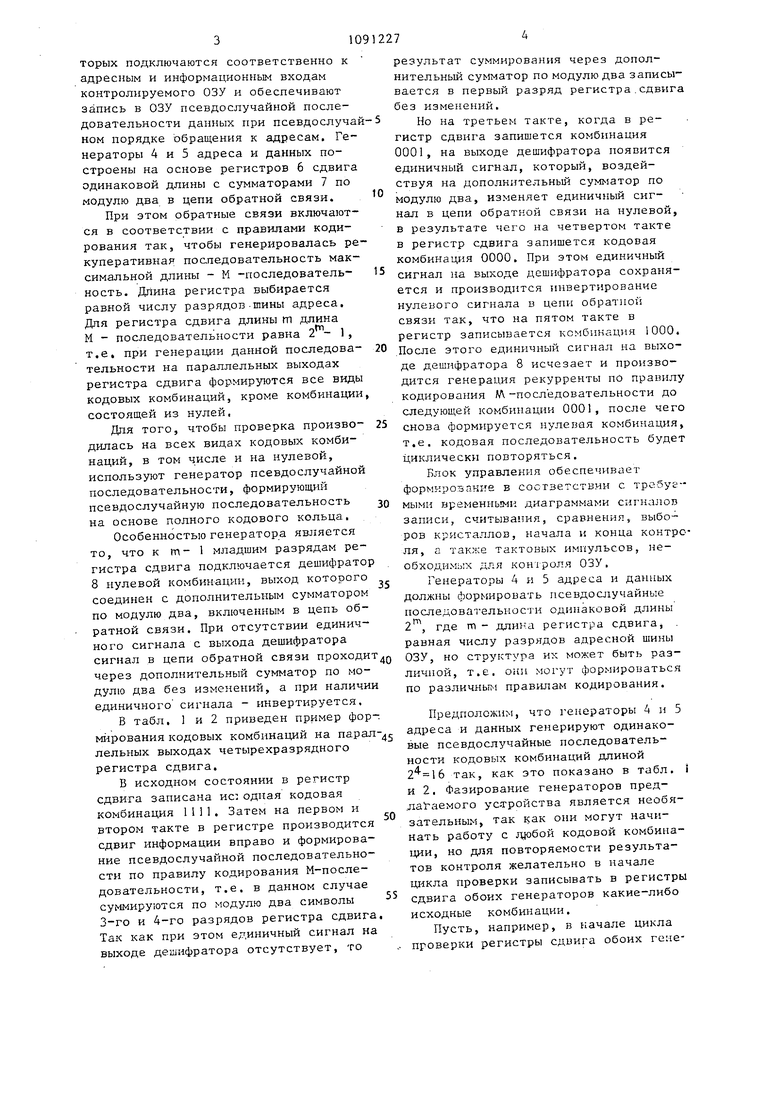

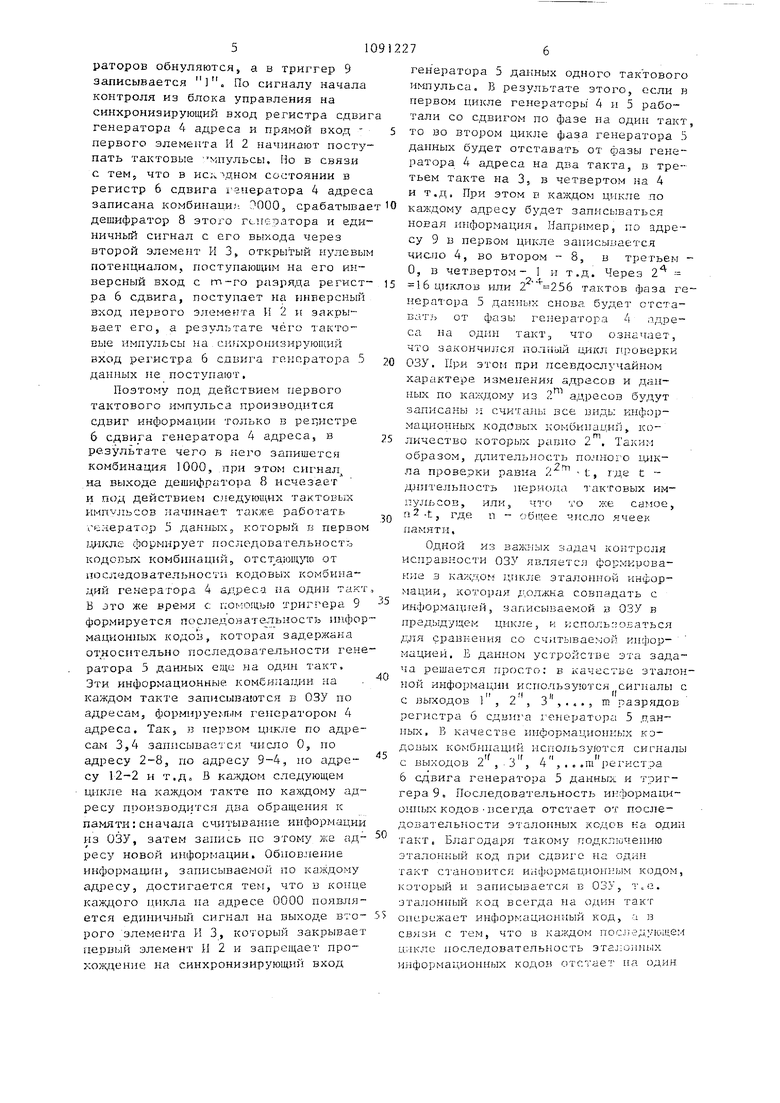

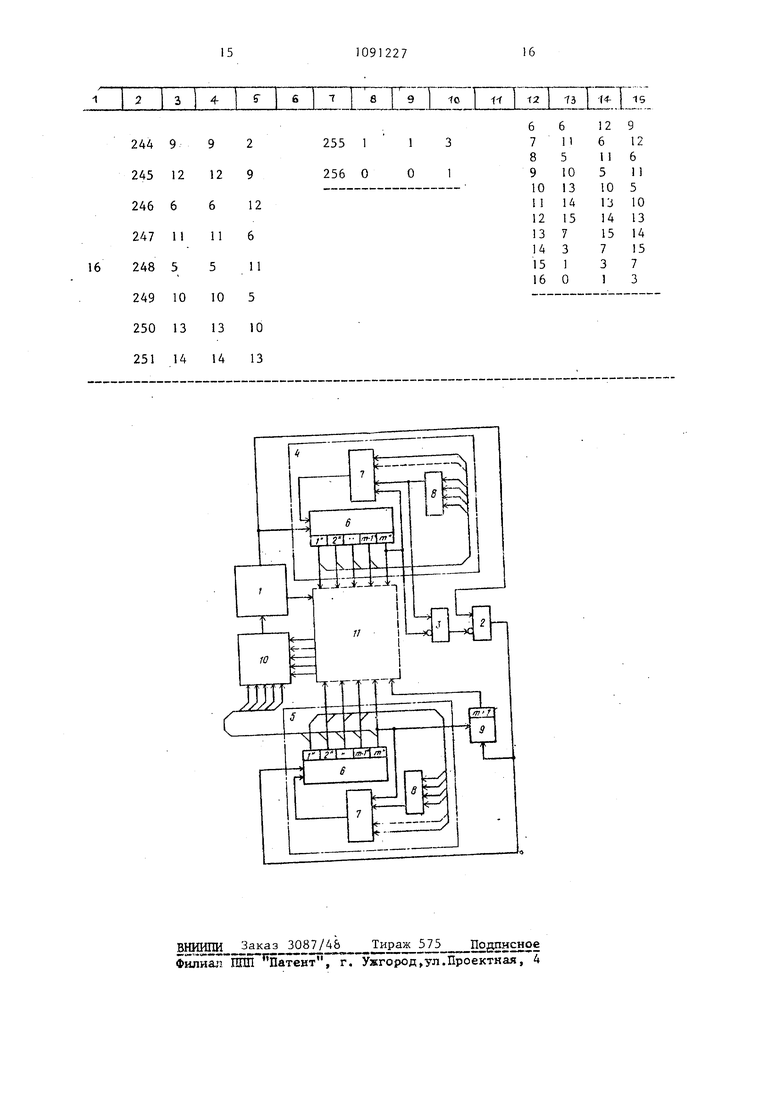

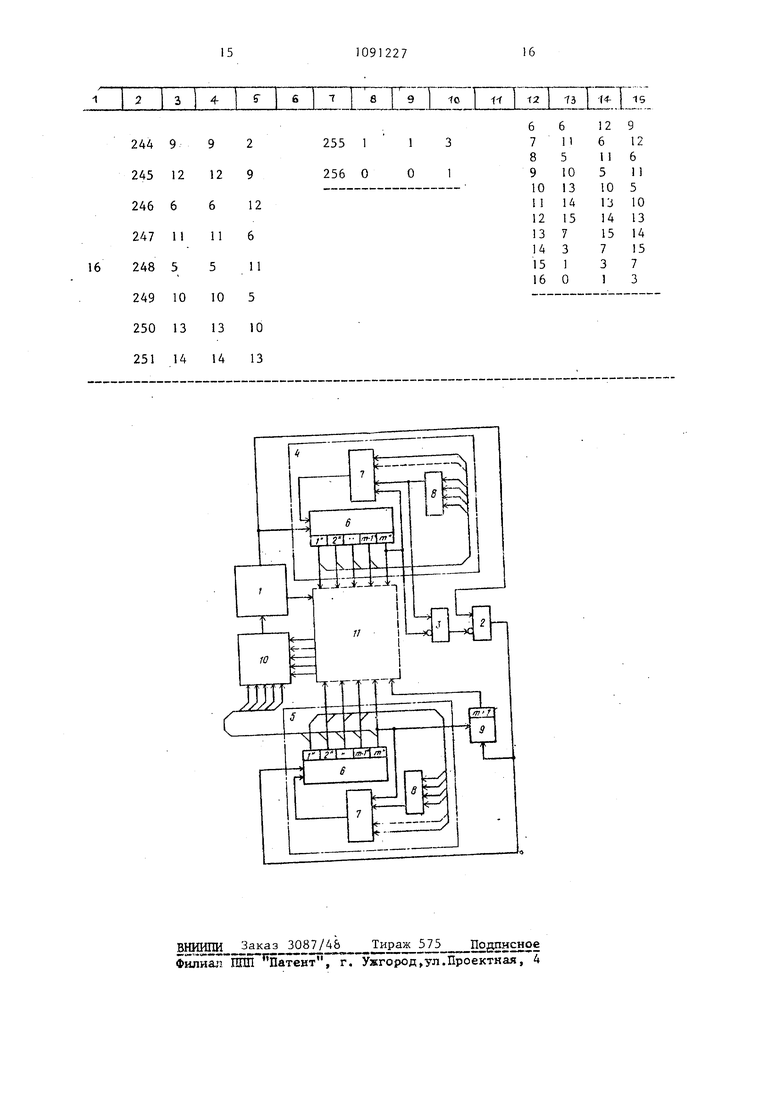

Изобретение относится к запоминаю 1ЦИМ устройствам и может быть исполь зовано для функционального контроля оперативной памяти. Известно устройство для контроля оперативной памяти t i J, Недостатками известного устройств являются последо& тельнь;й порядок обращения к адреса.: сложность формирования эталонной лнформации и воз можность генерирования только одной псевдослучайной последовательности. Наиболее техническим реше нием к изобретению является устройство для контроля блоков памяти, содержащее генераторы адреса и данньж подключенные к входам контролируемого блока памяти, схему сравршния и блок управления, соединенный с выходом схемы сравнения и входами генератора адреса и блока памяти 2 Недостатком этого устройства является невысокая достоверность контроля. Цель изобретения - повышение дост верности контроля путем обеспечения возможности кольцевого тестирования. Поставленная цель достигается тем что в устройство для контроля оперативной памяти, содержащее генератор адреса, одни выходы которого являются одними вьгходами устройства, а вхо подключен к первому выходу блока упрг1вления, другой выход которого является выходом устройства, а вход соединен с выходом блока сравнения, одни выходы которого являются входам устройства, и генератор данных, введены первый и второй элементы И, три гер, информационный вход которого . подключен к выходу старшего разряда генератора данных, первый вход перво го элемента И соединен с нулевым выходом триггера, а второй вход - с одним выходом генератора адреса, nep вый вход второго элемента Ц подключе к первому выходу блока управления, второй вход - к выходу первого элемента И, а выход - к синхровходу триггера и к входу генератора данных одни выходы которого соединень с другими входами блока сра внения-, а другие выходы и выход триггера являются другими выходами устройства. На.,чертеже приведена функциональ пая схема предлагаемого устройства. Устройство содержит блок управ ления, эле ченты И 2 и 3, генератор 4 и 5 соответственно адреса и данных, в состав каждого из которых входят / -разрядный регистр 6 сдвига, сумматор 7 по модулю два и дешифратор 8, триггер 9 и блок 0 сравнения. Генераторы 4 и 5 выполнены одинаково В каждом из них выход дешифратора 8 соединен с первым входом сумматора 7 по модулю два, выход которого соединен с информадионым входом регистра 6 сдвига, который подключается: к дешифратору 8 - выходами разрядов 1, 2, 3 ,......,№-, х второму входу сумматора 7 по модулю два выходом разряда tri и к третьему входу -ши группе входов сумматора 7 по модулю два - выходами разрядов, определяемыми правилом кодирования. Первый выход блока i управления подключен к синхронизиру10111,ему входу рехистра 6 сдвига генератора 4 адреса непосредственно, а к синхронизирующим входам регистра 6 сдвига и триггера. 9 - через первый элемент И 2, инверсный вход которого соедине;н с выходом второго элемента И 3, прямой и инверсный входы которого соединены соответственно с выходом дешифратора 8 и Ш-.М разрядом регистра 6 сдвига генератора 4 адреса, Быхсд т-го разряда регистра 6 сдвига генератора 5 да;;пых соединен с информационным вxoдo. триггера 9, выход которого, а также в.иходы 2, 3, 4, , .,« „ ,, ,. , разрядов регистра 6 сдвига генератора 5 данных Я2;ляют ся информационными выхо,пами устрой- ства, а выходы разрядоз 1, 2 , 3 , ..,,., т регистра 6 сд1знг.а генератора 4 адреса являются адресными выходами устройства и соединяются с.оот- ветственно с информационньми и адресньшИ входами контролируемого ОЗУ 11. информационные выходы которого являются информационными входами устройства и соединяются с первыми входами блока 10 сравнения, вторые входы которого подключаются к выходак разрядов ) , 2, З ,,,, о. .1 регистра 6 сдвига генератора 5 данныл.. Выход блока сравнения соединяется с входом блока управления, вторые выходы которого ЯВ.ЛЯЮТСЯ управляюими выходами устройства и также, подключаются к контролируе.ому ЭЗУ 1 1 , Основой устройства для контроля оперативной памяти являются генераторы 4 и 5, параллельные выходы которых подключаются соответственно к адресным и информационным входам контролируемого ОЗУ и обеспечивают запись в ОЗУ псевдослучайной последовательности данных при псевдослуча ном порядке обращения к адресам. Генераторы 4 и 5 адреса и данных построены на основе регистров 6 сдвига одинаковой длины с сумматорами 7 по модулю два в цепи обратной связи. При этом обратные связи включаются в соответствии с правилами кодирования так, чтобы генерировалась ре куперативная поапедовательность максимальной длины - М -последовательность. Длина регистра выбирается равной числу разрядов-ШИНЫ адреса. Для регистра сдвига длины m длина М - последовательности равна 2 - 1, т.е. при генерации данной последовательности на параллельных выходах регистра сдвига формируются все виды кодовых комбинаций, кроме комбинации состоящей из нулей, Для того, чтобы проверка производилась на всех видах кодовых комбинаций, в том числе и на нулевой, используют генератор псевдослучайной последовательности, формирующий псевдослучайную последовательность на основе полного кодового кольца, Особенностью генератора является то, что к т- 1 младшим разрядам регистра сдвига подключается дешифрато 8 нулевой комбинации, выход которого соединен с дополнительным сумматором по модулю два, включенным в цепь обратной связи. При отсутствии единичного сигнала с выхода дешифратора сигнал в цепи обратной связи проходи через дополнительный сумматор по модулю два без изменений, а при наличи единичного сигнала - инвертируется, Б табл. 1 и 2 приведен пример фор М14рования кодовых комбинаций на пара лельных выходах четырехразрядного регистра сдвига. В исходном состоянии в регистр сдвига записана не: одная кодовая комбинация 1111. Затем на первом и втором такте в регистре производится сдвиг информации вправо и формирование псевдослучайной последовательности по правилу кодирования М-последовательности, т.е, в данном случае суммируются по модулю два символы 3-го и 4-го разрядов регистра сдвига Так как при этом единичный сигнал на выходе дешифратора отсутствует, то результат суммирования через дополнительный сумматор по модулю два записывается в первый разряд регистра . сдвига без изменений. Но на третьем такте, когда в регистр сдвига запишется комбинация 0001, на выходе дешифратора появится единичный сигнал, который, воздействуя на дополнительный по модулю два, изменяет единичный сигнал в цепи обратной связи на нулевой, в результате чего на четвертом такте в регистр сдвига запишется кодовая комбинация 0000. При этом единичный сигнал на выходе дешифратора сохраняется и производится инвертирование нулевого сигнала в цепи обратной связи так, что на пятом такте в регистр записывается комбинация 1000. .После этого единичный сигнал на выходе дешифратора 8 исчезает и производится генерация рекурренты по правилу кодирования АЛ -последовательности до следующей комбинации 0001, после чего снова формируется нулевая комбинация, т.е, кодовая последовательность будет циклически повторяться. Блок управления обеспечивает формирозание в состзетствии с требуемыми временньми диаграммами сигналов записи, считывания, сравнения, выборов кристаллов, начала и конца контреля, а также тактовых импульсов, необходимых для конгроля ОЗУ, Генераторы А j-i 5 адреса и данных должны формировать псевдослучайные последовательности оди1 аковой длины 2 , где m - длина регистра сдвига, . равная числу разрядов адресной шины ОЗУ, но структура их может быть различной, т,е, они могут формироваться по различным правилам кодирования. Предположим, что генераторы 4 и 5 адреса и данных генерируют одинаковые псевдослучайные последовательности кодовых комбинаций длиной так, как это показано в табл. i и 2. Фазирование генераторов пред.лагаемого ус-тройства является необязательным, так как они могут начинать работу с /уобой кодовой комбинации, но для повторяемости результатов контроля желательно в начале цикла проверки записывать в регистры сдвига обоих генераторов какие-либо исходные комбинации. Пусть, например, в начале цикла проверки регистры сдвига обоих гене5ратороБ обнуляются, а в триггер 9 записывается 1. По сигналу начала контроля из блока управления на синхронизирующий вход регистра сдви генератора 4 адреса и прямой вход первого элемента И 2 начинают посту пать тактовые мпульсы. Но в связи с тем, что в исходном состоянии в регистр 6 сдвига генератора 4 адрес записана комбинации; ЭООО, срабатыва дешифратор 8 этого генератора н еди ничный сигнал с его выхода через второй элемент И 3, открытый нулевы потенциалом, ностунающим на его инверсный вход с го-го разряда регист ра 6 сдвига, поступает на инверсный вход первого элеме-ита И 2 и закрывает его, а результате чего тактовые импульсы на синхронизируюисий вход регистра 6 сдвига гампратора 5 данных не поступают. Поэтому под действием первого тактового импульса производится сдвиг информации только в peiiHcrpe 6 сдвига генератора 4 адреса, в результате чего в него запишется комбинация 1000, при этом сигнал на выходе дешифратора 8 исчезает и под действием следующих тактовых HMnvjibcoB начинает работать 1енератор 5 данных, который в первом Злнкле формирует последовательность кодовых комбинаций, отстдющую от последовательности кодовых комбинаций генератора 4 адреса на один такт В это же время с помощью триггера 9 формируется последовательность инфор мационных кодов, которая задержана относительно последовательности гене ратора 5 данных еще на один такт. Эти информационные комбипацин на каждом такте записываются в ОЗУ по адресам, фopмиpye л,м reiiepaiopOM 4 адреса. Так, в цикле по адресам 3,4 записывается число О, по адресу 2-8, по адресу 9-4, по адресу 12-2 и т.д. В ка;кдом следующем цикле на каждом такте но каждому адресу производится два обращения к памяти:сначала считывание информации из ОЗУ, затем запись пс этому же ад ресу новой информации. Обновление информац1 и, записываемой по каждому адресу, достигается тем, что в конце каждого цикла на адресе 0000 появляется единичный сигнал на выходе второго элемента И 3, который закрывает первый элемент И 2 н запрещает прохождение на синхронизирующий вход 27 генератора 5 данных одного тактового датульса, В результате этого, если н первом цикле генераторы 4 н 5 работали со сдвигом по фазе на один такт, то во втором цикле фаза генератора 5 данных будет отставать от фазы генератора 4 адреса на два такта, в третьем такте на 3, в четвертом на 4 и т.д. При этом в каждом цикле по каждому адресу будет записыватьс новая информация, Например, по адресу 9 в первом цикле записывается число 4, во втором - 8, в третьем О, в четвертом- I и т.д. Через 2 16 циклов или 2 тактов фаза генератора 5 данных снова будет отстаот фазы генератора 4 на один такт., что озна что закончился цикл гцюверки ОЗУ, При этом при псевдослучайном характере изменения адресов и данных по каждому из адресов будут записаны ;i считаны все видь: информационных кодйвых комбинаций, количество KOTOpbix piiBHo 2 . Таким образом, длительность поллюго Щ1Кла проверки равна - t, где t длительность периода тактовых импульсов, или, ЧТС1 VO же самое, n2.t, где п - общее число ячеек памяти. Одной из важных задач контроля исправности ОЗУ является формкровакие 3 каждом цикле эталонной информации, которая должна совпадать с информац51ей, записываемой в ОЗУ в предыдущем цикле, к ксполь::оБаться для сравкен11я со считываемой информацией, В данном устройстве эта задача решается просто; в качестве эталонной информации используются сигналы с с выходов l, 2, З,,.., m разрядов регистра 6 сдвига 1енератора 5 данных, В качестве информацио1п-ь х кодовых комбинаций используются сигналы of , If ; I I С выходов 2 , . 3 , 4 , , . «ni регистра 6 сдвига генератора 5 данных и триггера 9, Последовательность информационных кодов всегда отстает от последовательности эталонных кодов на один такт. Благодаря такому подключению эталонный код при сдвиге ни одиь: такт становится информационным кодом, который и записывается в ОЗУ, т.е. эталонный код всегда на один такт опережает информационный код, а 3 связи с тем, что в каждом nocji5A:7ioiiieM ш-нчлс последовательность этало п-п.1х информационных кодов отстает па один

такт от аналогичных последовательностей в предыдущем цикле, то опережение в одном случае и отставание в другом взаимно компенсируются и эталонные коды по каждому адресу будут совпадать с тем1 шформационными кодами которые были записаны по тем же адресам в предыдущем цикле.

Так, если в первом цикле по адресу б записывалось число 9, то во втором цикле по адресу б эталонный код тоже равен числу 9, если в -г первом цикле по адресу 13 записывалось число 5, то во втором цикле эталонный код по адресу 13 также равен числу 5, если во втором цикле по адресу 3 записывалось 14, то в третьем цикле но адресу 3 эталонный код также равен 14 и т.д. Сравнение считываемого из ОЗУ иьформационного кода с эталонным кодом производится в блоке 10 сравнения, выход которого соединен с входом блока 1 .управления. Блок управления выносит решение об испрааиости ОЗУ только в том случае, если за время

полного цикла проверки считываемый из ОЗУ информационный код на такте совпадает с соответствующим э т ал ониым к одом.

В общем случае, когда число разрядов шины адреса не равно числу разрядов шины данных, число разрядов регистров сдвигов обоих генераторов выбирается равным большему из этих чисел, а шина, число разрядов у которой меньше, подключается к старшим разрядам рег-истра сдвига, а млад;: ие разряды этого ре- . гистра не используются.

Технико-экономическая эффективность заключается в том, ччо предлагаемое устройство позволяет записывать .однородиую по структуре инфор ;,-Г1,о И накопитель и поэтому является эффективным тестом для контроля накоп1- телей. Одаовременно псевдсслучаГный порлцок обращения к адресам ОЗУ делает его эффективным для контроля адресных дешифраторов ОЗУ.

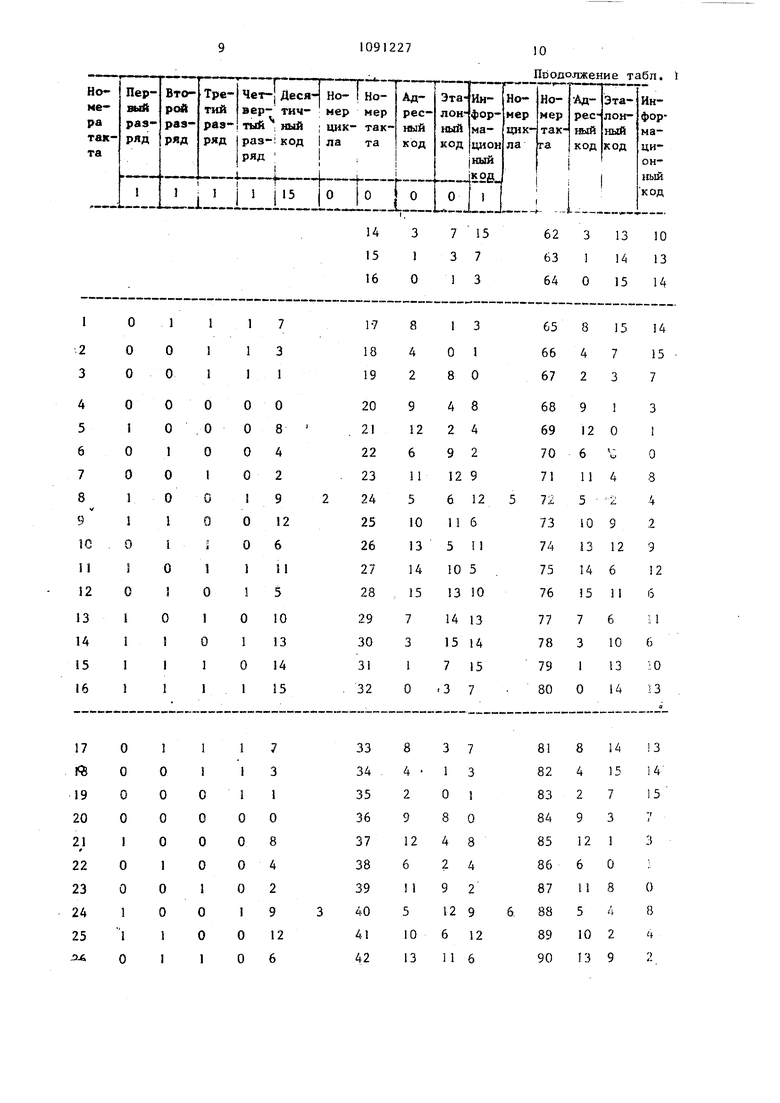

Т а б л и

Ц а

Поодолжение табл. 1

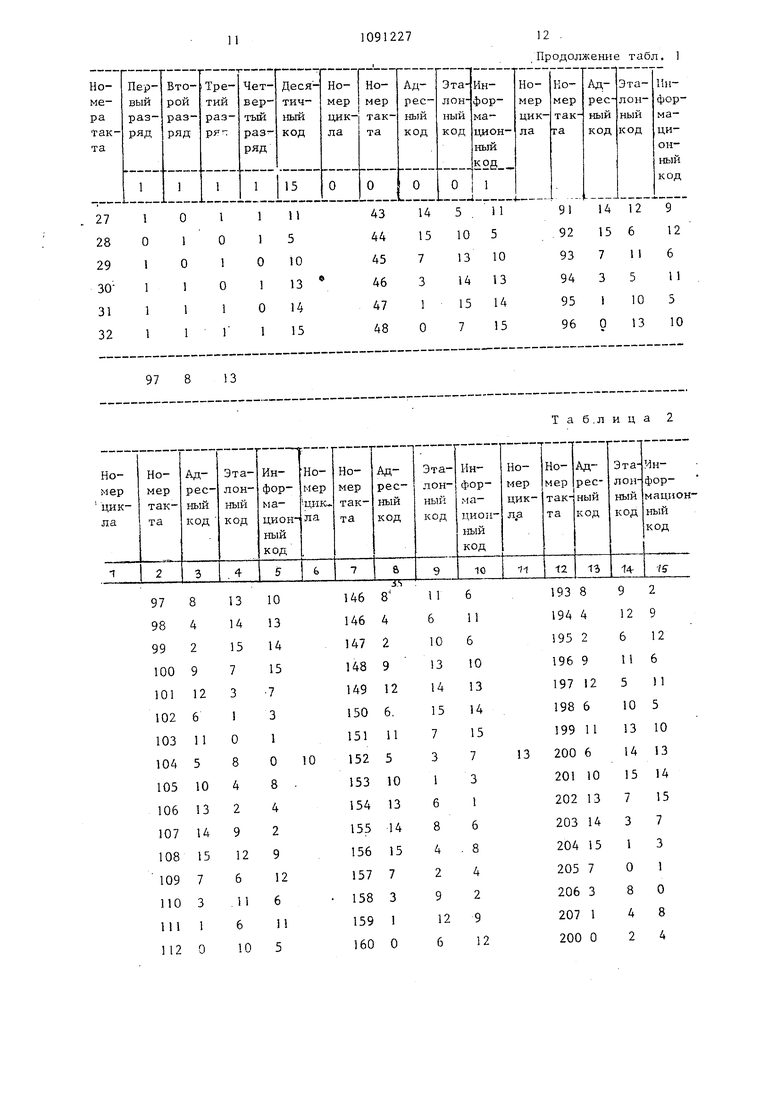

11

1091227

12 /Продолжение табл. 1

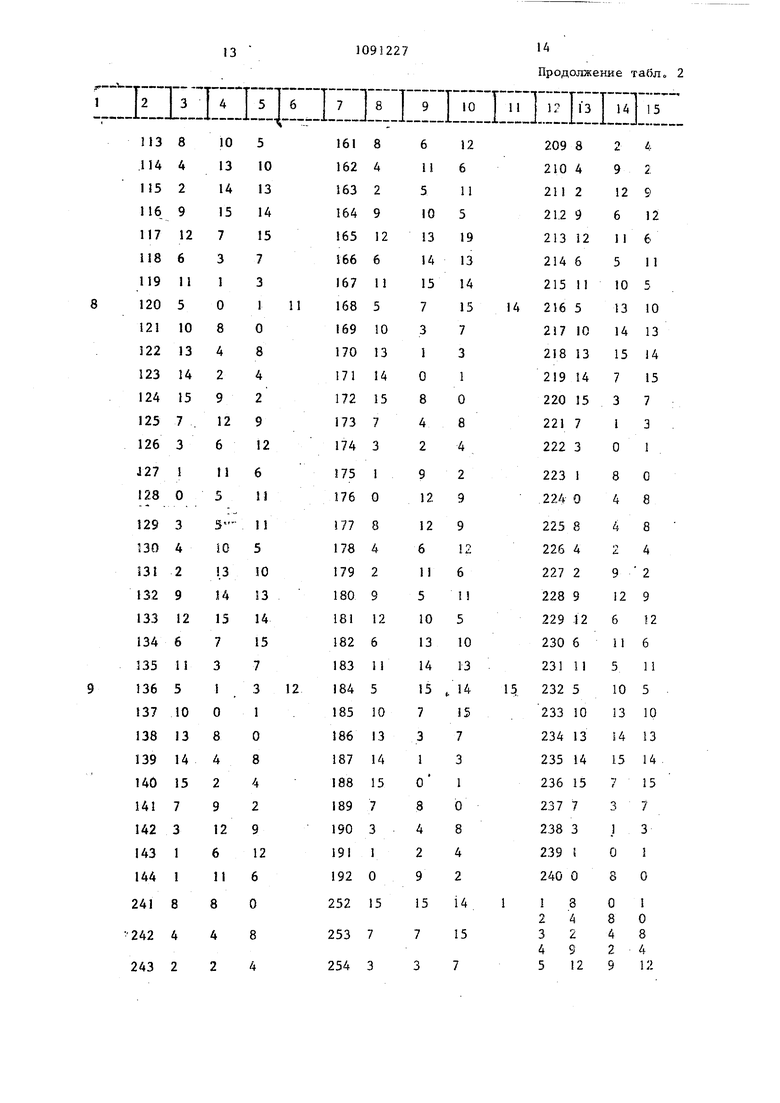

J3 1091227

Продолжение та{)л, 2

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля оперативных накопителей | 1989 |

|

SU1705874A1 |

| Устройство для задания тестов | 1983 |

|

SU1141379A2 |

| Устройство для задания тестов | 1983 |

|

SU1168951A1 |

| УСТРОЙСТВО ДЛЯ СИНТЕЗА РЕЧЕВЫХ СИГНАЛОВ | 1991 |

|

RU2020608C1 |

| Логический анализатор | 1986 |

|

SU1432527A1 |

| Генератор псевдослучайных последовательностей | 1988 |

|

SU1626345A2 |

| Устройство для контроля цифровых узлов | 1984 |

|

SU1231506A1 |

| Имитатор абонентов | 1983 |

|

SU1291987A1 |

| Устройство для контроля блоков оперативной памяти | 1984 |

|

SU1265859A1 |

| Устройство для формирования тестов | 1990 |

|

SU1795462A1 |

УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ОПЕРАТИВНОЙ ПАМЯТИ, содержащее генератор адреса, одни выходы которого являются одними выходами устройства, а вход подключен к первому выходу блока управления, другой выход которого является выходом устройства, а вход соединен с выходом блока сравнения, одни входы которого являются входами устройства, и генератор данных, отличающееся тем, что, с целью повышения достоверности контроля путем обеспечения возможности кольцевого тестирования, в него введены первый и второй элементы И, триггер, информационный вход которого подключен к выходу старшего разряда генератора данных, первый вход первого элемента И соединен с нулевым выходом триггера, а второй вход - с одним выходом генератора адреса, первый вход второго элемента И подключен к первому выходу блока управления, второй вход - к выходу первого элемента И, а выход - к синхровходу тригге ра и к входу генератора данных, одни выходы которого соединены с другими (/) входами блока сравнения, а другие выходы и-выход триггера являются другими выходами устройстБа. f

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для контроля оперативной памяти | 1975 |

|

SU547837A1 |

| Солесос | 1922 |

|

SU29A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Авторское свидетельство СССР № 760195, кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1984-05-07—Публикация

1982-11-17—Подача