(jciaiOK 3fO(O усгройсгва состоит в юм.что оно не по;гйоляе1 конгролировагь функццо5шроваluie логических блоков, что сужает область его применения.

Целью изобретения является расши1 екие области примеиеш-1я усфойства.

Поставленная цепь достигается Бвеаегшем в npejxnoKeHHoe устройство блсжа с атйст гческих анализаторов. При этом выходы нреобразователл случайных чисел соеданены с входами контролируемого логаческого блока, а вход блока индикации - с выходом б.гтока управления через блок статистических йкализа-торэв, йнформни.иогшые входы соторого оов;п ненш с зйтходаин коммугатора вь ХОДЯЫХ CHiHBJIOB.

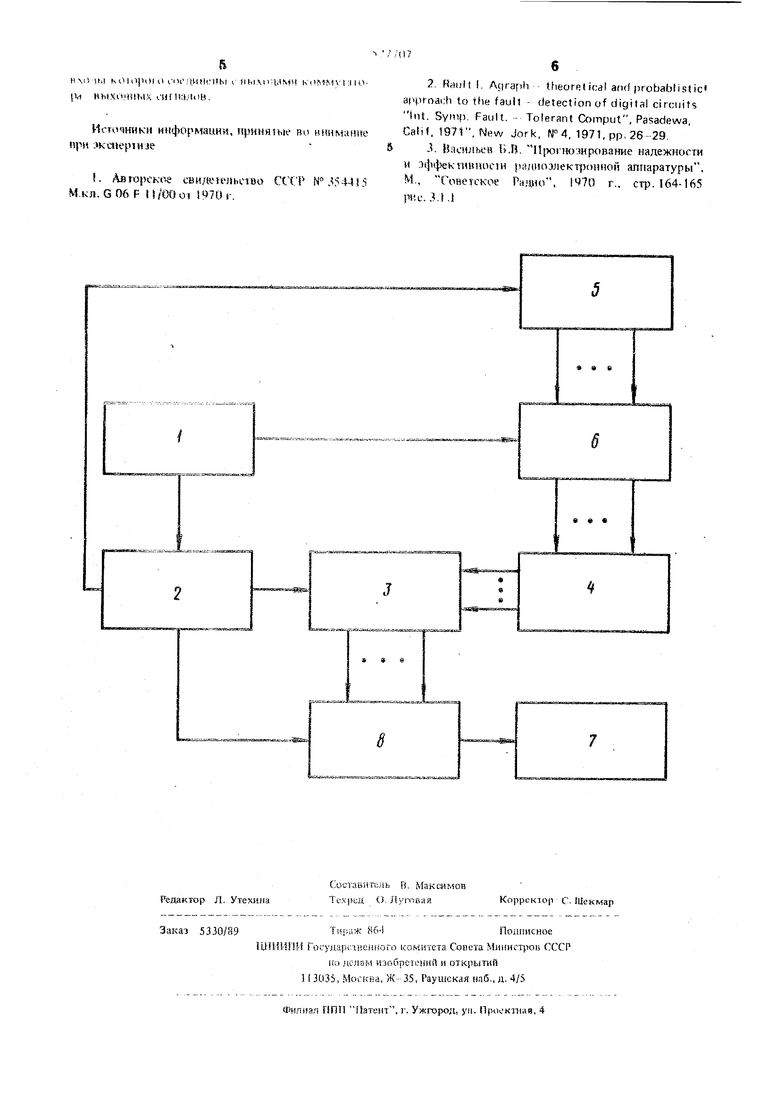

Блок-схема устройства изображена на чертеж ;.

Ус1ройетзо состоит изблока ввода даянмх , бяока уггргаяегЕгл 2, коммутатора выход -Нз1х сигналов 3, КО:: фолнруег-ю-по логического блока 4, генератора елучзй иь5х Чисел S, преобразователя случайных чисел 6, блока индйкаши 7 и блока сташстческих акзлшяторов 8.

Устройство .работаем следующим образом.

С поТЛСПгыи б.мока в-водз данных 1 задаемся Hiii opTv;i5j.iiH о порядке подютю езздй контрольных ток-к кейтролируемого яо-гического блока 4 к инфс рй йцио} ным входам блока статистических аналнзатсров 8. о рабочей щстоте проверки и о требуег-(о;,1 законе рвшргделезвп случайных сигналов, г.остзшатоидмх 1та вход проверяемого блока.

В cooiBeicTBitH с этой информацией преобразователь настраивается на преобразовагме случайных чисел с равномерньгм законом распределения, поступающих с вьхода генератора случайных чисел 5, в 4Kcj;a с грейусмымраспредепением.

СпучаГпо ш сигналы с контрольных точек ко прол ;руемого блока 4 отымаются коммутатором .5 и передаются на входы статистических анали3aiopoii в ,ке, О1)реяеля.емом блоком управлзrei3 2 в соответствии с информацией, поступающей с блока ввода данных 1. Анализаторы блока 8 определ К)т отклоне ше математических олшданий случяйных сигналов от заданной величины и в случае, есл5Е эти отк;10 -;ения нрезьглают заданный уровень, выдД|ОТ сообщения в блок кнл.икаи,ии 7, который О1Гиали;йГ1)уст о наличин нсистраумости и номере котрол),ой точки, в которой эча 1 сисправi юсть 3ai|)si;-: ci s poiui; га.

Блок yiipaiijjCHKH 2 также управлясг рабочей частою ; гсг;ерачора c.ryi.aiiHbix чисс.ч 5 и сиихроннзирус рапагу ан;,лизатора 8.

ПересspoiiKa ; .:гройсп а при иодаче lia проверку нового лошчссгсого fjioKa может осущесталяться дяонко. В (, Полое простом, варианте ртравлс1мс нрсоОразопателем случайных Щ1сел не ocyiticcTB.iiieicH, т.е. оя либо настроен иостоянно на т.);к;)остис1 1| к ирес)Г)рп:), либо исключс из схемы. Иифирм:11г; И о кои ролируемом блоке задас ся в Клпс Jiajioiinijix значений матемашчсских o:w Дании сши.иил в ксапрольных точках и iiuciy4

5aei непосредсгвенно в блок ста1неги скя,, шипи затороз 8. Эгог йюсоб Tjwfjyei, как правило, мень1 Е объема вхояной информации, предааригелыюе получение этой информации несложно. Однако такой способ не обеспечивает стопроцентную полноту контроля некоторых типов проверяемых блоков.

Второй, &эг{ее угечверсальный, вариаит предусматривает задание входной информации в виде

настроечных сигналов для преобразователя случайных чисел 6. Этот способ позволяет добиться макшмальной полноты контроля, а также обеспечить стандартную веливдну эталонных значений математеческого ожидания сигналов в контрольных точках контролируемого блока, что позволяет нсклютать перестройку статистических анализаторов. Последний способ особенно удобен, если число контрольных точек велико и мяогае из них относятся к независимо работающим частям контролируемого логического блока.

Возможно также совместное и пользование обоих они санных способов, позволяющее добиться оптимальной (в смысле объема входной информации, а также полноты контроля) орга1шзации проверки.

Применение данного устройства позволяет при незначительном увеличении аппаратурных затрат производить контроль произвольных отдельных логических блоков и диагностику их неисправностей,

обеспечить смену наборов сигналов на входе контро.пируемого блока с частотой, с максимальной частотой срабатьшания этого блока в условиях эксплуатации. Предлагаемое устройство исключает использование для контроля тестовых

последовательностей сигналов, соответственно не требуется больших ЗУ для хранения этих последовательностей, что С1шжает его стоимость и повышает надежность.

Формула изобретения

Устройство для статистического контроля логеческих блоков, содержащее последовательно соединенные блок ввода данных, блок управления, коммутатор выходных сигналов, входы которого соединены с выходами контролируемого логического блока, блок индикации, генератор случайных чисел, вход которого соединен с блоком управления, преобразователь случайных чисел, информадио}шые входы которого соединены с выходами

генератора случайных чисел, а управляющий вход -

с выходом блока ввода данных, отличающеес я тем, что, с целью расширения области применешя усзройства, оно содержит блок статистических анализаторов; причем выходы преобразователя случайных чисел соединены со входами контролируемого логического блока, а вход блока индикации - с выходом блока управления через блок

статистических анализаторов, информационные им) Uil KOh1|U)J о tiV/lH l -l bl I KOMMVt U lO|Vi HbiXO.ititMX Oiiinri.iiilB. Исгочшжн итгформации, принятые во шшлпоше при : Kc«epiHje . AsropcK-ite сви/лчельство СОР N 354415 М.кл. G 06 F И/00 О 1970 г. 2.Rault I. Лс)гарИ - theorfilical and probablist ic to ttie fault - detection of digital circuits int. Sy(ip. Fault. - Tolerant Compul, Pasadewa, Caiif. 1971, New Jork, ff 4, 1971, pp, 26-29. 3.Иасильев Б.В. Пртпю.шрование надежности « эффч;ктивнос и (1элекг()()пнон аппаратуры, Советское Радио, |Ч70 г.. стр. 164-165 рис. 3.1.1

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для статистического контроля логических блоков | 1983 |

|

SU1173415A1 |

| Устройство для статистического контроля логических блоков | 1976 |

|

SU615481A2 |

| Способ статистического контроля цифровых устройств | 1978 |

|

SU723591A1 |

| Обучающее устройство | 1978 |

|

SU752454A1 |

| Устройство для контроля памяти | 1981 |

|

SU982100A1 |

| Устройство прогнозирования работоспособности радиоэлектронной аппаратуры | 1984 |

|

SU1264116A1 |

| Устройство для статистического контроля логических блоков | 1976 |

|

SU652564A1 |

| Устройство для контроля цифровых блоков | 1982 |

|

SU1037261A1 |

| Устройство для статистическогоМОдЕлиРОВАНия пРОизВОдСТВЕННыХпРОцЕССОВ | 1977 |

|

SU796854A1 |

| СТАТИСТИЧЕСКИЙ АНАЛИЗАТОР | 1972 |

|

SU328468A1 |

Авторы

Даты

1976-09-05—Публикация

1974-02-18—Подача