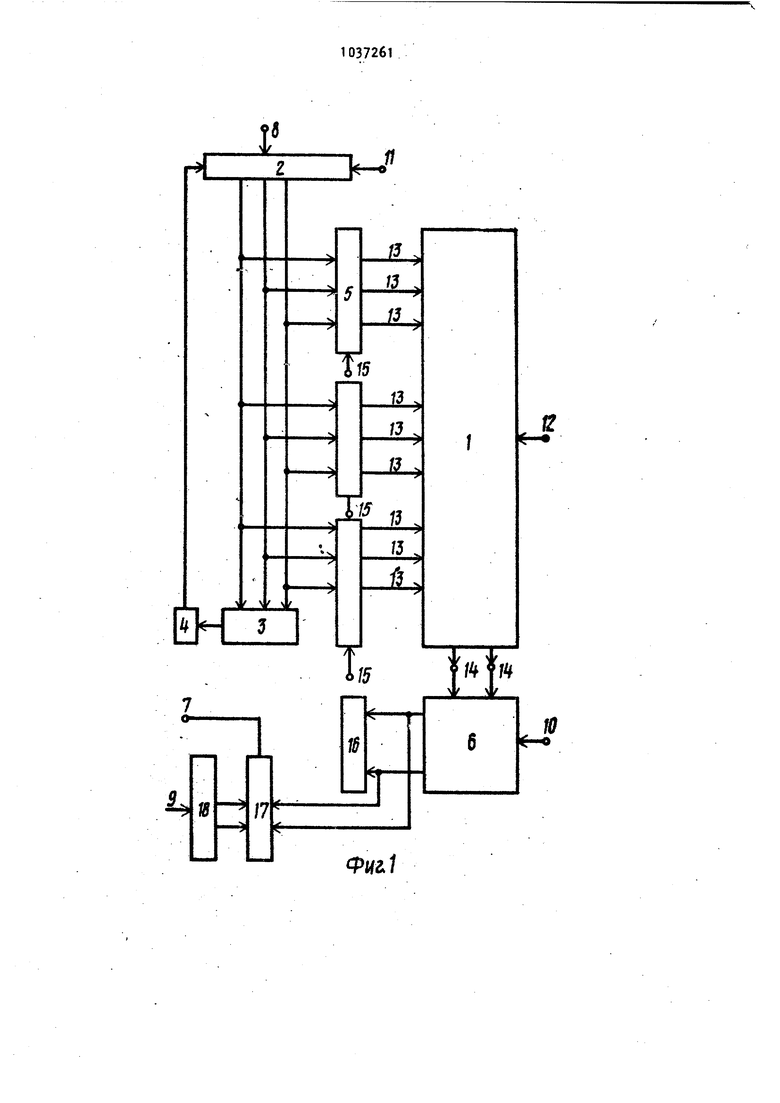

Изобретение относится к вычислиотельной технике, э именно к контролю цифровых устройота Известно устройство для проверки полноты тестов, содержащее генерато тестов, модель объекта контроля, эталонный, блок, блок сравнения, бло ввода неисправностей, два счетчика, делитель, датчик случайных чисел и блок управления, причем выход генер тора тестов соединен с входами моде ли объекта контроля и эталонного блока, которых соединены с входами блока сравнения, выход кото рого соединен с входом блока управ™ ления и входом первого счетчика, вы ходы первого и второго счетчиков со динены с входами делителя, выходы к торых являются выходами устройства, выход блока управления соединен с входами генератора тестов, второго счетчика и датчика случайных чисел, выход которого через блок ввода неисправностей соединен с моделью объ екта контроля С Недостатками данного устройства являются необходимость эталонного блока и сло); ностьл. получения полной системы переходов тестовых набороа. Наиболее близким к предлагаемому по технической сущности является устройство для контроля интегральны схем,- содержащее блок 8вод;3 информа ции, блок управления, группу входны сумматоров, две группы коммутаторов группы входных регистров сдвига, группу выходных сумматоров, группу блоков индикации5 блок сравнения, многоканальный амплитудный дискриминатор, и генератор тактовь х импульсов, причем зыход генераюра тактовых импульсов соединен с первы ми, входами входных сумматоров группы, выходы которых аоединены с входами входных регистров сдвига группы, выходы которых соединены с входами соответствующих коммутаторов первой группы, выходы которых соединены с вторыми входами соответствующих входных сумматоров группы, выходы старших разрядов входных регистров сдвига группы соединены с входами контролируемой интегральной схемы, выходы которой соединены с входами многоканг льного амплитуднего дискриминатора, информационные выходы которого -соединены с первыми входами соответствуклцих выходных сумматоров группы,- выходы которых соединены с входами выходных регистров сдвига группы, выходы которых соединены с входами -коммутаторов второй группы, выходы кото- рых соединены с вторыми входами выходных сумматоров группы, выходы выходных регистров сдвига группы соединены с входами соответствующих блоков индикации и первой группой эходов блока сравнения, вторая группа входов которого соединена с входами начальных установок входных регистров сдвига группы и выходами блока ввода инс юрмации, выходы блока сразнения соединены с входами блока -управления, выход которого соединен с входами начальных установок выходных регистров сдвига группы и входом запуска генератора тактовых импульсов t2. Однако формирование входных тестовых наборов с полной системой переходов известным устройством оказывается сложным, особенно при большом количестве входов проверяемого цифрового устройства, так как для каждого входа требуется о-гдельный .-.ногоразрядный регистр сдвига с суммач-орами и комму-гаторами в цепи регистра. Цель изобретения - расширение функциональных возможностей устройства путем формирования полной системы переходов тестовых наборов. Поставленная цель достигается тем, что в устройство для контроля цифровых блоков, содержащее регистр сдвига, сумматор по модулю два, коммутатор, блок индикации, блок сравнения, блок свертки выходных сигналов, регистр эталонов, причем- регистра сдвига соединены с входами коммутатора, выходы которого соединены с входами сумматора по модулю два, выход которого соединен с информационным входом регистра сдвига, сдвиговый вход которого является шиной сдвига устройства, вх-оды блока свертки выходных сигналов соединены с выходами контролируемого блока, выходы блока-свертки выходных сигналов соединены с входами блока индикации и первой группой входов блока сравненияS вторая группа входов которого соединена с выходами регистра эталонов, выход блока сравнения является шиной результата контроля устройства, входы начальных устано3вок регистра сдвига, регистра этало нов и блока свертки выходных сигналов -являются соответственно первой, второй и третьей шинами начальных установок устройства, введена группа коммутаторов, информационные вхо.ды которых соединены с выходами регистра сдвига, а выходы соединены с соответствующими группами входов контролируемого блока, установочные входы коммутаторов группы являются установочными входами .устройства. Кроме того, каждый коммутатор пы содержит дешифратор, группу элементов ИЛИ, К групп элементов И (, где п - количество разрядов регистра сдвига), причем первые входы элементов И К-й группы соединены с К-м выходом деши ратора, выход каждого j-ro элемента И К-й группы соединен с соответству ИЛИ группы ющим входом j-элемента (1 j -j), выходы которых являются выходами коммутатора, второй вход каждого j-ro элемента И К-й группы соединен с i-м информационным входом коммутатора (, , i K{j-1)+1), входы дешифратора являются установочными входами коммутатора. На фиг. 1 приведена структурная схема устройства для контроля цифровых блоков; на фиг. 2 - структурная схема коммутатора группы для . Устройство содержит контролируемый блок 1, регистр 2 сдвига, комму татор 3, сумматор по. модулю два , группу 5 коммутаторов, блок 6 сверт ки выходных сигналов, шину 7 резуль тата контроля устройства, шины 8-10 .начальных установок устройства,шину 41 сдвига устройства, шину 12 активизации контролируемого блока 1, вы ды 13 коммутаторов группы и группу 1 выходов контролируемого блока 1, установочные входы 15 коммутаторов группы, блок 16 индикации, блок 17 сравнения, регистр 18 эталонов. Коммутатор группы (фиг. 2) содер жит группу 19 элементов И, группу 20 элементов И, дешифратор 21. Устройство работает следующим об .разом. Регистр 2 сдвига, коммутатор 3, сумматор по модулю два k образуют структуру линейной автономной после довательностной цепи, которая обеспечивает получение двоичной после1овательности максимальной длины с периодом (2 -1) бит, где п - количество разрядов (параллельных выходов }регистра 2 сдвига, при подаче импульсов сдвига на шину 11 сдвига устройства. Выходы 13 коммутаторов труппы 5 образуют группу выходов, с которых могут сниматься двоичные тестовые наборы с полной системой в процессе контроля блока Г. К-й коммутатор разрешает прохождение на асе свои j-e выходы импульсов, удовлетворя)0щих уравнению (j-f) , (1) где 1iiin;1 j Y Порядок h системы переходов К-го коммутатора группы 5 (Ь,) характеризует расстояние между соседними разрядами регистра 2 сдвига, с которых снимается информация, определяемое .минимальным количест- , вом разрядов регистра, заключенных между этими разрядами. Например, для получения двухразрядных тестовых наборов () с порядком 1 системы переходов () на выходы 13 коммутатором группы 5 подается информация с первого и третьего разрядов регистра 2 сдвига. . При этом в каждом такте сдвига набор оС2С -| переходит в набор который определяется содержанием второго и четвертого разрядов регистра 2 сдвига. Так как регистр 2 сдвига образует все возможные (п-1)-элементные комбинации, указанные наборы могут быть любыми, что и обеспечивает пол- ноту системы переходов 1-го порядка тестовых наборов. Указанную систему переходов нельзя получить при снятии набора со смежных разрядов регистра, например 1-го и 2-го, так как в этом случае в каждом такте сдвига возможен переход произвольного набора {ot2°ij только в два набора: о, и.{1,оС2,а не четыре набора rp2ft| 3K было рассмотрено. Коммутатор группы 5 обеспечивает передачу информации с параллельных разрядов регистра 2 сдвига на выходы 13 в зависимости от требуемой величины порядка переходов тестовых наборов h.

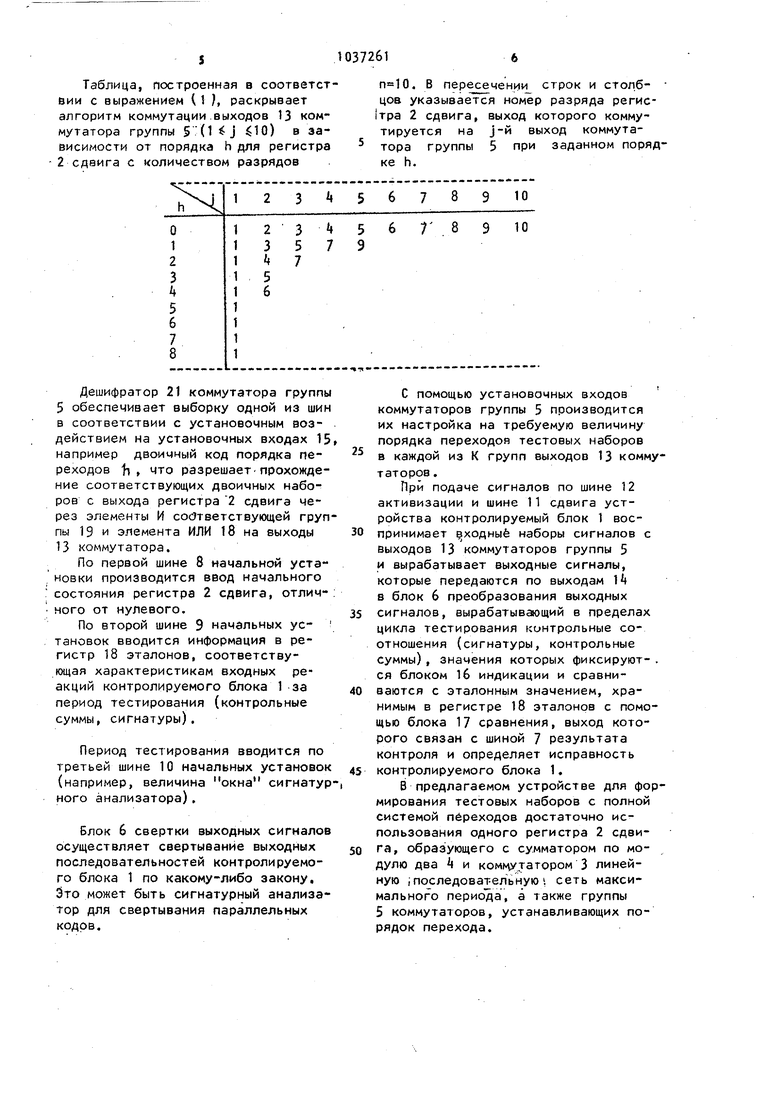

Таблица, построенная в соответствии с выражением (1 J, раскрывает алгоритм коммутации.выходов 13 ком мутатора группы 5( Ю) в зависимости от порядка h для регистра 2 сдвига с количеством разрядов

. В пересечении строк и столбцов указывается номер разряда регистра 2 сдвига, выход которого коммутируется на j-й выход коммутатора группы 5 при заданном порядке h.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля логических блоков | 1986 |

|

SU1336011A2 |

| Устройство для контроля цифровых узлов | 1980 |

|

SU911532A1 |

| Устройство для контроля интегральных схем | 1978 |

|

SU744579A1 |

| Система для контроля сложных релейных распределителей | 1985 |

|

SU1252780A1 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1553978A1 |

| Устройство для контроля логических узлов | 1980 |

|

SU890398A1 |

| Устройство для контроля многовы-ХОдНыХ цифРОВыХ узлОВ | 1979 |

|

SU817721A1 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1539782A2 |

| Устройство для контроля и диагностики цифровых блоков | 1985 |

|

SU1312580A1 |

| Устройство для контроля и диагностики логических узлов | 1980 |

|

SU960825A1 |

Дешифратор 21 коммутатора группы 5 обеспечивает выборку одной из шин в соответствии с установочным воздействием на установочных входах 15 например двоичный код порядка переходов fj , что разрешаетпрохождение соответствующих двоичных наборов с выхода регистра 2 сдвига через элементы И сосЗтветствующей груп пы 19 и элемента ИЛИ 18 на выходы 13 коммутатора. По первой шине 8 начальной установки производится ввод начального состояния регистра 2 сдвига, отличного от нулевого. По второй шине 9 начальных установок вводится информация в регистр 18 эталонов, соответствующая характеристикам входных реакций контролируемого блока 1 за период тестирования (контрольные суммы, сигнатуры). Период тестирования вводится по третьей шине 10 начальных установок (например, величина окна сигнатур ного анализатора). Блок 6 свертки выходных сигналов осуществляет свертывание выходных последовательностей контролируемого блока 1 по какому-либо закону, Это может быть сигнатурный анализатор для свертывания параллельных кодов. С помощью установочных входов коммутаторов группы 5 производится их настройка на требуемую величину порядка переходов тестовых наборов в каждой из К групп выходов 13 коммутаторов , При подаче сигналов по шине 12 активизации и шине 11 сдвига устройства контролируемый блок 1 воспринимает входные наборы сигналов с выходов 13 коммутаторов группы 5 и вырабатывает выходные сигналы, которые передаются по выходам 1 в блок 6 преобразования выходных сигналов, вырабатывающий в пределах цикла тестирования контрольные соотношения (сигнатуры, контрольные суммы), значения которых фиксируют- . ся блоком 16 индикации и сравниваются с эталонным значением, хранимым в регистре 18 эталонов с помощью блока 17 сравнения, выход которого связан с шиной 7 результата контроля и определяет исправность контролируемого блока 1, В предлагаемом устройстве для формирования тестовых наборов с полной системой переходов достаточно использования одного регистра 2 сдвига, образующего с сумматором по модулю два k и ком(« татором 3 линейную iпоследовательнуюi сеть максимального периЬда, а также группы 5 коммутаторов, устанавливающих порядок перехода.

Авторы

Даты

1983-08-23—Публикация

1982-04-16—Подача