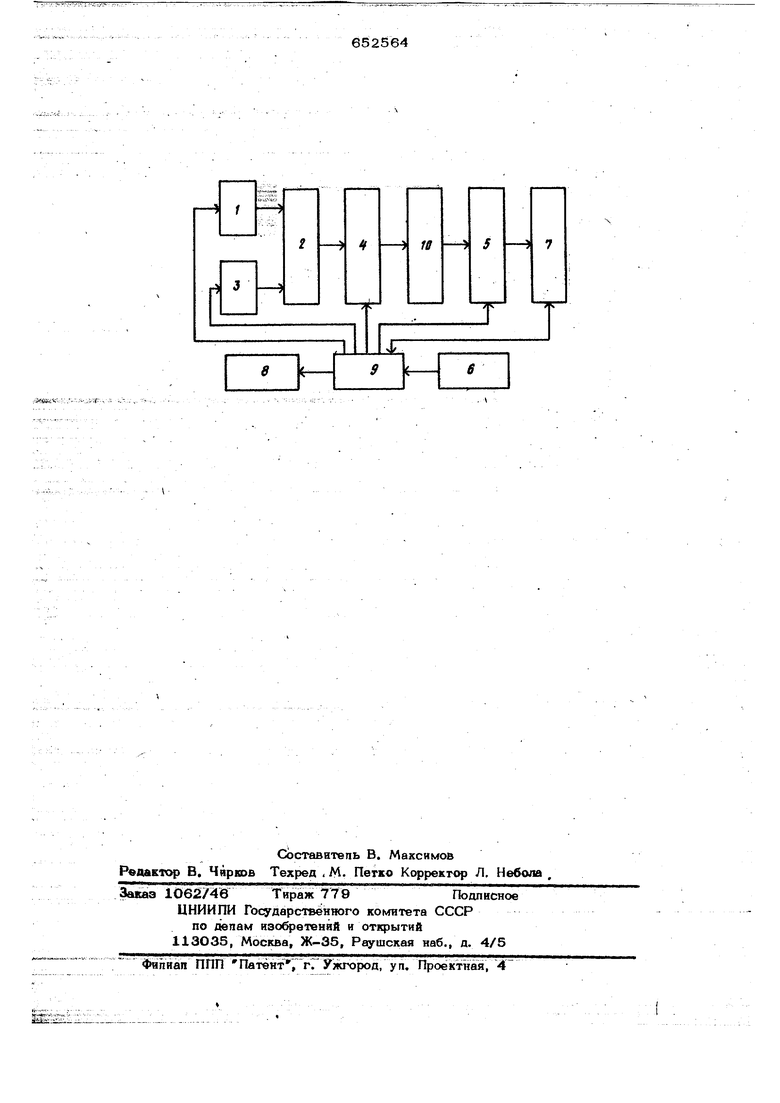

но поспедо1ав1«пьно авдешать на ,т из п генератора уровень яогической ,, тей самым пошшая вероятность переключения погического гостояния выхода до веяичины Р йгРпГ -Леобходимость выполнения указанных требований ве дет к еще большему усложнению генератора и преобразователя случайных чисел. Целью изобретения {Шляется упроше- ине устройства статистического коитроп .Цифровых схем, в частности, за счёт йс кшрчения иа него внешнего аппаратно { ёаянэбюаншяч} генератора и преобразователя свучайных или псевдосяучайшдх чясев. Поставленная цепь достигается тем, яо устройство содержит генератор опсф мЫ1 поспедоватепьности HMiqrnbcc, ампяпудный модулятор и генератор напря)неяия, выход которого соединен с перiabffifBxdflOM амплитудного модулятора, второй вход которого соединен с выходом генератора опорной последоватепьностн яияуяъсов, выход - с блоком комк(утапии входов, а соответствующие выхоаы блока управления соединены с вхо дами генератора опорной последовательности и М1 льсов а генератора напряжетя. На чертеже приведена блок-ч:хема уст ройства для статистического 1юнтроля психических блоков. Устройство содержит генератор 1 опорной последовательности импульсов, а1Л(п«тудш 1й модулятор 2, генератор 3 иапряхюния, блок 4 коммутации входов, блок 5 ком(тапик выходов, блок 6 вво да данных, блок 7 статистических анализаторов, блок 8 индикации, блок 9 упраьвения. Объект 10 контроля подключа ется кблокам 4 и 5 коммутации входов и {щходов. Принцип работы устройства основан на тем, что цифровые логические блоки являются пороговыми Элементами с ре лейяымя статическими переходными хар;бЁктер8стиками, определявмыъ«и эначе;виям« входных пороговых напряжений яое Вследствие технологического vaytfia, конкретному производ ству, величины порогсаяял напряжений Ло гических блоков, (хюдйнных в течение оШого и ТйЕЧэ з«е технологического цикл являются случайными 19еличинами. Если объединить N входов логическ ио блогка, а в оби9ю точку подать последоваteabHo Tb имцульсов с амплитудой, увелячвв Уошейся но известному закону От уровня логического О до уровня логической , то; вследствие релейного характера передаточной характеристики логического блока на его входы будут поступать -разрядные случайные двоичные числа. Лля повышешя универсальности (в частн применения заявленного устройства ОЛЯ контроля нмпульсно-потенпнальных блоков и блоков с памятью) в общую точку подается а мплиту дно-моду л ированная последовательность прямсугольных импульсе. Пусть разность порогевых,напряжений i -го и (i+1) входов и и..равна &,bf ,a каждый последующий отличается От предыдущего по амплктуае на величину л и , прячем А и « А Ц Следовательно, на входы логического эяемеята какоето врекга, (шределяемое временем нарастания модунит ющего напряжения, будут поступать однН я те же двоичные числа, т.е. формируется пачка двойчш чисел, прячем количествочясел в пачке К . 7777 Зои является также величиной случайной. Таким образом, если на общую точку подать последовательность импуяьсс« с аШЕлйтудой, увеличивающейся по известному закону от уровня логического О . до уровня логической , то на входы логического блока будут поступать Н-раэрядные двоичнь1е числа от исходнсво состояния - ООО...ООО (вслучае, амплитуда импульсов меньдае минимального порогового напряжения) до конечного состояния - 111...111 (когда амплитуда ии«1ульс ж больше максимального порогового напряжения). Г%юверка блока состоит в том, что путем подачи амппитудно-модулированной импульсной , последовательности в точку, объединяющую входы проверяемой Ьхемы, имитируется подключение ко входам объекта контроля W -рааряднсяо ге1юратора сщгчай{шх двоичных чисел. функциональное назначение блоков сострит в следующем. Блок 4 коммутации входов объединяет входы, объекта контроля и пояквючёет к выходу амплитудного модулятора 3. С помощью блока 5 выходы объекта 1О контроля подключаютя к блоку 7 статистических анализатоов, который «шредевяет статические; параметры даОячяой последовательности иШ гльссв по каждому выходу. Например, определгвется вероятность появления W-{ 56 количества погическнх по j выход т.е. где К i - количество .импульсов в пачк Полученная величина сравнивается в бло ке 9 управления с известной величиной, поступа с 1цей иэ блока 6 ввода данных. Кроме того, блок 9 осуществляет управ ление работой остальных блоков устройства согласно программе контроля. Вся оперативная информация отображается с помощью блока индика|щи ti. Устройство работает следующим обра зом. вырабатываемая генератором 1 имяульсоЕ опорная последовательность поступает на первый вход амплитудного модулятора 2, на второй вход KOTCf oro поступает изменяющееся по известному закону ншфяжение от генератора 3. С выхода амплитудного модулятора 2 модулированная (например, по линейному закону) последовательность импульсов поступает через блок 4 коммутации вхо дов на соединенные параллельно входы объекта Ю контроля. достижении амплитуды импульсов значения минимапь нстО порога на входах контролируемого лсяического блока появляется первая пачка случайных двоичных чисел, отличных от исходного числа (ООО...ООО) Количество случайных чисел в пачке определяется разностью значений ближайших пороговых напряжений. При достижении амплитудой импульсе следующего порог ого уровня генерируется вторая пачка случайных двоичных чисел и т.д. до достижения конечного СОСТОЯНИЯ на входах гфоверяемой схемы 111...111. За время цикла контроля блок 7 статнствческих анализаторов, подклюяюнный к тлходу объекта 10 контроля через бло 5 |И мк тациа выходов, определяет статиствчесхую характеристику выходной последователыюсти, например, вероятность появления заранее известного копвчества л и ических по каждому вы ходу. По сравнению с известными устройствамв сггатястического контроля цифроаых схем предлагаемое устройство суоюстееово проще, так как в генерато4ре случайных чисел, выполненном, например, на сдвиговых регистрах, при использовании интегральных микросхем серии 155, требуется, как минимум, один Э -К триггер на разряд регистра, один R - S триггер И один вентиль схемы маскирования этого разряда. Таким образом, для построения генератора случайных чисел с количеством выходов, равным 2ОО, требуется 20О корпусов 3 -К триггер, 1ОО корпусов R- S триггере, 5О корпусов вентилей и около 5О корпусов интегральных микросхем Ш1Я организашси цепей обратной связи и управления. Следовательно, обшее количество корпусов интегральных микросхем составляет приблизительно 4ООшт. Для реализации генератора стимулирующих воздействий по предлагаемому изобретекию требуется не более 2О шт. корпусов интегральных микросхем. Формупаизобретения Устройство для статистического контроля логических блоков, содержащее блок комиутации входов, бпок коммутации выходов, соединенный с блоком статистических анализаторов и последовательно соединенные бпок ввода данных, блок управления и бпок индикации, ЕШХОДЫ блока упра впения соединены соответственно с входами бпоков коммутации входов и выходов и блоком статистических анализаторов, отпйчаюшеес я тем, 9ТО, с целью упрощения уст ройства, оно содержит генератор опорной последовательности импульсов, aii nлитудный модулятор и генератор напряжения, выход которого соединен с первым входом амплитудного модулятора, второй вход которого соединен с выходом генератора опорной последовательности импульсов, выход - с блоком коммутации входов, а соответствующие выходы блока управления соединены с входами генератора опорной после дсжательности импульсов и генератора напряяюния. Источники информации, принятые во вниман 1е при экспертизе 1.. Патент США N 36146О8, кя. 324-7 ЗР, 1972. 2, Авторское свидетельство СССР № 527707, Кп. Q Об F 11/ОО, 18.О2.74.

; iTe ;v;;/-.4.,:iv.

| название | год | авторы | номер документа |

|---|---|---|---|

| Способ статистического контроля цифровых устройств | 1978 |

|

SU723591A1 |

| Устройство для статистического контроля логических блоков | 1976 |

|

SU615481A2 |

| СИСТЕМА РАДИОСВЯЗИ | 2005 |

|

RU2296428C1 |

| ВОЛОКОННО-ОПТИЧЕСКАЯ СИСТЕМА С БЕЗОПАСНОЙ ПЕРЕДАЧЕЙ ИНФОРМАЦИИ | 1995 |

|

RU2100906C1 |

| РАДИОПРИЕМНОЕ УСТРОЙСТВО МНОГОЧАСТОТНЫХ СИГНАЛОВ | 2005 |

|

RU2310992C2 |

| Анализатор амплитудно-временных параметров случайных сигналов | 1983 |

|

SU1179228A1 |

| Устройство аварийной сигнализации | 1980 |

|

SU905458A1 |

| Устройство для проведения матричныхиСпыТАНий МиКРОэлЕКТРОННыХ CXEM | 1979 |

|

SU851414A1 |

| Дельта-модулятор | 1987 |

|

SU1508350A2 |

| Устройство для контроля логических блоков | 1986 |

|

SU1388873A1 |

Авторы

Даты

1979-03-15—Публикация

1976-12-03—Подача