1

Изобретение относится к заломи- нающим устройствам, в частности .федназначено для входного функционального контроля полупроводниковых оперативных запоминающих устройств (ОЗУ) с произвольной выборкой .

Известно устройство для контроля памяти, содержащее генератор случайных чисел, построенный на регистре сдвига, который вырабатывает тесты на основе линейных и нелинейных случайных кодовых комбинаций (1 3.

Недостаток данного устройства состоит в низкой достоверности контроля за счет возможности появления на выходе контролируемого блока памяти неопределенных состояний, поскольку среди входных наборов встречаются запрещенные комбинации, а также в невозможности определения статистических характеристик работы контролируемого блока памяти.

Наиболее близким к изобретению является устройство для контроля блоков памяти, содержащее блок управления, блок памяти, генератор случайных чисеп, блок сравнения, контрольный выход которого соединен с первым входом {5лока управления 2.

/

Недостатком этого устройства является необходимость перед контролем блока памяти гаписывать в него

10 конкретный тест, являющийся произ; водным адресной информации, что снижает достоверность контроля ввиду невозможности выявить все взаимовлияния элементов, а также случайных сбоев в блоке памяти на его рабочей частоте. Кроме того, данное ; устройство не позволяет определить, статистические характеристики работы контролируемого блока памяти.

20

Целью изобретения является повышение надежности устройства.

Поставленная цель достигается тем, что в устройство для контроля

памяти, содержащее генератор случайных чис., схему сравнения, блок индикации и блок управления, первый и второй-входы которого подключены соответственно к одним из выходов генератора случайных чисел и схемы сравнения, другие выходы которой соединены с одними иа входов блока индикации, другой вход которого подключен к первому выходу блока управления ,, второй вход которого соединен с одним из выходов генератора случайных чисел, введены блок местного управления и статистический анализатор, управляющие входы которых подключены соответственно к третьему и четвертому выходам блока управления, входы блока местного управления ч оединены с другими, выходами гене-. ратора случайных чисел, один из вы. ходов подключен к одному из входов статистического анализатора, выходы которого соединены со входами схемы сравнения, другие выходы блока местного управления и другой вход статистического анализатора являются соответственно выходами и входом устройства,,

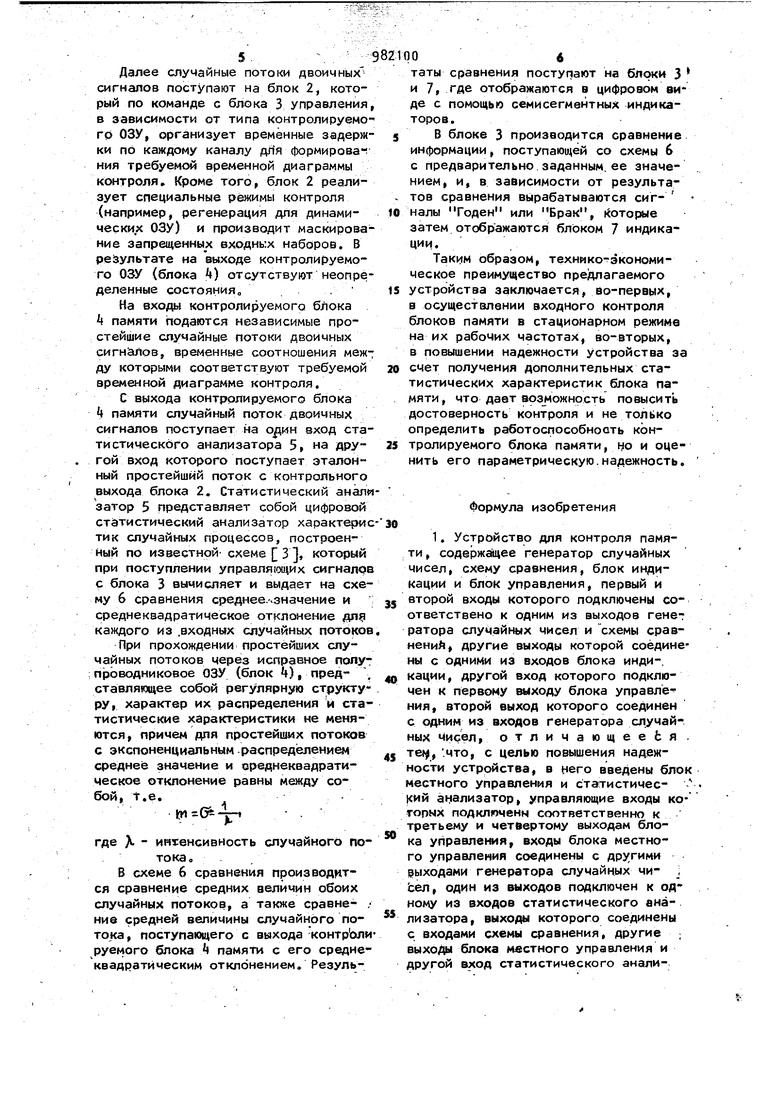

Кроме того, блок местного управле ния содержит формирователь тактовых сигналов, формирователи управляющих сигналов, формирователи инфор(1аи.ионных и адресных сигналов, элемент И, группы элементов И, генератор сигналоэ регенерации, выходы которого подключены соответственно ко входу счетчика и одному -сз входов триггера, мультиплексор, одни из входов которого соединены с выходами счетчика и выходом триггера, другой вход . которого подключен к одному из выходов мультиплексора, выходы формирователей информационных и адресных сигналов соединены соответственно с одними из входов элементов И первой группь) и с одними из входов элементов И второй группы, выходы которых подключены к другим входам мультиплексора, выход элемента И подключен ко входу формирователя тактовых сигналов, одним из входовфЬ|эмйрова телей управляющих сигналов и входам формирователей информационных сигналов и генератора сигналов регенерэ ции, входы элемента И и другие формирователей управляющих сигналов и элементов И групп являются входами блока, выходамикоторого яапяются выходы формирователя тактовых

сигналов, формироватапей управляющих; сигналов и элементов И первой группы И другие выходы мультиплексора.

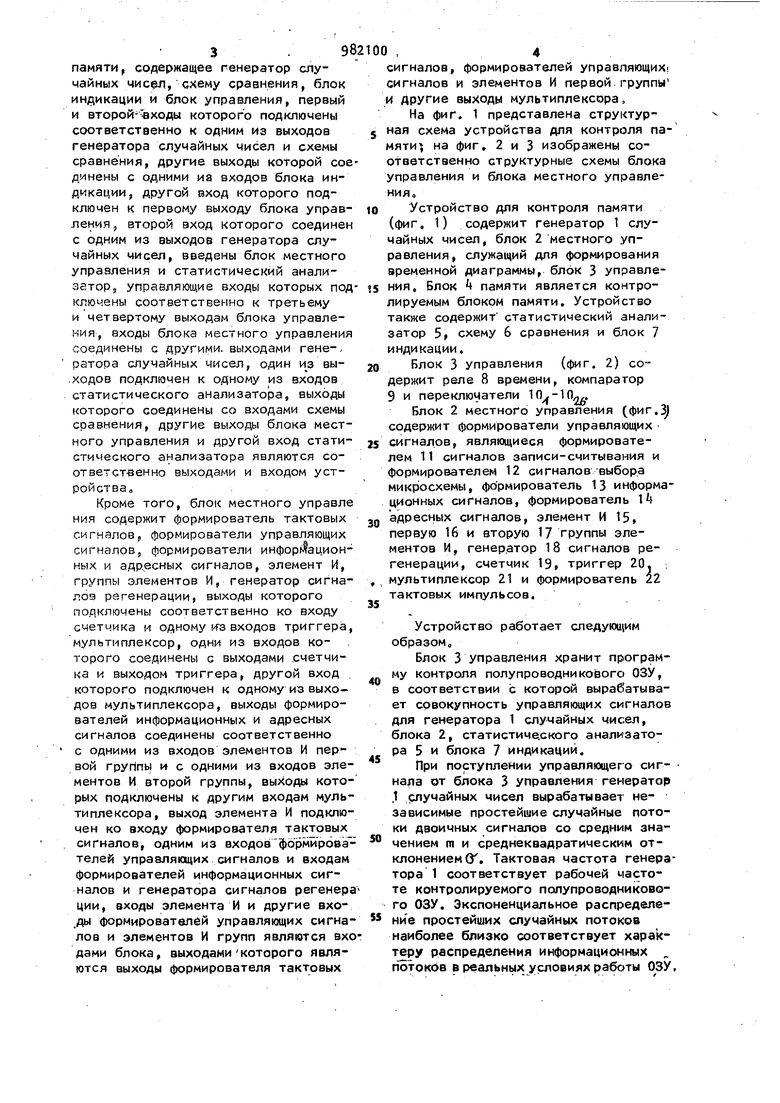

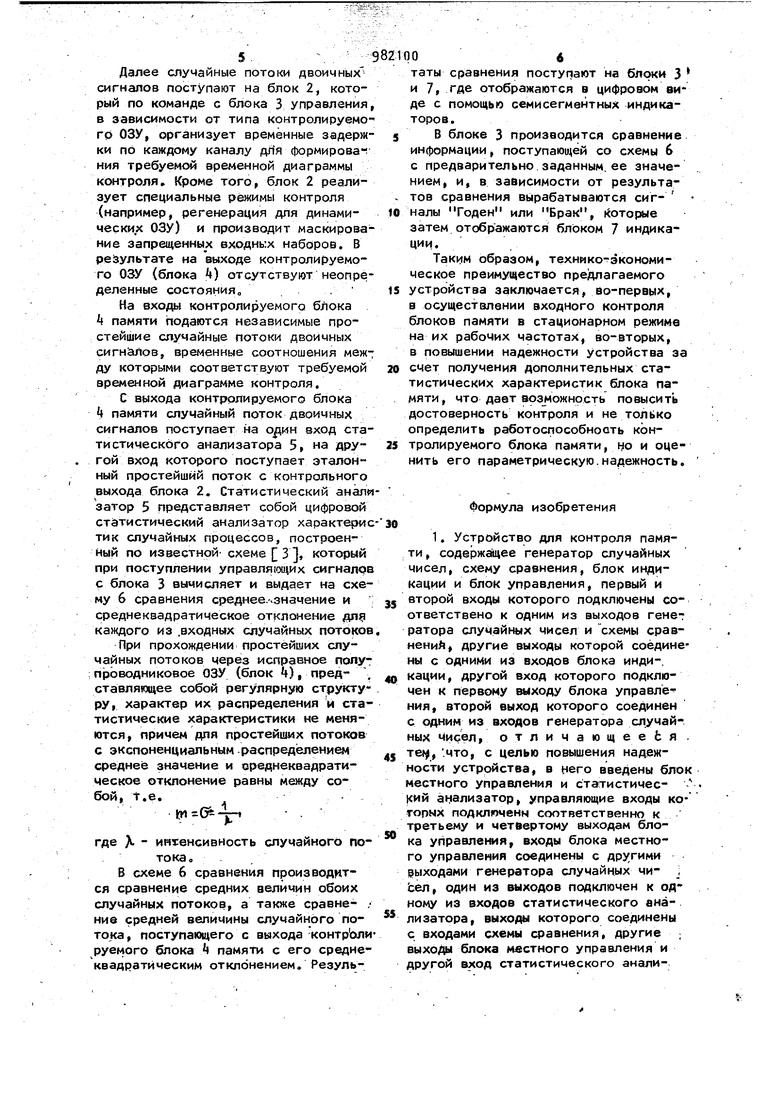

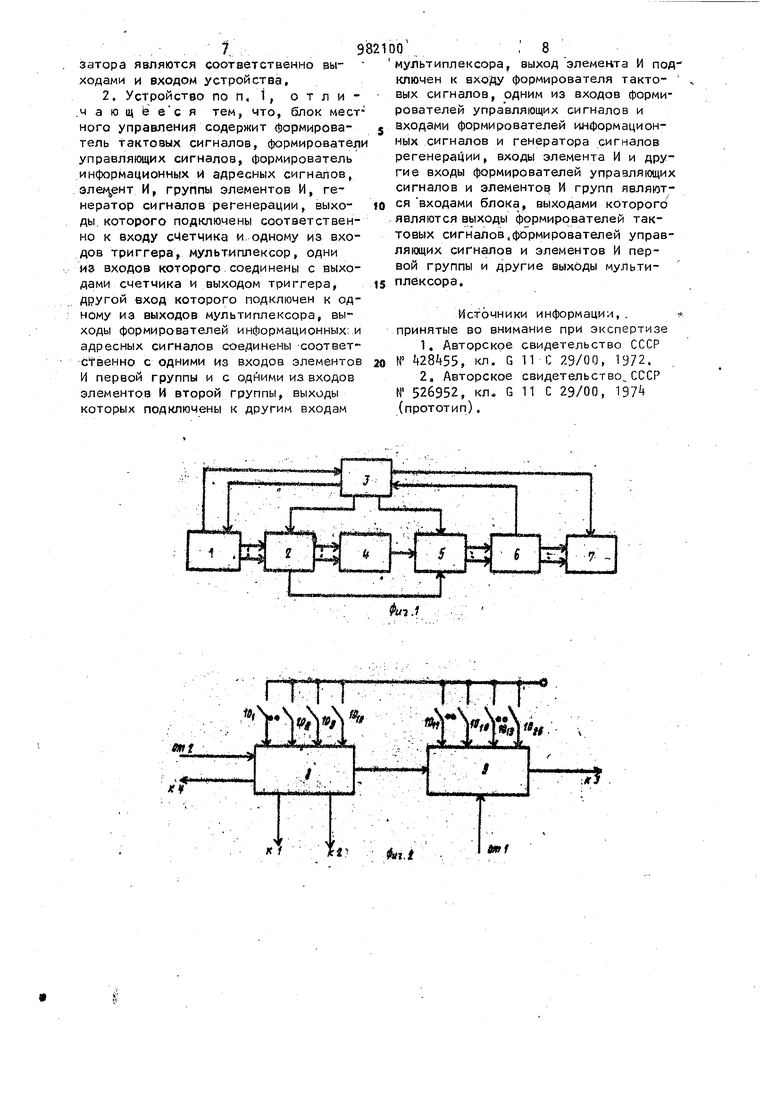

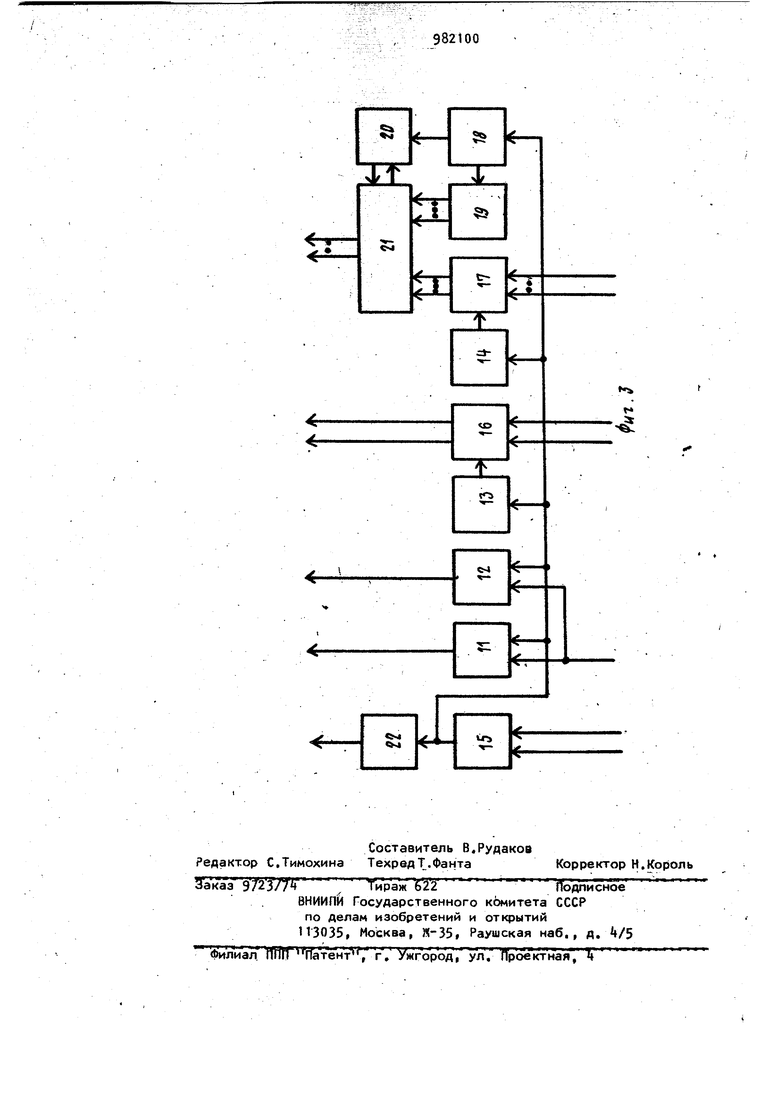

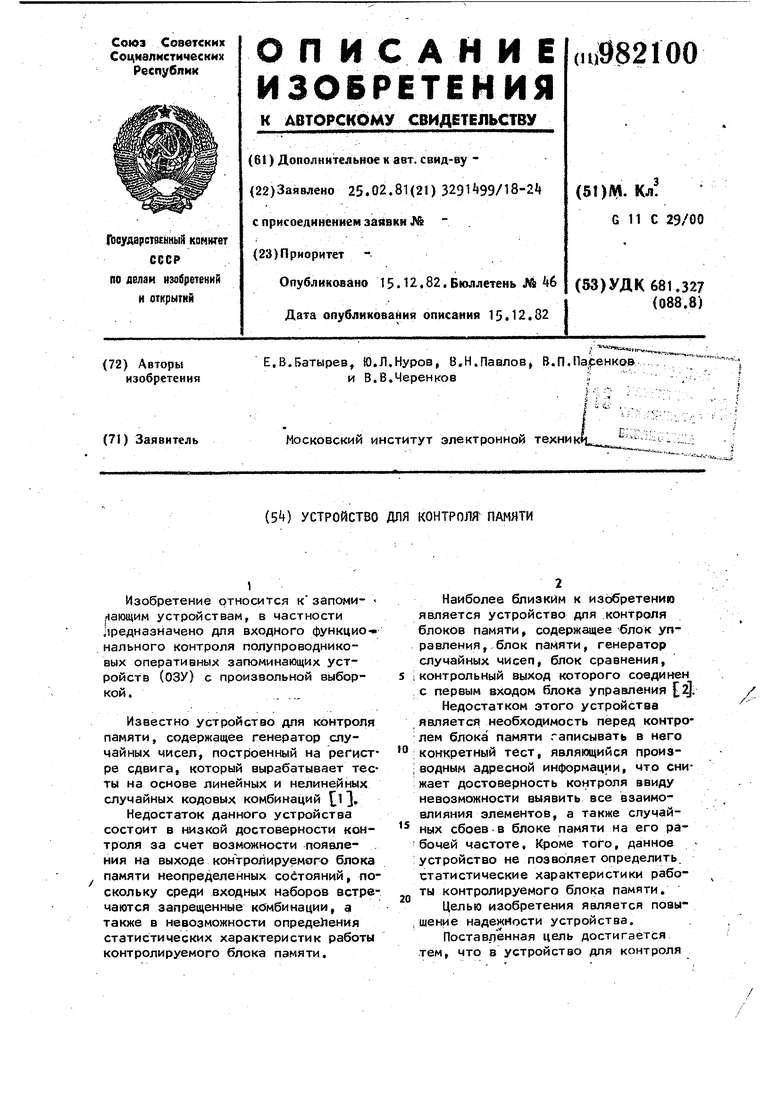

На фиг. 1 представлена структурная схема устройства для контроля памяти на фиг 2 и 3 изображены соответственно структурные схемы блока управления и блока местного управления,

Устройство для контроля памяти (фиг, 1) содержит генератор 1 случайных чисел, блок 2 местного управления, служащий для формирования временной диаграммы, блок 3 управления. Блок памяти является контролируемым блоком памяти. Устройство также содержит статистический анализатор 5, схему 6 сравнения и блок 7 индикации.

Блок 3 управления (фиг. 2) содержит реле 8 времени, компаратор 9 и переключатели

Блок 2 местного управления (фиг, содержит формирователи управляющих

сигналов, являющиеся формирователем 11 сигналов записи-считывания и формирователем 12 сигналов выбора микросхемы, формирователь 13 информационных сигналов, формирователь 1

адресных сигналов, элемент И 15, первую 16 и вторую 17 группы элементов И, генер.атор 18 сигналов регенерации, счетчик 19 триггер 20. .

мультиплексор 21 и формирователь 22 тактовых импульсов.

Устройство работает следующим образом.

Блок 3 управления хранит программу контроля полупроводникового ОЗУ, в соответствии с которой вырабатывает совокупность управляющих сигналов для генератора 1 случайных чисел, блока 2, статистического анализатора 5 и блока 7 индикаций.

При поступлении управляющего сиг- нала от блока 3 управления генератор .1 случайных чисел вырабатывает независимые простейшие случайные потоки двоичных сигналов со средним значением п и среднеквадратическим отклонением О . Тактовая частота генератора 1 соответствует рабочей частоте контролируемого полупроводникового ОЗУ. Экспоненциальное распределение простейших случайных потоков наиболее близко соответствует характ ру распределения информационных потокдв в реальных условиях работы ОЗУ. Далее случайные потоки двоичных сигналов поступают на блок 2, который по команде с блока 3 управления в зависимости от типа контролируемо гр ОЗУ, организует временные задерж ки по каждому каналу для формировач ния требуемой временной диаграммы контроля. Кроме того, блок 2 реализует специальные режимы контроля (например, регенерация для динамических ОЗУ) и производит маскирова ние запрещенных входных наборов. В результате на выходе контролируемого ОЗУ (блока А) отсутствуют неопре деленные состояния . На входы контроли1эуемого блока k памяти подаются независимые простейшие случайные потоки двоичных сигналов, временные соотношения между которыми соответствуют требуемой временной диаграмме контроля. С выхода контролируемого блока k памяти случайный поток двоичных сигналов поступает йа вход статистического анализатора 5, на другой вход которого поступает эталон™ ный простейший поток с контрольного выхода блока 2. Статистический анали затор 5 представляет собой цифровой статистический анализатор характерис тик случайных процессов, построенный по известной- схеме 3, который при поступлении управлящих сигналов с блока 3 вычисляет и выдает на схему 6 сравнения среднее-- значение и среднеквадратическое отклонение дл каждого из .входных случайных потоков При прохождении простейших случайных потоков через исправное попу: проводниковое ОЗУ (блок ), пред- . ставляющее собой регулярную структуру, характер их распределения и статистические хара1сгеристики не меняются, причем для простейших потоков с экспоненциальным распред1элением среднее значение и ореднеквадратическое отклонение равны между собой. Т.е. --& где X - интенсивность случайного потока. В схеме 6 сравнения производится сравнение средних величин обоих случайных потоков, а также сравнение средней величины случайного по тока, поступающего с выхода контроли руемого блока Л памяти с его среднеквадратйческим отклонением. Результаты сравнения поступают на блоки 3 и 7, где отображаются в цифровом виде с помощью семисегментных индикаторов. В блоке 3 производится сравнение информации, поступающей со схемы 6 с предварительно заданным, ее значением, и, в зависимости от результатов сравнения вырабатываются сигналы Годен или Брак, (%ie затем отображаются блоком 7 индикации. Таким образом, технико- экономическое преимущество предлагаемого устройства заключается, во-первых, в осуществлении входного контроля блоков памяти в стационарном режиме на их рабочих частотах, во-вторых, в повышении надежности устройства за счет получения дополнительных статистических характеристик блока памяти, что дает возможность повысить достоверность контроля и не только определить работоспособность контролируемого блока памяти, но и оценить его параметрическую.надежность. Формула изобретения 1. Устройство для контроля памяти , содержащее генератор случайных чисел, схему сравнения, блок индикации и блок управления, первый и второй входы которого подключены соответствено к одним из выходов генератора случайных чисел и схемы сравнений, другие выходы которой соединены с одними из входов блока инди-. кации, другой вход которого подключен к первому вмходу блока управле ния, второй выход которого соединен с одним из входов генератора случайных Чисел, отличающееЬя. те, .что, с целью повышения надежности устройства, в него введены блок местного управления и статистичес- кий анализатор, управляющие входы топых подклпченн соответственно к третьему и четвертому выходам блока управленияу входы блока местного управления соединены с дру/ими выходами генератора случайных чиЬел, один из выходов подключен к оД ному из входов статистического анализатора, выходы которого соединены с входами схемы сравнения, другие ; блока местного управления и другой вход статистического аиалиf:9затора являются соответственно выходами и входом устройства, 2. Устройство по П. 1, о т л и .4 а ю |д е ес я тем, что, блок мест ного управления содержит фармирователь taKTOBbix сигналов, формировател управляющих сигналов, формирователь информационных И адресных сигналов, И, группы элементов И, генератор сигналов регенерации, выходы. которого подключены соответственно к входу сМетчика и. одному из входов триггера, мультиплексор, одни из входов которого соединены с выходами счетчика и выходом триггера, другой вход которого подключен к одному из выходов мультиплексора, выходы формирователей информационных; и адресных сигналов соединены -соответctBeHHo с одними из входов элементов И первой группы и с одйими из входов элементов И второй группы, выходы которых подключены к другим входам 0,,8 мультиплексора, выход элемента И подключен к входу формирователя тактовых сигналов, одним из входов формирователей управляющих сигналов и входами формирователей информационных сигналов и генератора сигналов регенерации, входы элемента И и другие входы формирователей управляющих сигналов и элементов И групп являются входами блока, выходами которого являются выходы формирователей тактовых сигналов,формирователей управляющих сигналов и элементов И первой группы и другие выходы мультиплексора. Источники информации,. принятые во внимание при экспертизе 1,Авторское свидетельство СССР If i 28ft55, кл. G 11 С 29/00, 1372. 2,Авторское свидетельство СССР № 526952, кл. G 11 С 29/00, 197 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля памяти | 1982 |

|

SU1092568A1 |

| Устройство для контроля оперативной памяти | 1981 |

|

SU957279A1 |

| Многоканальный сигнатурный анализатор | 1987 |

|

SU1529221A1 |

| Устройство для контроля цифровых узлов | 1985 |

|

SU1269139A1 |

| Устройство для контроля цифровых блоков | 1986 |

|

SU1343417A1 |

| Устройство для контроля блоков оперативной памяти | 1986 |

|

SU1358003A1 |

| Многоканальный сигнатурный анализатор | 1984 |

|

SU1262500A1 |

| Устройство для контроля интегральных схем | 1980 |

|

SU966699A1 |

| Устройство для контроля цифровых узлов | 1981 |

|

SU1013960A1 |

| Устройство для статистического контроля логических блоков | 1983 |

|

SU1173415A1 |

лгЖ ; iiM

%

Авторы

Даты

1982-12-15—Публикация

1981-02-25—Подача