пы, для регистров /п-й группы; PS раарядность регистра). где / - ЧН.СЛО знак I означае Обозначим qi

с, гJ-Ka-,

©Д If mv ©IJ

f

U

Сигнал на выходе устройства Д 0 при исПраВ Ной работе регистров, - при неисправной работе регистров.

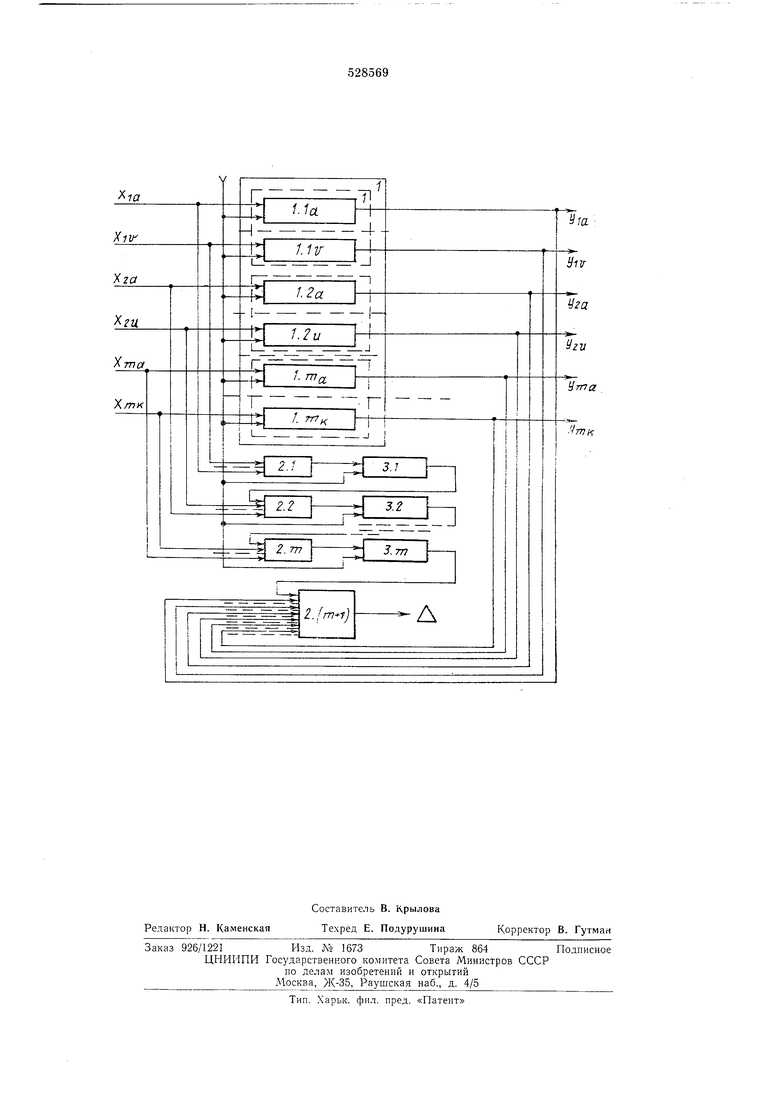

На чертелсе изображена блок-схема предлагаемого стройсгва, где все контролируемые регистры сдвига 1. 1а - l.mk обведены С плошны.м контуром. Контролируемые регистры одинаковой разрядности образуют группу .1а -l.lu, 1.2а-1.2w, l.ma - l.mfe. Все регистры являются си-нхрониыми устройства.м«. Каждый контролируемый регистр имеет И1нфор.мациопиый .вход, связанный с источником входных сигналов х,-;, и один выход, с которого снимаются выходные сигналы г/,-;.

в устройстве первый вход сумматора по модулю два 2.1 соединен с информациоиным входом контролируемого регистра 1.1 а, второй вход сумматора 2.1 соединен с ипформаЦИОТО1ЫМ 13ХОДО.М .регистра 1.1 и, и-вый вход сум.матора 2.1 соединен с «нформационным входом регистра 1.1 и. Выход сумматора 2.1 соединен с информациолпым входом контрольного регистра 3.1. Выход регистра 3.1 соединен с нервном входом сум.матэра по модулю два 2.2. Второй вход сумматора 2.2 соединен с информационным входом регистра 1.2а, («+1)-й вход сумматора 2.2 соединен с пнформациопиым .входом репстра 1.2«. Выход сумматора 2.2 соеди-нер; с информац1 о;1;1Ь.м входом контрольного регистра 3.2. Такой вид ОБязей повторяется и далее, в результате образуется целочка из чередуюш,ихся сумматоров по модулю два и контрольных регистров. Наконэц, выход регистра З.т соеди1нен с первым 1ВХОДОМ сумматора .по .модулю два 2. (т+1). ВтОрой вход сумматора 2. (т+1) соэдИИен с выходом контролируемого регистра Ма, .последний -вход су.мматора 2. {m+l соединен с выходом .регистра l.mk.

Рассмотри:, работу устройства на конкретном пр.имере. При этОМ зададиолся следующими .ис.ходаыми да.ниыми.

Структура устройства слнсызагтся выражением:

3 олопчательном

q-m iZ

Jl

.©D I ., i j-i J j

Пусть имеется три группы контролируемых регистров сдвига: два регистра l.la 1. 1в по зосе.мь разрядов, два регистра 1.2а и 1.2.S по шесть разрядов, два регистра 1.3а и 1. Зв по четыре разряда.

Устройство содержит сумматор по модулю два 2.1 ка два входа, сумматоры по модулю два 2.2 и 2.3 на три входа, сумматор по модулю два 2.4 на семь входов; контрольные регистры 3.1 и 3.2, состояш,ие из двух разрядоз, контрольный регистр 3.3, состоящий из четы-. рех разрядов.

Рассмотрим случай исправной работы регистров.

Лусть в мо.мент времени t сигналы на инфор.мационных входах регистров 1. 1а и 1. 1в имели значение: А ,,. 1, У-,- 1 соответственно. В момент /3 сигналы на информационных входах регистров 1 2а и 1 2з: , О, л4 1- В момент /5 сигналы lia информационных 1входах регистров 1 - За и 1 Зв : ,, 1, x-J; 0. Воспользовавщись формулой (I), напишем 31наче.н:ие сигналов на выходах этих регистров:

. 1, , 31:,- О, , у:;, 1, .

Будем считать, что сумматоры по модулю два работают без задерж ки.

Тогда сигнал на входе регистра 3 1 в момент /1 будет равен

Сигнал на его выходе в момент /з согласно 45 (I) раве-н

)4а pJ--J ,. а,;0э а х,,е jjjGs 2 j. - )ijJ 5F, i , ) .. ©2 .jj 03 p -Ъ®, r7,j © D ™/ ; регистров з ()-й группе,q,,i P, т су.м.м«рова ние по модулю 2.п налише.м выражение (2) Pi, q2 P2-Р, . . . , виде: jruJ ejK Д y,j©.©2 y/;r.,,©g mj© j I - jr -j Ij:I Аналогично напишем з начение входных и выходных сигналов для остальных контроль кых регнстроз .. Хгз ® © У га - , Ч ji 1 , 4NvC3aextf@:j | l®001 0 , Сигнал Д на выходе сумматора 2 4 з мо мент /9 будет равен: to -- г .-V, , - ,.-9 т i :J,,j0.i©:)-C; i sj© ::35®-Э-- -- 101©001 1® Пусть в результате сбоя в регистре 1. За сигнал на его выходе принял неправильноезна чен:ие (УЗ ,) 0, хотя сигнал на его вхо де xf 1. Тогда на выходе устройств возни:кает сигнал (Д ) равный: (,©у /©УЙеу:1©1азо)© 41 © i®ieo®i©o® о®

Таким образом, значение сигнала Д 1 на выходе устройства позволяет обнаружить этот сбой.

В предлагаемом устройстве дополнительное оборудование вводится не в отдельно взятый регистр, а в группу регистров. Это позволяет уменьшить объем дополнительного оборудования до 30% в зависимости от разрядности регистров и числа групн.

Г1сточн;гки информации, принятые во внимание при экспертизе:

1.Азт. св. ЛЬ 327481, М. Кл.ООбР 11/00,

1970г.

2.Авт. св. Лс 402067, М. Кл. G Об F 11/00, 1972 г.

3.Авт. св. Хо 383048, .М. Кл. G 06 F 11/00,

1971г. Фор :.; у л а и з о б р е т е п и я стройство для контроля т групп periicTов сдвига, содержащее сумматоры по .юдулю два, отличающееся тем. что, с целью упрощеьшя устройства в него В ведены ш контрольных рггистро.в сдвига, причем входы устройства согди:-;ены с илформацнонными входами контролируемых регистров сдвига, вхоы первого сумматора по модулю два соединены с ИНформационными входами контролируемых регистров сдвига первой грулпы, выход первого cyм iaтopa по модулю два соедииеи с первым входов.: первого контрольного регистра сдвига, выход которого соединен с первым зхэдом второго сумматора по модулю два, остальные входы второго сумматора по модулю два соединены с информационнымвходамл контролируемых регистров сдвига второй группы, выход второго сум матора по модулю два соединен с первым входом второго контрольного регистра сдвига, выход которого соединен с первым входом следующего сумматора по модулю два. остальные входы этого сумматора по модулю два соединены с информационным : входами контролируемых регистров сдвига следующей группы, выход последнего контрольного регистра соединен с первым входом последнего сумматора по модулю два, остальные входы которого соединены с выходами контролируемых peri стров сдвига, выход последнего сумматора по модулю два соединен с выходом устройства, вторые входы контрольных регистров сдвига со входом импульсов сдвига устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля информации на четность | 1985 |

|

SU1339898A1 |

| Устройство для обнаружения и исправления ошибок в непозиционном коде | 1983 |

|

SU1134941A1 |

| Устройство для контроля @ групп регистров | 1986 |

|

SU1322378A1 |

| Устройство для сдвига информации | 1984 |

|

SU1173447A1 |

| Многоканальный сигнатурный анализатор для микропроцессорной системы | 1986 |

|

SU1374226A1 |

| Сигнатурный анализатор | 1987 |

|

SU1416997A1 |

| Устройство для деления чисел на константу 2 @ + 1 | 1990 |

|

SU1746379A1 |

| Устройство для контроля генератора М-последовательностей | 1985 |

|

SU1278850A1 |

| Генератор псевдослучайных последовательностей | 1984 |

|

SU1228236A1 |

| ГЕНЕРАТОР ПСЕВДОСЛУЧАЙНЫХ ЧИСЕЛ | 2020 |

|

RU2756833C1 |

Авторы

Даты

1976-09-15—Публикация

1974-07-08—Подача