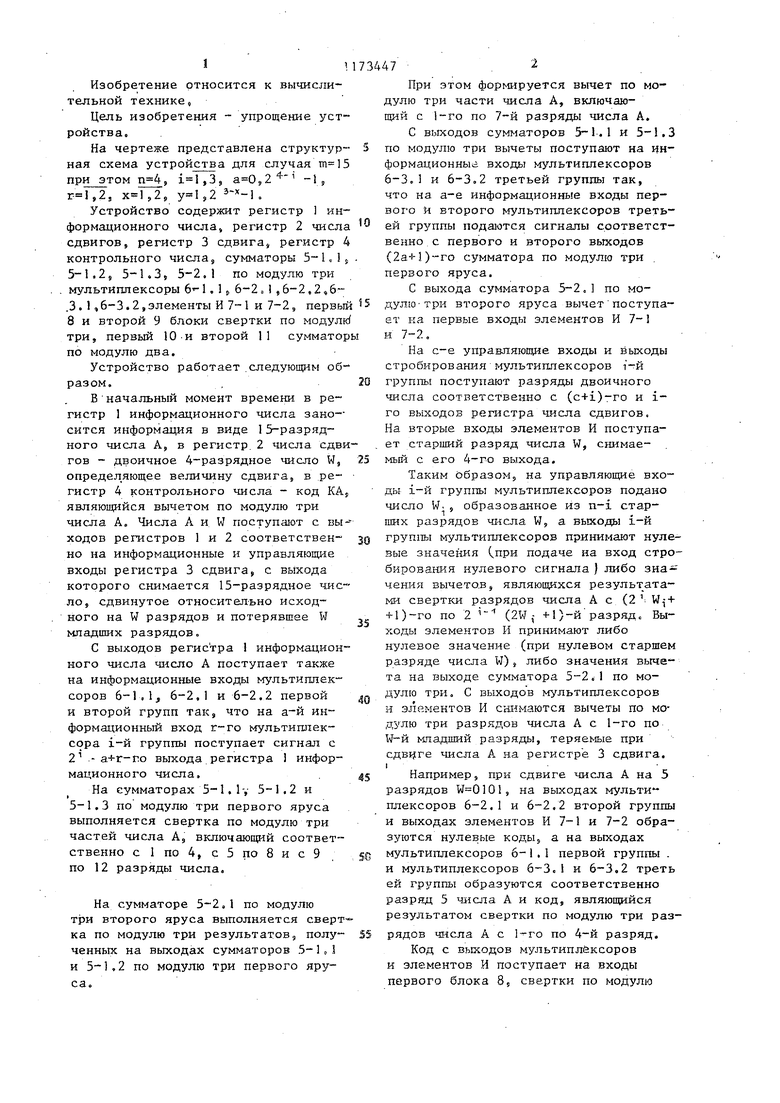

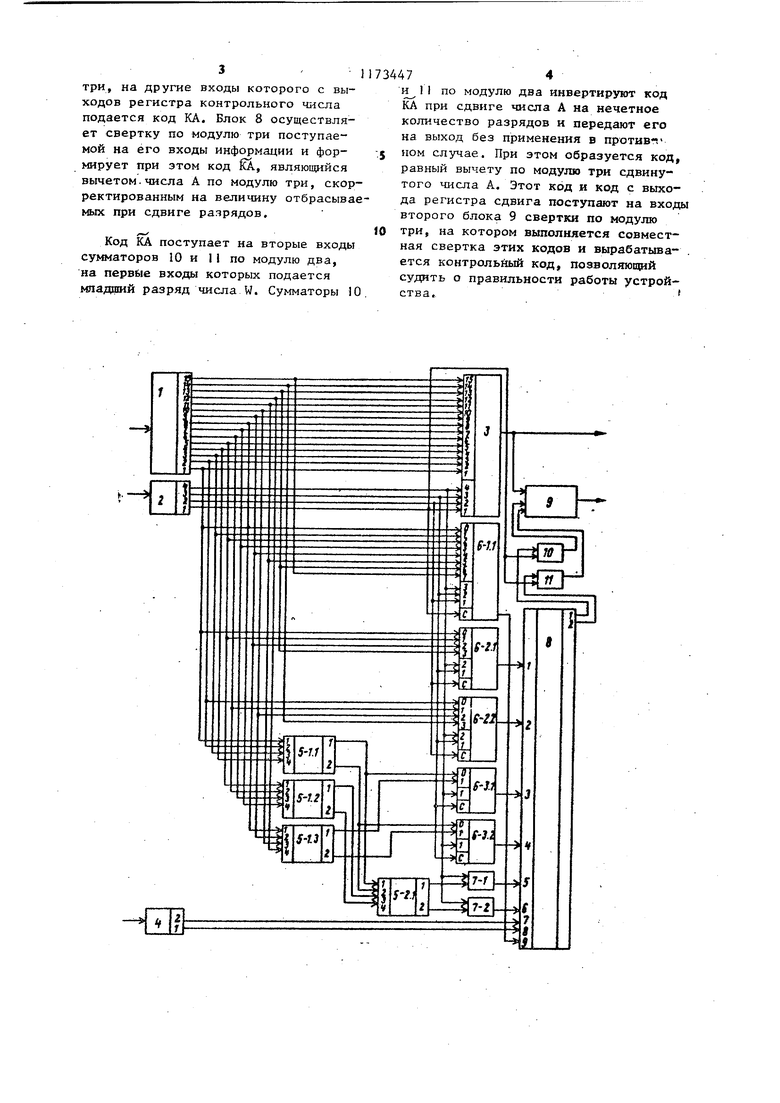

Изобретение относится к вычислительной технике, Цель изобретения упрощение уст ройства. На чертеже представлена структур ная схема устройства для случая при этом , ,3, ,2 , г. 1,2, ,2, ,2 , Устройство содержит регистр 1 ин формационного числа, регистр 2 числ сдвигов, регистр 3 сдвига, регистр контрольного числа, сумматоры 5 1.1 5-1.2, 5-1.3, 5-2.1 ПС модулю три мультиплексоры б-. 1 j, 6-2« 1 ,6-2,2,6™ .3..2,элементы И 7-1 и 7-2, первы 8 и второй 9 блоки свертки по модул три, первый 10-и второй 11 суммато по модулю два. Устройство работает .следующим об разом.. Вначальный момент времени в регистр 1 информационного числа заносится информация в виде 15-разрядного числа А, в регистр. 2 числа сдв гов - двоичное 4-разрядное число W, определ яющее величину сдвига, в регистр 4 контрольного числа - код КА являющийся вычетом по модулю три числа А, Числа А и. W поступают с вы ходов регистров 1 и 2 соответственно на информационные и управляювще входы регистра 3 сдвига, с выхода которого снимается 15-разрядное чис ло, сдвинутое относительно исходного на W разрядов и потерявшее W младших разрядов. С выходов регистра 1 информацион ного числа число А поступает также на информационные входы мультиплексоров 6-1.1, 6-2,1 и 6-2,2 первой и второй групп так, что на а-й информационный вход г-го мультиплексора i-й группы поступает сигнал с 2V-a- -r-r.o выхода регистра 1 информационного числа.. На сумматорах 5-1. 1у 5-I.2 и 5-1,3 по модулю три первого яруса выполняется свертка по модулю три частей числа А, включающий соответственно с 1 по 4, с 5 по 8 и с 9 по 12 разряды числа. На сумматоре 5-2.1 по модулю TJJH второго яруса выполняется сверт ка по модулю три результатов, полученных на выходах сумматоров 5-1„1 и 5-1.2 по модулю три первого яруса. При этом формируется вычет по модулю три части числа А, включающий с 1-го по 7-й разряды числа А. С выходов сумматоров 5-1-, 1 и 5-1,3 по модулю три вычеты поступают на информационные входы мультиплексоров 6-3.1 и 6-3.2 третьей группы так, что на а-е информационные входы первого и второго мультиппексоров третьей группы подаются сигналы с.оответственно с первого и второго выходов ()-го сумматора по модулю три первого яруса. С выхода сумматора 5-2.1 по модулю- три второго яруса вычетпоступает ка первые входы элементов И 7-1 и 7-2, На с-е управляющие входы и выходы стробирования мультиплексоров i-й группь поступают разряды двоичного числа соответственно с (c+i)-ro и iго выходов регистра числа сдвигов. На вторые входы элементов И поступает старший разряд числа W, снимаемый с его 4-го выхода. Таким образом, на управляющие входы i-й группы мультиплексоров подано число W., образованное из n-i старших разрядов числа W, а выходы i-й группы мультиплексоров принимают нулевые значения Спри подаче на вход стробирования нулевого сигнала ) либо значения вычето.в, являющихся результанта- ми свертки разрядов числа А с (2 W + + 1)-го по 2 i- (2W,- +1)-йразряд. Выходы элементов И принимают либо нулевое значение (при нулевом старшем разряде числа W), либо значения вычета на выходе сумматора по модулю три. С выходов мультиплексоров и элементов И сш- маются вычеты по модулю три разрядов числа А с 1-го по W-й младший разряды, теряемые при числа А на регистре 3 сдвига, I Например, при сдвиге числа А на 5 разрядов , на выходах мультиплексоров 6-2.1 и 6-2.2 второй группы и выходах элементов И 7-1 и 7-2 образуются нулевые коды, а на выходах мультиплексоров 6-1.1 первой группы . и мультиплексоров 6-3. и 6-3,2 треть ей группы образуются соответственно разряд 5 числа А и код, являющийся результатом свертки по модулю три разрядов числа А с 1-го по 4-й разряд, Код с выходов мультиплексоров и элементов И поступает на входы первого блока 8, свертки по модулю

3 1

три, на другие входы которого с выходов регистра контрольного числа подается код КА. Блок 8 осуществляет свертку по модулю три поступаемой на его входы информации и формирует при этом код 1(А, являющийся вычетом.числа А по модулю три, скорректированным на величину отбрасываемых при сдвиге разрядов.

Код КА поступает на вторые входы сумматоров 10 и 11 по модулю два, на первые входы которых подается младший разряд числа W. Сумматоры 10.

474

и 1 1 по модулю два инвертируют код КА при сдвиге числа А на нечетное количество разрядов и передают его на выход без применения в npoTHB-,

ном случае. При этом образуется код, равный вычету по модулю три сдвинутого числа А. Этот код и код с выхода регистра сдвига поступают на входы второго блока 9 свертки по модулю

три, на котором выполняется совместная свертка этих кодов и вырабатыва- . ется контрольйый код, позволяющий судить о правильности работы устройства,.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сдвига информации | 1983 |

|

SU1109807A1 |

| Устройство для обнаружения и исправления ошибок в непозиционном коде | 1983 |

|

SU1134941A1 |

| УСТРОЙСТВО ДЛЯ БЫСТРОГО ПРЕОБРАЗОВАНИЯ ФУРЬЕ | 1991 |

|

RU2012051C1 |

| Устройство для формирования тестовых воздействий | 1984 |

|

SU1168953A1 |

| Устройство для умножения комплексных чисел в модулярной системе счисления | 1985 |

|

SU1280625A1 |

| Устройство для умножения комплексных чисел в модулярной системе счисления | 1987 |

|

SU1587503A1 |

| Устройство для умножения чисел в модулярной системе счисления | 1986 |

|

SU1352483A1 |

| Устройство для умножения чисел в модулярной системе счисления | 1989 |

|

SU1667065A1 |

| Устройство для масштабирования чисел | 1989 |

|

SU1667066A1 |

| Устройство для умножения чисел | 1986 |

|

SU1325475A1 |

УСТРОЙСТВО ДЛЯ СДВИГА ИНФОРМАЦИИ, содержащее m-разрядный регистр информационного числа, г-разрядный регистр числа сдвигов ( п - .ближайшее целое, большее log j Pi), регистр сдвига, регистр контрольного числа, первый и второй блоки свертки по модулю три, сумматоры по модулю два, п-1 групп мультиплексоров, элементы И, причем информационные входы регистра сдвига соединены с выходами регистра информационного числа, входы которого являются первыми входами устройства, а управляющие входы регистра сдвига соединены с выходами регистра числа сдвигов, вход которого является вторым входом устройства, выход регистра сдвига ляется информационным выходом устройства, с-е управляющие входы и входы стробирования мультигшексоров 1-й группы (,,п-1, , п-1) соединены соответственно с (c+i)-M и i-M выходами регистра числа сдвигов, и-и выход которого соединен с первыми входами элементов И, а первый выход с первыми входами сумматоров по модулю два, о(-й информационный вход г-го мультиплексора первой и второй групп (, 1 т/2 , ,л ) соединен с

| Устройство для обнаружения ошибок в регистре сдвига | 1975 |

|

SU529488A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для сдвига информации | 1983 |

|

SU1109807A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1985-08-15—Публикация

1984-03-27—Подача