е-1 в-г в-з - s-s е-в s-7ft-ni

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля цифровых узлов | 1984 |

|

SU1231506A1 |

| Сигнатурный анализатор | 1986 |

|

SU1357961A1 |

| Сигнатурный анализатор | 1986 |

|

SU1472907A1 |

| Сигнатурный анализатор | 1984 |

|

SU1242957A1 |

| Сигнатурный анализатор | 1989 |

|

SU1714602A1 |

| Устройство для деления | 1988 |

|

SU1621034A1 |

| МНОГОКАНАЛЬНЫЙ СИГНАТУРНЫЙ АНАЛИЗАТОР | 1995 |

|

RU2087030C1 |

| Устройство для контроля цифровых узлов | 1983 |

|

SU1124312A1 |

| Устройство для контроля цифровых блоков | 1987 |

|

SU1587515A1 |

| Параллельный сигнатурный анализатор | 1986 |

|

SU1451696A1 |

Изобретение относится к вычислительной технике и может быть использовано в контрольно-диагностической аппаратуре для контроля функционирования и локализации неисправностей цифровых устройств. Целью изобретения является повышение быстродействия анализатора. Сигнатурный анализатор содержит п-разрядный регистр 1, блок 2 задания режима, п мультиплексоров . 3, m сумматоров по модулю два 4(т n-k - максимальное число информационных входов анализатора, а п и k являются показателями степени в образующем примитивном полиноме Р(х)х +х +1), Обработка входных j-разрядных кодов в сигнатурном анализаторе ( - выбранное на блоке задания режима число исцоль- зуемых информационных входов анализатора) осуществляется путем формирования и записи в п-разрядный регистр состояния, которое имел бы однока- нальньш анализатор через J тактов от текущего состояния, в течение которых в него записывалась последовательность из j бит. 1 ил. с (Л

О)

со со

Изобретение относится к вычисли- Teju.Hot i технике и может быть исполь- для контроля функционирования и диагностирования неисправносте1{ ци ровых устройств.

: Цель изобретения - повышение бы- :стродействия сигнатурного анализатора .

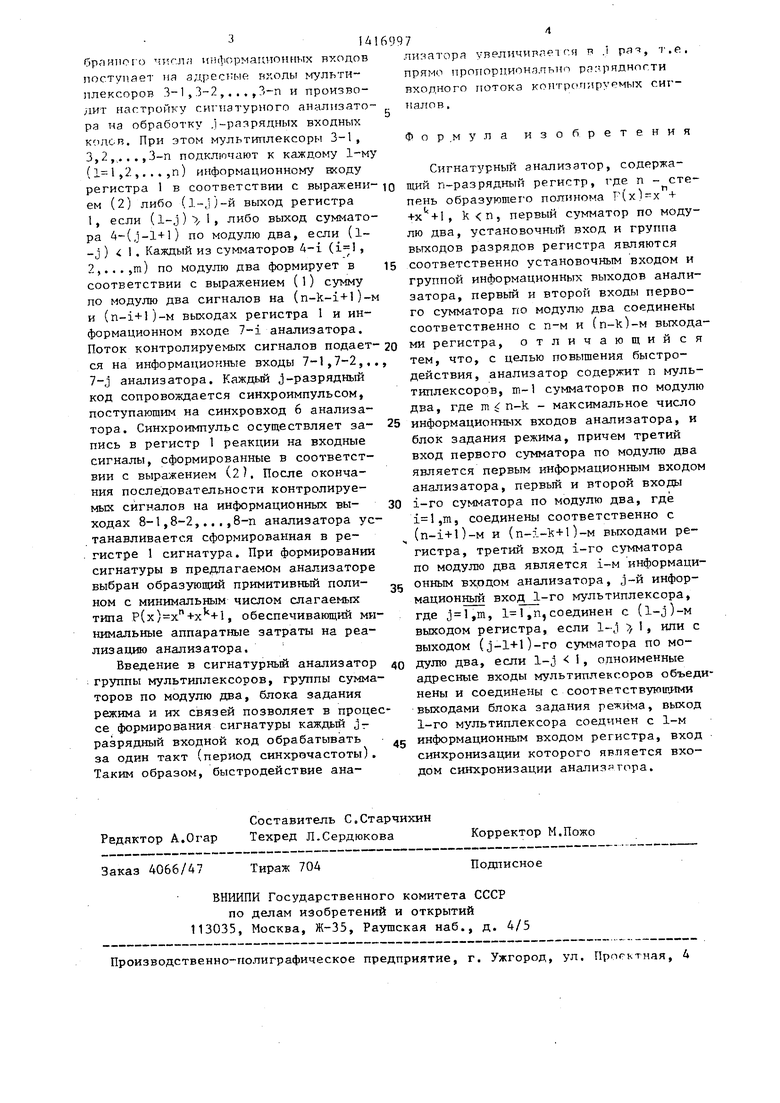

На чертеже изображена функциональ ная схема сигнатурного анализатора, : Сигнатурный анализатор содержит |п-разрядный регистр 1, блок 2 зада- :ния режима, мультиплексоры 3-1,3-2,, 3-п, сумматоры 4-1,4-2,...,4-т по мо дулю два ( - максимальное число информационных входов анализатора) , ;установочньш вход 5, синхровход 6, :информационные входы 7-1,7-2,t..,7-m ;и информационные выходы 8-1,8-2,.,, 8-п. На чертеже представлена функциональная схема сигнатурного анализатора при , , и образующем полиноме Р(х).

Блок 2 задания режима может быть реализован на переключателях 9-1, 9-2,..,,9-р, где p7/logjm (в данном случае ). Первые и вторые контакты переключателей 9-1,9-2,...,9-р соединены соответственно с шинами О и 1,а третьи контакты являются выходами блока 2 задания режима.

Другим примером реализации блока задания режима 2 может служить р-раз- рядный регистр, в который перед нача- лом работы сигнатурного анализатора записывается код числа используемых информационных входов.

Анализатор работает следующим образом.

Рассмотрим работу одноканального сигнатурного анализатора, реализованного на базе регистра сдвига с сумматором по модулю два в обратной связи Пусть Р(х) - образующий при- митивный полином, описывающий работу сигнатурного анализатора; а„, где ,2,...,п, состояние 1-го разряда регистра сигнатурного анализатора на t-M такте работы; Ъ - сигнал на информационном входе сигнатурного анализатора на t-M такте; ® - операция суммирования по модулю два. Тогда процесс формирования сигнатуры в од- ноканальном анализаторе математическ может быть описан с помощью рекуррентного алгоритма ai aj,. ,

аТ -a ,,,...ar , где t

последовательно принимает значения 0,1,2,..,, (d - ;у1ина входной последовательности контролируемых сигналов). При ;i%a5,.,.,a° - исходное состояние, в которое устанавливается регистр сигнатурного анализатора перед началом работы. При t,d а ,a.,j, , ., ,а - сформированная в регистре анализатора сигнатура. Пусть с ,c,j ,., ,с J - параллельный j-разряд- ный входной поток контролируемых сигналов, поступающей на информационные вхеды предлагаемого сигнатурного анализатора. Здесь И,, где - максимальное число информационных входов предлагаемого сигнатурного анализатора. Представим входной параллельный код с ,c,j,. .. ,с как входную последовательность одноканального сигнатурного анализатора: с , Ъ 02,..,Ъ. -С:, Определим

состояния всех разрядов регистра этого анализатора после тактов работы, в течение которых осушествляется фиксация в анализаторе входной последо- -,t + 2

вательности Ъ , Ъ ,..,,Ъ . Очевидно, что

ae-j , если 1-j 1 , .4

е 1 t+i-f+1

.а V , если l-j 1

t -j-E-n -ut + i-F+1 a/ а„.( © a J ® Ъ

3-U-j+e®

- t t .

Обозначим , ,4i © a,.; © c,- ,

где ,2,... ,m. Тогда

t+j Г a( : , если 1-j 1 г I S.. . , если 1-3

5

5

| i-i

Таким образом, чтобы зафиксировать за один такт в сигнатурном анализаторе j-разрядный параллельный входной код, в каждый 1-й разряд п-разрядного регистра анализатора необходимо записать состояние, определенное соотношением (2) .

Работа сигнатурного анализатора начинается с установки в исходное, например, нулевое состояние регистра 1 путем подачи импульса на установочный вход 5. Затем с помощью переключателей 9-1,9-2,...,9-р блока 2 задания режима осуществляется выбор необходимого числа ,-(И,тп) информационных входов анализатор:,. Двоичный код выбранноI o числя информационных входов поступает на адресные мультиплексоров 3-1,3-2,..,,3-п и производит настройку сигнатурного анализатора на обработку л-разрядных входных кодог. При этом мультиплексоры 3-1 , 3,2,...,3-п подключают к каждому 1-му (1- 1,2 ,...,п) информационному входу регистра 1 в соответствии с выражением (2) либо (1-,))-й выход регистра 1, если (l-j)l, либо выход сумматора 4-(,-1+1) по модулю два, если (l- -j ) i 1 . Каждый из сумматоров A-i ( 2,...,га) по модулю два формирует в соответствии с выражением (l) сумму по модулю два сигналов на (n-k-i+l)-M и (n-i+l)-M выходах регистра 1 и информационном входе 7-i анализатора.

Поток контролируемых сигналов подает- 20 ми регистра, отличающийся

ся на информационные входы 7-1,7-2,, 7-, анализатора. Каждый j-разрядный код сопровождается синхроимпульсом, поступающим на синхровхсд 6 анализатора. Синхроимпульс осуществляет запись в регистр 1 реакции на входные сигналы, сформированные в соответствии с выражением (2). После окончания последовательности контролируемых сигналов на информационных выходах 8-1,8-2,...,8-п анализатора устанавливается сформированная в регистре 1 сигнатура. При формировании сигнатуры в предлагаемом анализаторе выбран образующий примитивный полином с минимальным числом слагаемых типа Р(х)х +х +1, обеспечивающий минимальные аппаратные затраты на реализацию анализатора.

Введение в сигнатурньш анализатор группы мультиплексоров, группы сумматоров по модулю два, блока задания режима и их связей позволяет в процесе формирования сигнатуры каждый j- разрядный входной код обрабатывать за один такт (период синхргачастоты). Таким образом, быстродействие ана

лнзатора увеличияпеч гя в .i ра, т.е. прямо пропорционально ра:-рядног.ти входного потока контролируемых сиг- TiaJioB,

Фор.мула изобретения

Сигнатурный анализатор, содержащий п-разрядный регистр, где п - степень образующего полинома Р(х)-х + +х + 1 , первый сумматор по модулю два, установочный вход и группа выходов разрядов регистра являются соответственно установочным входом и группой информационных выходов анализатора, первый и второй входы первого сумматора по модулю два соединены соответственно с п-м и (n-k)-M выхода5

0

g

тем, что, с целью повышения быстродействия, анализатор содержит п мультиплексоров, т-1 сумматоров по модулю два, где - максимальное число информационных входов анализатора, и блок задания режима, причем третий вход первого сумматора по модулю два является первым информационным входом анализатора, первый и второй входы i-ro сумматора по модулю два, где ,т, соединены соответственно с (n-i+l)-M и ( )-м выходами регистра, третий вход i-ro сумматора по модулю два является i-м информаци- 5 онным вх,одом анализатора, j-й инфор- мационный вход 1-го мультиплексора, где ,п, со единен с (l-j)-M выходом регистра, если 1-j / 1, или с выходом (j-l+l)-ro сумматора по модулю два, если 1-j 1, одноименные адресные входы мультиплексоров объединены и соединены с соответствующ -гми выходами блока задания режима, выход 1-го мультиплексора соединен с 1-м информационным входом регистра, вход синхронизации которого является входом синхронизации анализатора.

0

| Сигнатурный анализатор | 1984 |

|

SU1238074A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Сигнатурный анализатор | 1983 |

|

SU1180896A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-08-15—Публикация

1987-02-02—Подача