00

4 1C Ю

05

Изобретение относится к цифровой вычислительной технике и может быть использовано в составе микропроцессорной системы для контроля и диаг- ностики сложных цифровых устройств.

Целью изобретения является упрощение конструкции.

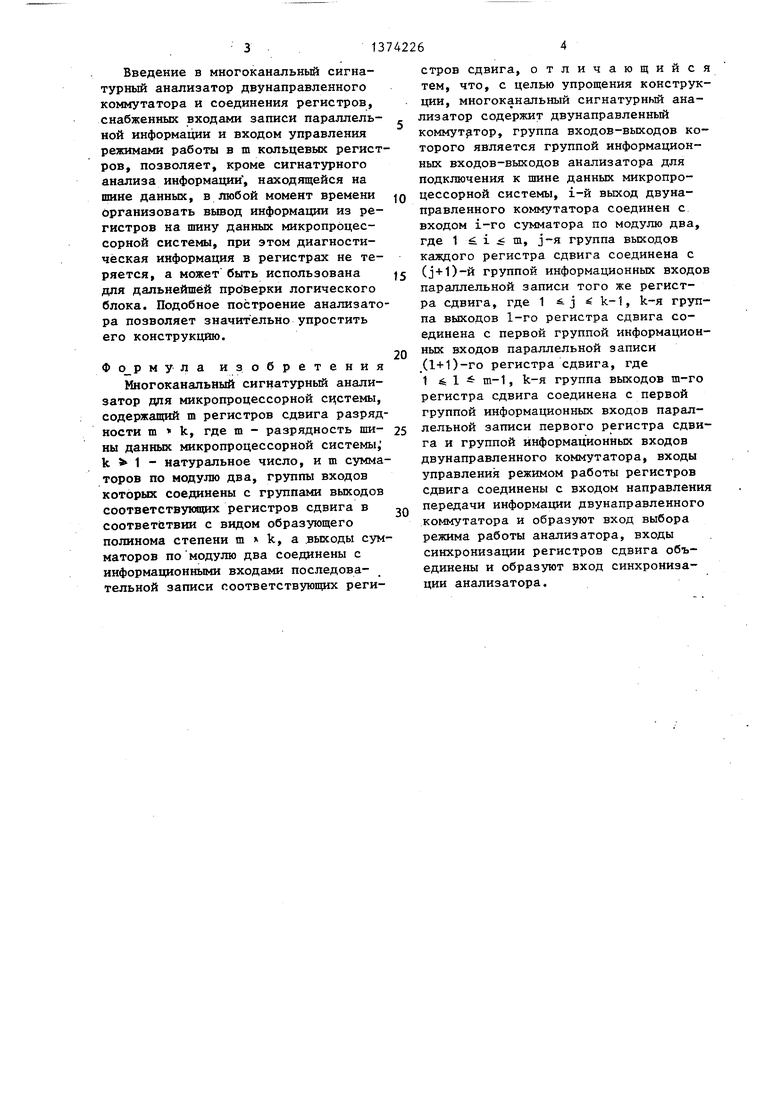

На чертеже изображена функциональная схема восьмиканального сигнатур- ного анализатора с шестнадцатиразрядными регистрами сдвига (т 8, k 2

Восьмиканальный сигнатурньШ анализатор для микропроцессорной системы содержит восьмиразрядный двуйаправ- ленный коммутатор 1, восемь шестнадцатиразрядных регистров 2.1-2.8 сдвига, восемь сумматоров 3.1-3.8 по модулю два, вход 4 начальной установки анализатора, вход 5 синхронизации, вход 6 выбора режима работы анализатора, вход 7 выбора, пшну 8 данных.

Работа анализатора возможна в двух режимах. Первьй режим - режим сигнатурного анализа информации с шины данных путем получения остатка от деления информационной последовательности на многочлен х + х + х 4 + х + 1, функцию которого выполняет регистр сдвига с обратными связями. Второй режим - режим вьщачи результатов сигнатурного анализа на шину данньк микропроцессорной системы.

Уровень 1, поступающий на вход 6 выбора режима работы анализатора, определяет работу регистров 2.1-2.8 в режиме сдвига, а коммутатор 1 передает информацию с шины данньк в микропроцессорной системе через дву- направленные входы-выходы DB1-DB8 на входы D01-D08, соединенные с входами сумматоров 3.1-3.8 по модулю два. Информационные сигналы с шины 8 данных, переданных через коммутатор 1, складываясь с сигналами обратных связей в сумматорах 3.1-3.8, поступают на последовательные информационные входы регистров 2.1-2.8 сдвига. По переднему фронту импульса синхро- низации, поступающего на вход 5 анализатора, происходит сдвиг информации в регистрах 2.1-2.8 сдвига на один разряд вправо и запись информации с выходов сумматоров 3.1-3.8 по модулю два в первые разряды регистров 2.1-2.8. Таким образом, информация с каждого разряда шины 8 данных микропроцессорной системы сворачивается в соответствующем регистре в шестнадцатиразрядный код - сигнатуру

Режим вывода диагностической информации из регистров анализатора устанавливается уровнем О по входу 6. Коммутатор 1 при этом передает информацию с входов DI1-DI8, подключенных к старшим восьми разрядам регистра 2.8, через двунаправленные входы-выходы DB1-DB8Ha шину 8 данных микропроцессорной системы, а регистры 2.1-2.8 сдвига переводятся в режим записи параллельной информации.

В первом такте работы анализатора в режиме вьгоода информации на шину данньк поступает информация со старших восьми разрядов регистра 2.8. Затем эта информация одновременно записывается через входы записи параллельной информации в младшие восемь разрядов регистра 2.1. Информация, хранимая в этих разрядах регистра 2.1 до процесса вьшода по переднему фронту первого тактового импульса, переписывается в старшие восемь разрядов регистра 2.1. Содержимое млйдших восьми разрядов регистров 2.1-2.8 переписьтается в каждом такте в старшие разряды регистров 2.1- 2.8, а содержимое старших разрядов регистров 2.1-2.8 переписьгаается в младшие разряды регистров 2.2-2. 8,

2.1 соответственно. Таким образом, информация из регистров при вьгооде на шину данных не теряется, а байт за байтом переписывается в регистрах. За шестнадцать тактовых импульсов вся информация из регистров 2.1-2.8 певедается на шину 8 данных микропроцессорной системы, а содержимое регистров 2.1-2.8 остается таким же, что и до процесса вьщачи информации на шину данных. После вьзда- чи диагностической информации в микропроцессорную систему устройс во может продолжить сигнатурный анализ информации с шины 8 данных микропроцессорной системы, причем начальное состояние регистров 2.1-2.8 может быть нулевым, оно устанавливается уровнем О на входе 4 анализатора или, если это необходимо, сигнатурный анализ продолжается с того состояния регистров 2.1-2.8, в котором они находились после свертки результатов реакций проверяемого блока на предыдущую испытательную последовательность.

Введение в многоканальный сигнатурный анализатор двунаправленного коммутатора и соединения регистров, снабженных входами записи параллельной информации и входом управления режимами работы в m кольцевых регистров, позволяет, кроме сигнатурного анализа информации , находящейся на шине данных, в любой момент времени организовать вывод информации из регистров на шину данных микропроцессорной системы, при этом диагностическая информация в регистрах не теряется, а может быть использована для дальнейшей прЬверки логического блока. Подобное построение анализатора позволяет значительно упростить его конструкцию.

Фо рмула изобретения

Многоканальный сигнатурный анализатор для микропроцессорной системы, содержащий m регистров сдвига разрядности m k, где m - разрядность ши- ны данных микропроцессорной системы, k 1 - натуральное число, и m сумматоров по модулю два, группы входов которых соединены с группами выходов соответствующих регистров сдвига в соответствии с видом образующего полинома степени m k, а .выходы сумматоров по модулю два соединены с информационными входами последовательной записи соответствующих регистров сдвига, отличающийс тем, что, с целью упрощения конструкции, многоканальный сигнатурный анализатор содержит двунаправленный коммутатор, группа входов-выходов которого является группой информационных входов-выходов анализатора для подключения к шине данных микропроцессорной системы, i-й выход двунаправленного коммутатора соединен с входом i-ro сумматора по модулю два, где 1 ё. i i т, j-я группа выходов каждого регистра сдвига соединена с (3+1)-й группой информационных входов параллельной записи того же регистра сдвига, где 1 j k-1, k-я группа выходов 1-го регистра сдвига соединена с первой группой информационных входов параллельной записи (1+1)-го регистра сдвига, где 1 6: 1 т-1, k-я группа выходов т-го регистра сдвига соединена с первой группой информационных входов параллельной записи первого регистра сдвига и группой информационньк входов двунаправленного коммутатора, входы управления режимом работы регистров сдвига соединены с входом направления передачи информации двунаправленного коммутатора и образуют вход выбора режима работы анализатора, входы синхронизации регистров сдвига объединены и образуют вход синхронизации анализатора.

vj- W:

a

Sj|oo|Tta gSg gg

I I I I I I

V

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обработки информации | 1981 |

|

SU993262A1 |

| Сигнатурный анализатор | 1984 |

|

SU1179341A1 |

| Параллельный сигнатурный анализатор | 1986 |

|

SU1451696A1 |

| Устройство для параллельного формирования адресов | 1990 |

|

SU1734097A1 |

| Устройство для умножения | 1985 |

|

SU1309019A1 |

| Сигнатурный анализатор | 1987 |

|

SU1427370A1 |

| Устройство для стохастического контроля микропроцессорных цифровых блоков | 1990 |

|

SU1725222A1 |

| Устройство для контроля логических блоков | 1982 |

|

SU1105897A1 |

| Сигнатурный анализатор с перестраиваемой стуктурой | 1986 |

|

SU1336009A1 |

| Автоматизированная система тестового контроля и диагностирования цифровых микропроцессорных блоков | 1989 |

|

SU1705782A1 |

Изобретение относится к цифровой вычислительной технике и может быть использовано в составе микропроцессорной системы для контроля и диагностики сложных цифровых устройств. Целью изобретения является упрощение конструкции. Анализатор содержит двунаправленный коммутатор, m регистров сдвига разрядности m k, где m - разрядность пшны-данных микропроцессорной системы; k 1 - натуральное .число, m сумматоров по модулю два. Данный анализатор обеспечивает контроль информационной последовательности на пгане данных, передает в произвольный момент времени диагностическую информацию на шину данных микропроцессорной системы с последующим продолжением сигнатурного анализа информационной последовательности. 1 ил. (Л

ВНИИПИ Заказ 603/45 Тираж 704

Произв.-полигр. пр-тие, г. Ужгород, ул. Проектная, 4

Подписное

| Устройство для контроля многовыходных цифровых узлов | 1984 |

|

SU1176333A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Авторское свидетельство СССР № 1146677, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-02-15—Публикация

1986-06-02—Подача