(54) ФАЗОВЫЙ ДИСКРИМИНАТОР

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь перемещения в код | 1980 |

|

SU875419A1 |

| ФАЗОВЫЙ ДИСКРИМИНАТОР | 2013 |

|

RU2541899C1 |

| УСТРОЙСТВО КОНТРОЛЯ СИНХРОНИЗМА КОЛЬЦА ФАЗОВОЙ АВТОПОДСТРОЙКИ ЧАСТОТЫ | 1993 |

|

RU2057395C1 |

| УСТРОЙСТВО ФАЗОВОЙ АВТОПОДСТРОЙКИ ЧАСТОТЫ | 2014 |

|

RU2565526C1 |

| Фазовый дискриминатор | 1984 |

|

SU1376229A1 |

| Дискретное фазозадающее устройство | 1981 |

|

SU1010573A1 |

| Фазовый дискриминатор | 1987 |

|

SU1469540A1 |

| Устройство для измерения скорости вращения вала | 1986 |

|

SU1315904A1 |

| Стробируемый формирователь с парафазными ттл-выходами | 1978 |

|

SU758502A1 |

| Устройство для синхронизации фаздВуХ гЕНЕРАТОРОВ | 1978 |

|

SU819975A1 |

Изобретение относится к импульсной технике.

Известен фазовый дискриминатор, содержащий дискриминатор цифрового управляющего сигнала, генератор пилообразного напряжения, блок выборки и блок памяти сигнала 1.

Такой I дискриминатор не обеспечивает достаточной точности дискриминации сигналов.

Известен также фазовый дискриминатор, содержащий две контролирующие цепи, состоящие из делителя частоты, фазового дискриминатора, дифференциального интегратора, при этом фазовый дискриминатор состоит из бистабильного триггера, образованного перекрестно соединенными вентилями, делитель частоты также состоит из триггеров Г2. Однако этот дискриминатор имеет сложную схему.

Наиболее близким по технической сущности к предлагаемому является фазовый дискриминатор, содержащий триггер RS типа, выполненный на двух многовходньсх логических элементах И-НЕ, одни входы

которых соединены между собой и подключены к источнику опорного сигнала, вторые входы перекрестно соединены с выходами логических элементов И-НЕ, а третьи их

входы соединены с вьсходами двухаходовьгх элементов И-НЕ, входы которых подключены соответственно к выходам многовходовых логических элементов И-НЕ З Такой дискриминатор имеет относительно большую зону нечувствительности.

Цель изобретения - уменьщение зоны нечувствительности.

Это достигается тем, что в предлагаемьй фазовый дискриминатор введен дифференциальный формирователь сигнала с парафазным вьсходом, выполненный, например, в ьиде противофазно последовательно средименных оптоэлектронньос з-шментов, вход; которого соединен с источником исследуемого сигнала, а выходы соединены с вторыми входами соответствук 1Ц1СХ двух входов ых, логическ1сх элементов tf-ilG.

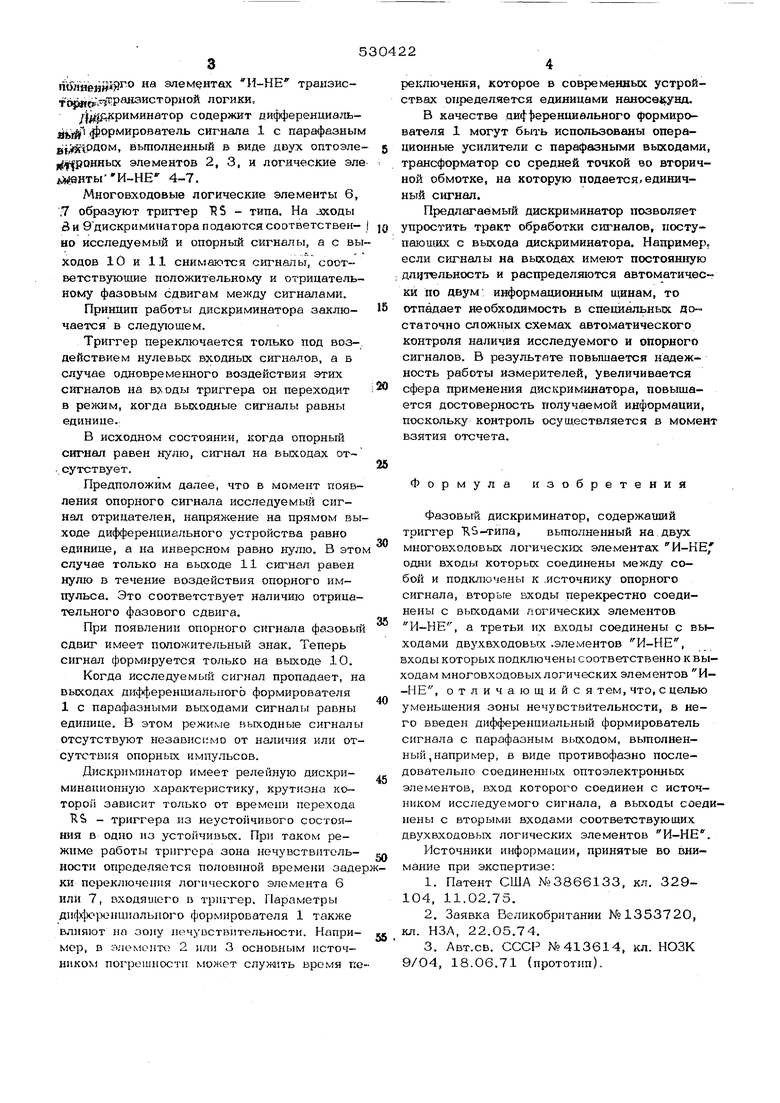

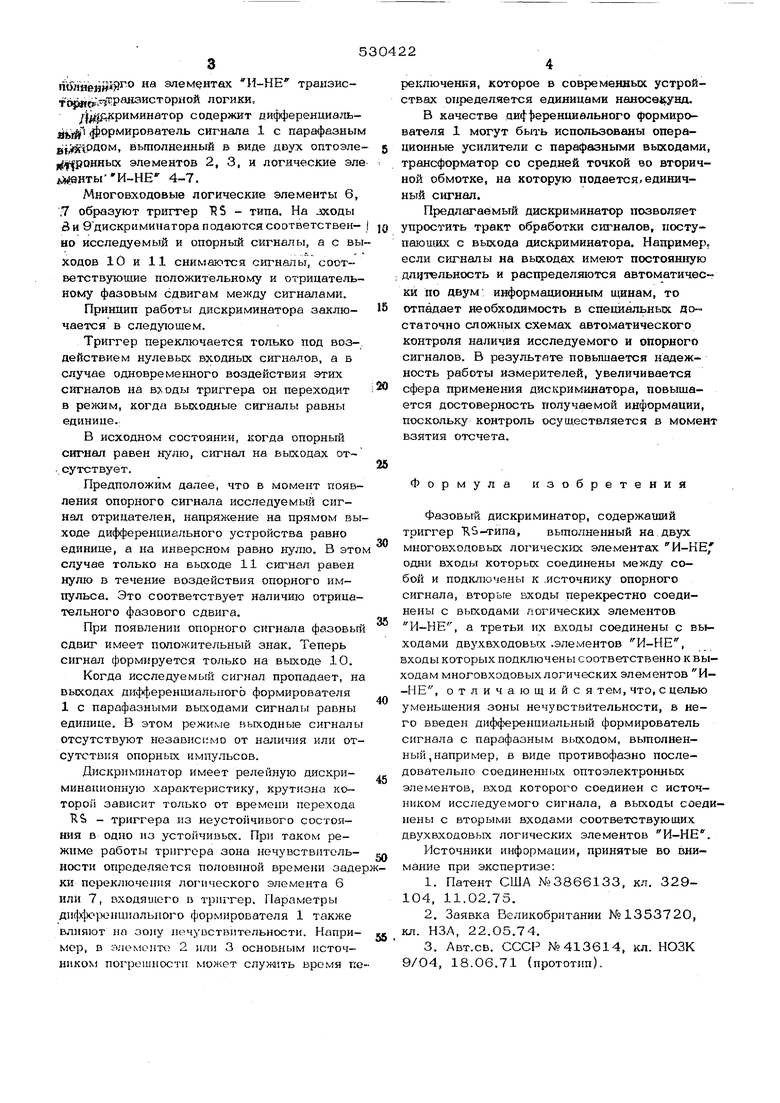

На чертеже приведена структурная апектрическая схема фазового дискриминатора, выйшшенШ на И-НЕ транэисf j«3jj|j;jr3TpaH3HCTDpHoft логики, /||)р риминатор содержит дифференииальj j,i (формирователь сигнала 1 с парафаэны , выполненный в виде двух оптоэле j y pOHHbDc элементов 2, 3, и логические эл дМ9Нты И-НЕ 4-7. Многовходовые логические элементы 6, ,7 образуют триггер TRS - типа. На зходы и и 9дискриминатора подаются соответствен- но исследуемый и опорный сигналы, а с вы ходов 10 и 11 снимаются сигналы, соответствующие положительному и отрицатель ному фазовым сдвигам мехеду сигналами. Принцип работы дискриминатора заключается в следующем. Триггер переключается только под воздействием нулевых входных сигналов, а в случае одновременного воздействия этих сигналов на взводы триггера он переходит в реншм, когда выходные сигналы равны единице. В исходном состоянии, когда опорный сигнал равен нулю, сигнал на выходах от., сутствует. Предположим далее, что в момент появ ления опорного сигнала исследуемый сигнал отрицателен, напряжение на прямом вы ходе дифференциального устройства равно единице, а на инверсном равно нулю. В это случае только на выходе 11 сигнал равен нулю в течение воздействия опорного импульса. Это соответствует наличию отрицательного фазового сдвига. При появлении опорного сигнала фазовьШ сдвиг имеет положительный знак. Теперь сигнал формируется только на выходе 10. Когда исследуемый сигнал пропадает, н выходах дифференциального формирователя 1 с парафазными выходами сигналы равны единице. В этом режиме Р4ыходные сигналы отсутствуют независимо от наличия или от сутствия опорньпс импульсов. Дискриминатор имеет релейную дискриминационную характеристику, крутизна которой зависит только от времени перехода TlSi - триггера из неустойчивого состояш я в одно из устойчивьсх. При таком режиме работы триггера зона нечувствитольности определяется половиной времени заде ки переключения логического элемента 6 или 7, входящего в триггер. Параметры ди4)4кч.оициалы1ого формирователя 1 также влияют на нечувствительности. Напримор. в элемоит11 2 или 3 основным источHHKONi погрешности может время п реключенкя, которое в современных устройствах определяется единицами наносекунд. В качестве дифференциального формирователя 1 могут быть использованы операционные усилители с парафазньгми выходами, трансформатор со средней точкой во вторичной обмотке, на которую подается, единичный сигнал. Предлагаемый дискриминатор позволяет упростить тракт обработки сигналов, поступающих с выхода дискриминатора. Например, если сигналы на выходах имеют постоянную дл1}тельность и распределяются автоматически по двум информационным щинам, то отпадает необходимость в специальных достаточно сложных схемах автоматического контроля наличия исследуемого и опорного сигналов. В результате повышается надежность работы измерителей, увеличивается сфера применения дискриминатора, повышается достоверность получаемой информации, поскольку контроль осуществляется в момент взятия отсчета. Формула изобретения Фазовый дискриминатор, содержаишй триггер Кй-типа, выполненный на двух многовходовых логических элементах И-НЕ одни входы которых соединены между собой и подключены к .источнику опорного сигнала, вторые входы перекрестно соединены с выходами логических элементов И-НЕ, а третьи их входы соединены с выходами двухвходовьгх .элементов И-НЕ, входы которых подключены соответственно к выходам многовходовых логических элементов И- -НЕ, отличающийся тем, что, с целью уменьщения зоны нечувствительности, в него введен дифференциальный формирователь сигнала с парафазным В1 1ходом, вьтолненный,например, в виде противофазно последовательно соединенных, оптоэлектронных элементов, вход которого соединен с источником исследуемого сигнала, а выходы соединены с вторыми входами соответствующих двухвходовых логических элементов И-НЕ. Источники информации, принятые во внимание при экспертизе: 1.Патент США №3866133, кл. 329104, 11.02.75. 2.Заявка Великобритании №1353720, кл. НЗЛ, 22.О5.74. 3.Авт.св. СССР №413614, кл. НОЗК 9/04, 18.06.71 (прототип).

Авторы

Даты

1976-09-30—Публикация

1975-09-15—Подача