1

Изобретение относится к импульсной технике и может быть использовано при разработке вычислительных устройств.

Известен двоичный счетчик импульсов для циклических преобразователей, содержащий счетные ячейки-триггеры, соединенные последовательно, разбитые на декады, центральный блок управления, электронный селектор, с помощью которого блок управления соединяется с триггерами соответствующей декады, буферный регистр с запоминающим устройством и логические элементы. Счетчик позволяет осуществлять ускоренный перенос сигнала между триггерами соответствующих декад, однако он конструктивно сложен.

Известен также счетчик импульсов, состоящий из последовательно включенных триггеров, разделенных на группы младших и старших разрядов, блока сквозного переноса сигналов старших разрядов, состоящего из многовходовых логических элементов «И, входы каждого из которых подключены соответственно к выходам предыдущих триггеров, а ВЫХОДЫ - к входу последующего триггера, и логических элементов «ИЛИ, образующих системы СВЯЗИ между триггерами счетчика. Такой счетчик имеет недостаточное быстродействие.

Цель изобретения - повышение быстродействия.

Это достигается тем, что в предлагаемый ДВОИЧНЫЙ счетчик импульсов введен блок формирования сигналов младших разрядов счетчика, состоящий из логических элементов «И, попарно подключенных к входам логических элементов «ИЛИ, и инверторов, входы которых соединены с выходами триггеров соответствующих младших разрядов счетчика, а ВЫХОДЫ - с входами соответствующих логических элементов «И блока формирования сигналов младших разрядов счетчика, причем остальные входы логических элементов «И блока формирования сигналов младших разрядов счетчика соединены с выходами соответствующих триггеров младших разрядов счетчика. При этом к входам каждого из триггеров младших разрядов подключены попарно двухвходовые логические элементы «И, ВХОДЫ которых соединены с соответствующими выходами предыдущих триггеров и входом счетчика.

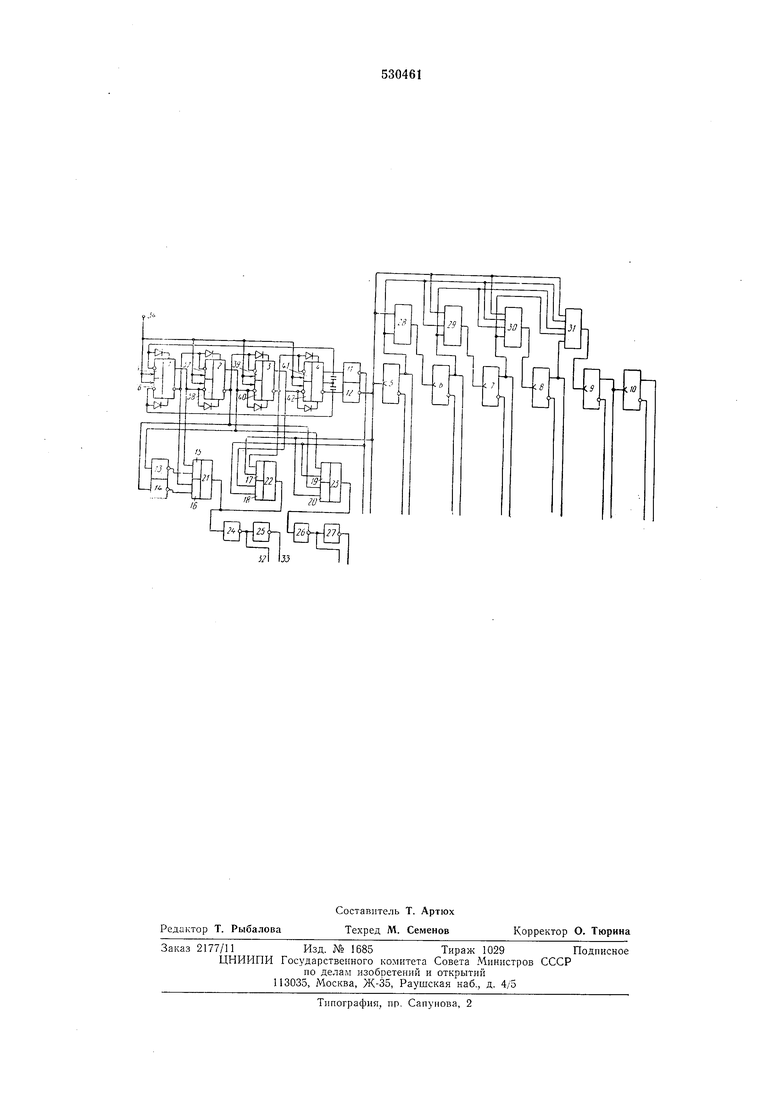

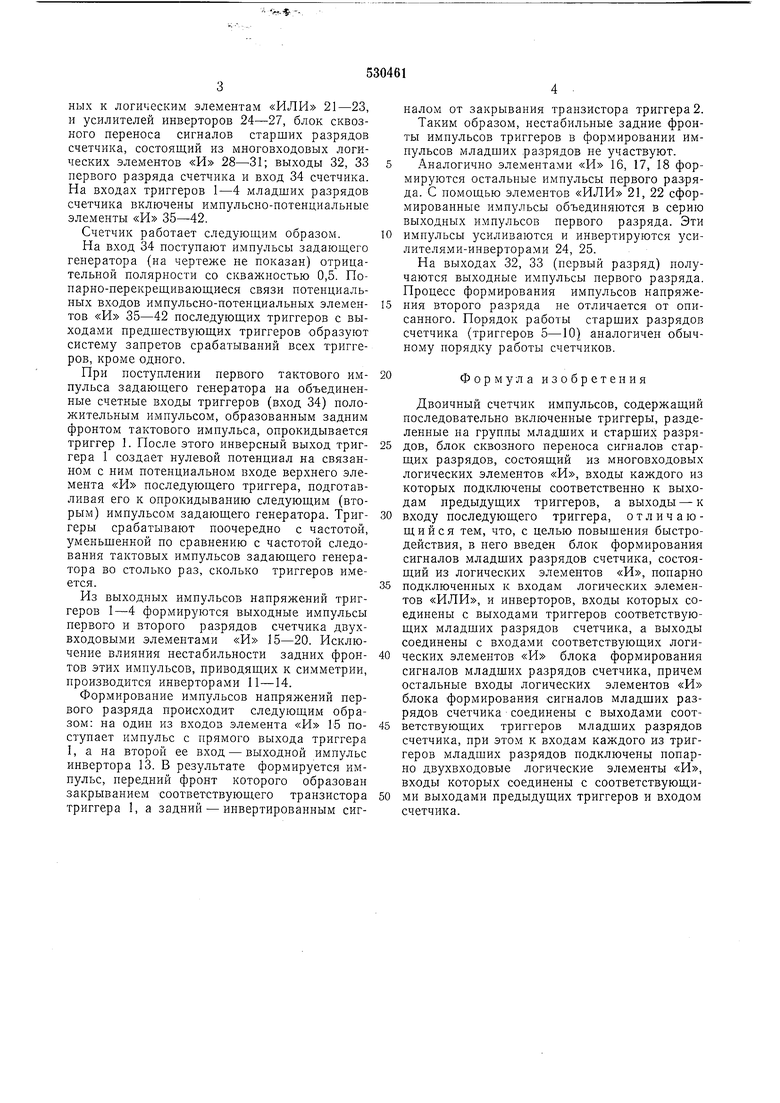

На чертеже показана структурная электрическая схема счетчика.

Счетчик содержит триггеры 1 -10 (триггеры 1-4 ЯВЛЯЮТСЯ триггерами младших разрядов, а триггеры 5-10 - триггерами старщих разрядов), блок формирования сигналов младших разрядов счетчика, состоящий из инверторов 11 -14, двухвходовых логических элементов «И 15-20. попарно подключенных к логическим элементам «ИЛИ 21-23, и усилителей инверторов 24-27, блок сквозного переноса сигналов старших разрядов счетчика, состоящий из многовходовых логических элементов «И 28-31; выходы 32, 33 первого разряда счетчика и вход 34 счетчика. На входах триггеров 1-4 младших разрядов счетчика включены импульсно-потенциальные элементы «И 35-42.

Счетчик работает следуюш,им образом.

На вход 34 поступают импульсы задаюш,его генератора {на чертеже не показан) отрицательной полярности со скважностью 0,5. Попарно-перекрешиваюш,иеся связи потенциальных входов импульсно-потенциальных элементов «И 35-42 последующих триггеров с выходами предшествующих триггеров образуют систему запретов срабатываний всех триггеров, кроме одного.

При поступлении первого тактового импульса задающего генератора на объединенные счетные входы триггеров (вход 34) положительным импульсом, образованным задним фронтом тактового импульса, опрокидывается триггер 1. После этого инверсный выход триггера 1 создает нулевой потенциал на связанном с ним потенциальном входе верхнего элемента «И последующего триггера, подготавливая его к опрокидыванию следующим (вторым) импульсом задающего генератора. Триггеры срабатывают поочередно с частотой, уменьшенной по сравнению с частотой следования тактовых импульсов задающего генератора во столько раз, сколько триггеров имеется.

Из выходных импульсов напряжений триггеров 1-4 формируются выходные импульсы первого и второго разрядов счетчика двухвходовыми элементами «И 15-20. Исключение влияния нестабильности задних фронтов этих импульсов, приводящих к симметрии, производится инверторами 11-14.

Формирование импульсов напряжений первого разряда происходит следующим образом: на один из входов элемента «И 15 поступает импульс с прямого выхода триггера 1, а на второй ее вход - выходной импульс инвертора 13. В результате формируется импульс, передний фронт которого образован закрыванием соответствующего транзистора триггера 1, а задний - инвертированным сигналом от закрывания транзистора триггера 2. Таким образом, нестабильные задние фронты импульсов триггеров в формировании импульсов младших разрядов не участвуют.

Аналогично элементами «И 16, 17, 18 формируются остальные импульсы первого разряда. С помощью элементов «ИЛИ 21, 22 сформированные импульсы объединяются в серию выходных импульсов первого разряда. Эти

импульсы усиливаются и инвертируются усилителями-инверторами 24, 25.

На выходах 32, 33 (первый разряд) получаются выходные импульсы первого разряда. Процесс формирования импульсов напряжения второго разряда не отличается от описанного. Порядок работы старших разрядов счетчика (триггеров 5-10) аналогичен обычному порядку работы счетчиков.

Формула изобретения

Двоичный счетчик импульсов, содержащий последовательно включенные триггеры, разделенные на группы младших и старших разрядов, блок сквозного переноса сигналов старщих разрядов, состоящий из многовходовых логических элементов «И, входы каждого из которых подключены соответственно к выходам предыдущих триггеров, а выходы - к

входу последующего триггера, отличающийся тем, что, с целью повышения быстродействия, в него введен блок формирования сигналов младших разрядов счетчика, состоящий из логических элементов «И, попарно

подключенных к входам логических элементов «ИЛИ, и инверторов, входы которых соединены с выходами триггеров соответствующих младших разрядов счетчика, а выходы соединены с входами соответствующих логических элементов «И блока формирования сигналов младших разрядов счетчика, причем остальные входы логических элементов «И блока формирования сигналов младших разрядов счетчика соединены с выходами соответствующих триггеров младших разрядов счетчика, при этом к входам каждого из триггеров младших разрядов подключены попарно двухвходовые логические элементы «И, входы которых соединены с соответствующими выходами предыдущих триггеров и входом счетчика.

| название | год | авторы | номер документа |

|---|---|---|---|

| МНОГОРАЗРЯДНЫЙ СЧЕТЧИК ИМПУЛЬСОВ | 1972 |

|

SU351325A1 |

| Устройство управления однофазным инвертором с широтно-импульсным модулированием | 1975 |

|

SU692060A1 |

| Способ следящего аналого-цифрового преобразования и устройство для его осуществления | 1983 |

|

SU1229954A1 |

| Измеритель временных интервалов | 1979 |

|

SU809037A1 |

| Цифровой частотомер | 2019 |

|

RU2730047C1 |

| Цифровой стробоскользиметр и вычитающее устройство с цифровой индикацией | 1983 |

|

SU1257523A1 |

| Устройство проверки счетчиков | 1978 |

|

SU752811A1 |

| СИНХРОННЫЙ ДЕЛИТЕЛЬ ЧАСТОТЫ | 1992 |

|

RU2037957C1 |

| ТРОИЧНОЕ СЧЕТНОЕ УСТРОЙСТВО | 2002 |

|

RU2231921C2 |

| МНОГОРАЗРЯДНЫЙ УПРАВЛЯЕМЫЙ ДЕЛИТЕЛЬ ЧАСТОТЫ | 1996 |

|

RU2119248C1 |

Авторы

Даты

1976-09-30—Публикация

1974-10-15—Подача